Professional Documents

Culture Documents

Assignment6 Solution 3rd Edition

Uploaded by

Raffi SkCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Assignment6 Solution 3rd Edition

Uploaded by

Raffi SkCopyright:

Available Formats

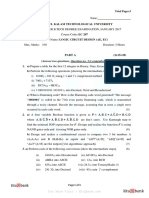

ECE-223, Solutions for Assignment #6

Digital Design, M. Mano, 3rd Edition, Chapter 5

5.2) Construct a JK flip-flop using a D Flip-flop, a 2-to-1 line multiplexer and an inverter.

5.4) A PN flip-flop has four operations: clear to 0, no change, complement, and set to 1, when inputs P and N are 00, 01, 10, and 11, respectively. a) b) c) d) Tabulate the characteristic table. Derive the characteristic equation. Tabulate the excitation table. Show how the PN flip-flop can be converted to a D flip-flop.

a) P 0 0 1 1

b) N 0 1 0 1 Q(t+1) 0 Q(t) Q(t) 1

Page: 1

Q(t+1) = PQ + NQ

c) Q(t) 0 0 1 1 Q(t+1) 0 1 0 1 P 0 1 X X N X X 0 1

d) By connecting P and N together. Q(t+1) = DQ + DQ = D

5.6) A sequential circuit with two D Flip-Flops, A and B; two inputs, x and y; and one output, z, is specified by the following next-state and output equations: A(t+1) = xy + xA B(t+1) = xB + xA z=B a) Draw the logic diagram of the circuit. b) List the state table for the sequential circuit. c) Draw the corresponding state diagram. a)

Page: 2

b) Present State A B 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 Inputs x 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 y 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Next State A B 0 0 1 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 1 1 Output z 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

c)

Page: 3

5.12) Reduce the number of states in the following state table and tabulate the reduced state table. Present State a b c d e f g h Next State x =0 f d f g d f g g x =1 b c e a c b h a x =0 0 0 0 1 0 1 0 1 Output x =1 0 0 0 0 0 1 1 0

Present State a b d f g

Next State x =0 f d g f g x =1 b a a b d x =0 0 0 1 1 0

Output x =1 0 0 0 1 1

5-16) Design a sequential circuit with two D Flip-Flops, A and B, and one input x. When x = 0, then the state of the circuit remains the same. When x =1, the circuit goes through the state transitions from 00 to 01 to 11 to 10 back to 00, and repeats.

Present State AB 00 00 01 01 10 10 11 11

Input x 0 1 0 1 0 1 0 1

Nest State AB 00 01 01 11 10 00 11 10

Page: 4

5-17) Design a one input, one output serial 2s complimenter. The circuit accepts a string of bits from the input and generates the 2s compliment at the output. The circuit can be reset asynchronously to start and end the operation. Solution: The output is 0 for all 0 inputs until the first 1 occurs at which time, the output is 1. Thereafter, the output is the complement of the input.

Page: 5

The state diagram has two states State 0 : Output = Input State1 : Output = Complement of input PS A 0 0 1 1 Inp. NS Out x A y 0 0 0 1 1 1 0 1 1 1 1 0

DA= A + x y=Ax

Page: 6

5-19) A sequential circuit has three flip-flops A, B, C; one input x; and one output, y. The state diagram is shown in Fig.P5-19. The circuit is to be designed by treating the unused states as dont-care conditions. Analyze the circuit obtained from the design to determine the effect of the unused states.

a) Use D flip-flops in the design b) Use J-K flip-flops in the design

Fig.P5-19

Page: 7

a)

A 0 0 0 0 0 0 0 0 1 1

Present State B 0 0 0 0 1 1 1 1 0 0

C 0 0 1 1 0 0 1 1 0 0

Input x 0 1 0 1 0 1 0 1 0 1

A 0 1 0 1 0 0 0 0 0 0

Next State B 1 0 0 0 1 0 0 1 1 1

C 1 0 1 0 0 0 1 0 0 1

Output y 0 1 0 1 0 1 0 1 0 0

Page: 8

b) Use JK flip-flops: JA 0 1 0 1 0 0 0 0 X X JA = Bx KA =1 KA X X X X X X X X 1 1 JB = A+ Cx KB =Cx + Cx JB 1 0 0 0 X X X X 1 1 KB X X X X 0 1 1 0 X X JC 1 0 X X 0 0 X X 0 1 KC X X 0 1 X X 0 1 X X

JC = Ax + ABx KC =x

Self-correction because KA =1

Page: 9

5-20) Design the sequential circuit specified by the state diagram of Fig. 5-19 using T flip-flops.

Fig. 5-19 From State table (Table 5-4 from Digital Design, M. Mano, 3rd Edition, pp.186) TA (A, B, x) = ( 2, 3, 6) TB (A, B, x) = ( 0, 3, 4, 6)

TB = AB+Bx 10

TA = Ax+Bx+ABx Page:

You might also like

- A Synchronous Synchronous Reset Design in ASICDocument38 pagesA Synchronous Synchronous Reset Design in ASICadaiadaiNo ratings yet

- Sequential CircuitDocument51 pagesSequential CircuitDamodar Telu100% (1)

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Sharp MX-4070NDocument471 pagesSharp MX-4070NAllen Walker100% (2)

- PRBS GeneratorDocument9 pagesPRBS GeneratorrafieeeNo ratings yet

- Design and Construction of Hybrid Arc Welding MachineDocument15 pagesDesign and Construction of Hybrid Arc Welding MachinePascu AurelNo ratings yet

- Digital Design ExamplesDocument29 pagesDigital Design ExampleshumnaharoonNo ratings yet

- SV-iC5 User ManualDocument15 pagesSV-iC5 User ManualChristopher T. Caniedo100% (2)

- FTA1100J Diesel Engine Fire Pump Controllers Product DescriptionDocument2 pagesFTA1100J Diesel Engine Fire Pump Controllers Product Descriptionrahu2260100% (1)

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsFrom EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNo ratings yet

- DD Co QuestionsDocument8 pagesDD Co QuestionsRohit M ANo ratings yet

- HW 06Document4 pagesHW 06Kevin KarthikNo ratings yet

- Digital System - Week 5 TutorialDocument9 pagesDigital System - Week 5 TutorialRetheshNo ratings yet

- ECS 154A Midterm KeyDocument4 pagesECS 154A Midterm KeyTiffany LeeNo ratings yet

- Chapter 5 Synchronous Sequential CircuitDocument32 pagesChapter 5 Synchronous Sequential CircuitSenthur PriyaNo ratings yet

- C5 ProbDocument4 pagesC5 ProbMihir Kumar MechNo ratings yet

- CompoundDocument4 pagesCompounduscrNo ratings yet

- Question Bank M Tech 2ND Sem Batch 2018Document31 pagesQuestion Bank M Tech 2ND Sem Batch 2018king khanNo ratings yet

- Sequential Circuit DesignDocument28 pagesSequential Circuit DesignNiranda PereraNo ratings yet

- Sequential Circuit Design Sequence RecognizerDocument4 pagesSequential Circuit Design Sequence RecognizerKhurram SamiNo ratings yet

- Exo StudentDocument3 pagesExo StudentHassanNo ratings yet

- ITI1100A Assignment 5 - Sequential Circuit Problems and SolutionsDocument3 pagesITI1100A Assignment 5 - Sequential Circuit Problems and SolutionssdfsdfNo ratings yet

- Assignment Sequential CircuitsDocument2 pagesAssignment Sequential CircuitsPavan SaiNo ratings yet

- Detailed Solutions A-09 JUNE 2003 Detailed Solutions A - 09 JUNE 2003Document22 pagesDetailed Solutions A-09 JUNE 2003 Detailed Solutions A - 09 JUNE 2003Harold WilsonNo ratings yet

- COEN 3137 Advanced Logic Circuits Design Lab 7 Synchronous Binary CountersDocument19 pagesCOEN 3137 Advanced Logic Circuits Design Lab 7 Synchronous Binary Countersjocansino4496No ratings yet

- EE 110 Practice Problems For Final Exam: SolutionsDocument7 pagesEE 110 Practice Problems For Final Exam: Solutionsmurthy237No ratings yet

- Question Bank Chapter 6 and Chapter 7Document5 pagesQuestion Bank Chapter 6 and Chapter 7nooneNo ratings yet

- Ch5 - 4 Design of Sequential CircuitsDocument46 pagesCh5 - 4 Design of Sequential CircuitsMariam ElnourNo ratings yet

- University of Gondar Institute of TechnologyDocument59 pagesUniversity of Gondar Institute of TechnologyamareNo ratings yet

- RR210204 Switching Theory & Logic DesignDocument2 pagesRR210204 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- 19EC303 QP RepositoryDocument4 pages19EC303 QP RepositoryssfjvhsffsNo ratings yet

- ECE 2411 Assignment 2Document2 pagesECE 2411 Assignment 2Bryan CastineNo ratings yet

- Analysis and Design of Sequential Circuits: Examples: COSC3410Document36 pagesAnalysis and Design of Sequential Circuits: Examples: COSC3410markolzNo ratings yet

- Ade Unit - 4 QBDocument17 pagesAde Unit - 4 QBNithya SNo ratings yet

- Synchronous Sequential Circuit Problems: Problem # 1Document6 pagesSynchronous Sequential Circuit Problems: Problem # 1Anonymous AFFiZnNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument8 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshNo ratings yet

- ELE2120 Digital Circuits and Systems: Tutorial Note 9Document25 pagesELE2120 Digital Circuits and Systems: Tutorial Note 9Nelson Ubaldo Quispe MNo ratings yet

- CSCI350-S22-Assignment 4Document1 pageCSCI350-S22-Assignment 4Atharva TemkarNo ratings yet

- Sequential CircuitsDocument11 pagesSequential CircuitsUday DesirajNo ratings yet

- EC207 Logic Circuit Design Exam QuestionsDocument3 pagesEC207 Logic Circuit Design Exam QuestionsABHILESH G KNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- Rajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterDocument37 pagesRajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterAmrita VenkitaramaniNo ratings yet

- State Transition Diagrams and Sequential Circuit DesignDocument6 pagesState Transition Diagrams and Sequential Circuit DesignPrafull BNo ratings yet

- Design Sequential Circuits in 4 StepsDocument4 pagesDesign Sequential Circuits in 4 StepsDhanwanth JPNo ratings yet

- 15es3gcdec Dec 2017Document4 pages15es3gcdec Dec 2017MAHESHA GNo ratings yet

- ITBP205 Digital Design and Computer Organization Unit 9 Sequential Circuits DesignDocument21 pagesITBP205 Digital Design and Computer Organization Unit 9 Sequential Circuits DesignReem Ashraf0% (1)

- FSM 1Document145 pagesFSM 1Sriharsha EnjapuriNo ratings yet

- TutorialDocument2 pagesTutorialBeat Boy RkayNo ratings yet

- D Flip-Flop JK Flip-Flop SR-latch T Flip-Flop D Q J K Q S R Q T Q 0 0 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1Document4 pagesD Flip-Flop JK Flip-Flop SR-latch T Flip-Flop D Q J K Q S R Q T Q 0 0 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1Mộc SầuNo ratings yet

- Counter DesignDocument7 pagesCounter Designsujaganesan2009No ratings yet

- EE El 213 Digital Circuits and Systems Assignment 4Document3 pagesEE El 213 Digital Circuits and Systems Assignment 4Dhruv Paul100% (1)

- Digital Logic by NODIADocument49 pagesDigital Logic by NODIAJyoti GoswamiNo ratings yet

- Digital Logic Design K-map worksheetDocument4 pagesDigital Logic Design K-map worksheetYeshiwas KefaleNo ratings yet

- Digital ElectronicsDocument33 pagesDigital ElectronicsNiranjanaNo ratings yet

- Lect19 Sequential Logic Part-2Document21 pagesLect19 Sequential Logic Part-2ramulakshmanan12No ratings yet

- Extra Tutorial AnsDocument19 pagesExtra Tutorial Ansمحمد النقيبNo ratings yet

- Exam 2 Review: Logic Implementation and Timing AnalysisDocument40 pagesExam 2 Review: Logic Implementation and Timing AnalysisBruno SilvaNo ratings yet

- Analysis and Design of Sequential Logic CircuitsDocument115 pagesAnalysis and Design of Sequential Logic CircuitsQuoc Khanh PhamNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- (WWW - Entrance Exam - Net) Electronics Based CompaniesDocument11 pages(WWW - Entrance Exam - Net) Electronics Based CompaniesPrativendra PatelNo ratings yet

- Vlsi Lab DocumentDocument18 pagesVlsi Lab DocumentRaffi SkNo ratings yet

- Compile Test CodesDocument24 pagesCompile Test CodesRaffi SkNo ratings yet

- TermsDocument1 pageTermsRaffi SkNo ratings yet

- Lab 1Document24 pagesLab 1Raffi SkNo ratings yet

- VgaDocument7 pagesVgafenutfenutNo ratings yet

- Lab 1Document24 pagesLab 1Raffi SkNo ratings yet

- Wipro 3Document11 pagesWipro 3akmalrahmanNo ratings yet

- Verilog modules for 4-bit ALU, register, RAM and instruction decoderDocument6 pagesVerilog modules for 4-bit ALU, register, RAM and instruction decoderRaffi SkNo ratings yet

- Chp8 PDFDocument15 pagesChp8 PDFRaffi SkNo ratings yet

- (WWW - Entrance-Exam - Net) - Wipro Sample Paper 2 PDFDocument0 pages(WWW - Entrance-Exam - Net) - Wipro Sample Paper 2 PDFRaffi SkNo ratings yet

- Cadence 5Document6 pagesCadence 5Raffi SkNo ratings yet

- DM7474 PDFDocument5 pagesDM7474 PDFRaffi SkNo ratings yet

- Written Test Pattern Is Verbal 15 Quetions Quanti. Cum Reasoing 15 Questions Technical 20 QuestionsDocument3 pagesWritten Test Pattern Is Verbal 15 Quetions Quanti. Cum Reasoing 15 Questions Technical 20 QuestionsRaffi SkNo ratings yet

- Chapter 4: Modules and Ports: AnswerDocument2 pagesChapter 4: Modules and Ports: AnswerRaffi SkNo ratings yet

- 2 Design Specification For 4 Bit ProcessorDocument4 pages2 Design Specification For 4 Bit ProcessorAjay G BellamNo ratings yet

- OopDocument67 pagesOopRaffi SkNo ratings yet

- 04041915Document9 pages04041915Raffi SkNo ratings yet

- 2 Design Specification For 4 Bit ProcessorDocument4 pages2 Design Specification For 4 Bit ProcessorAjay G BellamNo ratings yet

- Exercise 6 - Sequential Circuit Design: 60-265 Computer Architecture I: Digital Design Fall 2012Document5 pagesExercise 6 - Sequential Circuit Design: 60-265 Computer Architecture I: Digital Design Fall 2012Raffi SkNo ratings yet

- 06242064Document6 pages06242064Raffi SkNo ratings yet

- TCS Talent Test InstructionsDocument17 pagesTCS Talent Test InstructionsRaffi SkNo ratings yet

- Adc0809-N Data SheetDocument19 pagesAdc0809-N Data SheetJesus BernalNo ratings yet

- Chapter 6. Dataflow Modeling: 6.7 ExercisesDocument8 pagesChapter 6. Dataflow Modeling: 6.7 ExercisesRaffi SkNo ratings yet

- New Text DocumentDocument4 pagesNew Text DocumentRaffi SkNo ratings yet

- Synonyms & AntonymsDocument30 pagesSynonyms & AntonymsMohan100% (2)

- A Blind Digital Watermarking Algorithm Based On Wavelet TransformDocument4 pagesA Blind Digital Watermarking Algorithm Based On Wavelet TransformShivangi TandonNo ratings yet

- A Greedy Algorithm For Wire Length OptimizationDocument4 pagesA Greedy Algorithm For Wire Length OptimizationRaffi SkNo ratings yet

- Datasheet - HK lt1963-33 349763Document20 pagesDatasheet - HK lt1963-33 349763Duy LongNo ratings yet

- Powercommand Digital Master Control: FeaturesDocument12 pagesPowercommand Digital Master Control: FeaturesthainarimeNo ratings yet

- SSC Unit - I Lecture 0Document24 pagesSSC Unit - I Lecture 0Girish Shankar MishraNo ratings yet

- Phy 108 Exp 2 Wheaston BridgeDocument7 pagesPhy 108 Exp 2 Wheaston BridgeChukwunomso UnaoguNo ratings yet

- Manual LBEDocument117 pagesManual LBEDaniel Leonardo Palomino CamaNo ratings yet

- Sitescan Series Digital Flaw DetectorsDocument6 pagesSitescan Series Digital Flaw DetectorsAkhilNo ratings yet

- Zuper 400Document4 pagesZuper 400Md Kaleem100% (1)

- ZTE CDROM, USB devices and system driversDocument6 pagesZTE CDROM, USB devices and system driversYhonjaiverGuzmanNo ratings yet

- 3NC52-0N F3YP22-0P F3YP24-0P F3YP28-0P一般规格(14年 第6版)Document42 pages3NC52-0N F3YP22-0P F3YP24-0P F3YP28-0P一般规格(14年 第6版)赵先生No ratings yet

- 4208u 3-09 Rev A PDFDocument4 pages4208u 3-09 Rev A PDFgarrigan12No ratings yet

- Ban MCQDocument8 pagesBan MCQM KISHORE,CSE(19-23) Vel Tech, ChennaiNo ratings yet

- STR5A464x Series Data Sheet: For Non-Isolated Off-Line PWM Controllers With Integrated Power MOSFETDocument23 pagesSTR5A464x Series Data Sheet: For Non-Isolated Off-Line PWM Controllers With Integrated Power MOSFETHeru susantoNo ratings yet

- Aif - PFC TRN Rev12 1484268447 TechrefDocument40 pagesAif - PFC TRN Rev12 1484268447 TechrefmigsantNo ratings yet

- NDT UNIT 3-Complete NotesDocument59 pagesNDT UNIT 3-Complete Notesshriman100% (1)

- IO - Link + AS - Interface PDFDocument12 pagesIO - Link + AS - Interface PDFtadNo ratings yet

- Brosur EMALED 200 NewDocument2 pagesBrosur EMALED 200 NewAde DahliaNo ratings yet

- Microwave InspectionDocument10 pagesMicrowave InspectionZaid TariqNo ratings yet

- Major Components of the A4000D DistillerDocument5 pagesMajor Components of the A4000D DistillerYến HuỳnhNo ratings yet

- Monitor SonyDocument30 pagesMonitor SonyYoelNo ratings yet

- Zed-F9T: U-Blox F9 High Accuracy Timing ModuleDocument23 pagesZed-F9T: U-Blox F9 High Accuracy Timing Modulekar karNo ratings yet

- RMU Shop DrawingsDocument12 pagesRMU Shop Drawingsahmed saadNo ratings yet

- Design of High Performance Linear Brushless DC Motor With Ironless CoreDocument6 pagesDesign of High Performance Linear Brushless DC Motor With Ironless CoreShubhzsNo ratings yet

- URIT-50 Service Manual Main BodyDocument11 pagesURIT-50 Service Manual Main BodyJerry MnguniNo ratings yet

- Master Thesis - Daniel Sanz AusinDocument74 pagesMaster Thesis - Daniel Sanz Ausinesilva2021No ratings yet

- 4-Testing Differential ProtectionDocument36 pages4-Testing Differential ProtectionHassan TahaNo ratings yet

- B&K Short Form Catalog (1973)Document44 pagesB&K Short Form Catalog (1973)Francesco Violi100% (2)