Professional Documents

Culture Documents

WT7514 PDF

Uploaded by

le5100kwOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

WT7514 PDF

Uploaded by

le5100kwCopyright:

Available Formats

|____ |____ |____ |____

Weltrend Semiconductor, Inc.

,|______ ,|______ ,|______ ,|______4 4 4 4 _ __ _ _ __ _

2E, No. 24, Industry E. 9

th

RD., Science-Based Industrial Park, Hsin-Chu, Taiwan

TEL:886-3-5780241 EAX:886-3-5794278.5770419

Email:supportweltrend.com.tw

Data Sheet

REV. 1.30

ApriI 12, 2004

The information in this document is subject to change without notice.

WeItrend Semiconductor, Inc. AII Rights Reserved.

This datasheet has been downloaded fromhttp://www.digchip.comat this page

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 2

GENERAL DESCRIPTION

The WT7514L is a pulsewidth modulation (PWM) control circuit with complete protection circuits for

used in the SMPS (Switched Mode Power Supply). It contains various functions, which are Over Voltage

Protection, Under Voltage Protection, Power Good Output (PGO), Remote On/Off control and etc. It can

minimize external components of switching power supply systems in personal computer.

Over Voltage Protection (OVP) monitors 3.3V, 5V, 12V and PT input voltage level. Under Voltage

Protection (UVP) monitors 3.3V, 5V and 12V input voltage level. Power Good Output monitors the

voltage level of power supply.

FEATURES

Complete PWM Control and Protection Circuitry

Over Voltage Protection for 3.3V / 5V / 12V / PT

Under Voltage Protection for 3.3V / 5V / 12V

Various PG Time Delay by TPG

Power Good Output is Open Drain Output

PWM Control Output are Open Drain Output

250 mS Time Delay for UVP

Remote ON/OFF function Debounce Time

Power Good Output with Hysteresis

16Pin Dual Inline Package

PIN CONFIGURATION

Ordering Number Package Type

WT7514LN160WT DIP 16

V33

V5

V12

PT

GND

CT

C1

C2

VADJ

OPNEGIN

OPOUT

VCC

DET

PG

TPG

REM

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

7514L

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 3

PIN DESCRIPTION

Pin No. Pin Name TYPE FUNCTION

1 V33 I OVP/UVP INPUT EOR 3.3V

2 V5 I OVP/UVP INPUT EOR 5V

3 V12 I OVP/UVP INPUT EOR 12V

4 PT I EXTRA OVP INPUT PROTECTION

5 GND P GROUND

6 CT --- OSCIILATION EREQUENCY BY SETTING CAP

7 C1 O OUTPUT 1

8 C2 O OUTPUT 2

9 REM I REMOTE ON/OEE INPUT. IE REMLOW THAT MEANS

THE MAIN SMPS IS OPERATION. WHEN REMHIGH,

THE MAIN SMPS IS TURNED-OEE.

10 TPG

--- POWER GOOD DELAY TIME

11 PG O POWER GOOD SIGNAL. IE PGHIGH MEANS 'POWER

GOOD AND PGLOW MEANS 'POWER EAIL.

12 DET

I POWER GOOD SIGNAL INPUT

13 VCC P SUPPLY VOLTAGE

14 OPOUT O OP COMPENSATION OUTPUT

15 OPNEGIN I OP COMPENSATION NEGATIVE INPUT

16 VADJ I VOLTAGE ADJUST

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 4

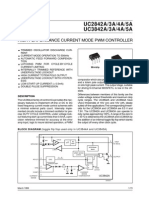

BLOCK DIAGRAM

ABSOLUTE MAXIMUM RATINGS, VCC=5.5V

CHARACTERISTICS SYMBOL VALUE Unit

Supply voltage VCC 5.5 V

Drain output voltage Vcc1, Vcc2 5.5 V

Drain output current Icc1, Icc2 200 mA

Power dissipation Pd 200 mW

Operating temperature Topr -10 ~ 70

Storage temperature Tstg -65 ~ 150

C

D Q

QN

R

S Q

QN

+

-

+

-

+

-

+

-

+

-

+

-

+

-

+

-

+

-

+

-

+

-

+

-

V33

V5

V12

PT

QOUT

TPG

REM

REMONF

REMON

PG

DET

C1

CT

VADJ

OPNEGIN

C2

OPOUT

DEAD TIME CONTROLLER

DETCMP

PWMCMP

PWM CONTROL

CLR

IN

250ms delay

OUT

5K

[11]

OSC

CLR

0.4V

0.625V

2.45V

ERROR AMP

[16]

[15]

4.5mS

Delay

36mS

Delay

[14]

[6]

[12]

[9]

0.625V

[4]

[3]

[2]

[1]

OVP

UVP

1.25V

OV

OV

OV

OV

UV

UV

UV

[8]

[7]

[10]

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 5

ELECTRICALCHARACTERISTICS,

CHARACTERISTICS SYMBOL TEST CONDITION Min. Typ. Max. Unit

DEAD TIME CONTROL SECTION

ZERO DUTY CYCLE 3.0 3.3 INPUT THRESHOLD VOLTAGE Vthdt

MAX. DUTY CYCLE 0.1

V

ERROR AMP SECTION

CLOSE LOOP VOLTAGE GAIN 0.5V ~ 3.5V 65 dB

CROSS OVER POINT 0dB 320 KHZ

OPNEG BIAS VOLTAGE OPNEG OPEN 2.38 2.45 2.52 V

OUTPUT SECTION

OUTPUT SATURATION VOLTAGE Vdssat Id200mA 1.1 1.3 V

DRAIN OEE-STATE CURRENT Idoff VccVdVs0V 2 10 uA

RISING TIME Tr 100 200 ns

EALLING TIME Tf 50 200 ns

PROTECTION SECTION

V33 3.8 4.1 4.3 V

V5 5.8 6.2 6.6 V

V12 4.41 4.64 4.90 V

OVER VOLTAGE PROTECTION

OVP

PT 1.2 1.25 1.3 V

V33 1.78 1.98 2.18 V

V5 2.70 3.00 3.30 V

UNDER VOLTAGE PROTECTION

UVP

V12 2.11 2.37 2.63 V

UVP DISABLE VOLTAGE PT 0.55 0.62 0.68 V

UVP DELAY TIME Td.uvp 100 250 500 ms

REMOTE ON/OEE SECTION

REM HIGH INPUT VOLTAGE Vremh 2.0 V

REM LOW INPUT VOLTAGE Vreml 0.8 V

REM PULL HIGH VOLTAGE Vremo 2.0 5.25 V

REM DELAY TIME Trem 30 36 42 ms

REM OEE DELAY TIME Toff 3.5 4.5 5.5 ms

POWER GOOD SECTION

DETECTING INPUT VOLTAGE Vdet 0.55 0.62 0.68 V

PG OUTPUT PULLUP RESISTOR Rpup, pg 5 K

PG OUTPUT LOAD RESISTOR Rpg 0.5 1 2 K

CHARGING CURRENT EOR TPG Ichg.tpg 30 uA

PG DELAY TIME Td.pg C2.2uE 100 250 500 ms

OUTPUT SATURATION VOLTAGE Vsat.pg Ipg10mA 0.2 0.4 V

TOTAL DEVICE

STANDBY SUPPLY CURRENT Icc 10 20 mA

OSCILLATION SECTION

OSCILLATION EREQUENCY Eosc CT2200P 50 60 70 KHZ

EREQ. CHANGE WITH TEMP. Eosc/T CT2200p 2 %

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 6

APPLICATION NOTE

1. Input impedance:

Pin No. Pin Name Input impedance

1 V33 52K

2 V5 81K

3 V12 52K

4 PT 279K(VGS14.12V)

59.8K(VGS20.88V)

(VCC5V, PT0.88V)

2. Operation Erequency:

The period oI the sawtootth is T

OSC

:

I

CHARGE

(1.25V / 5.8 K) * 2 430uA

T

OSC

(3.3V * CT) / I

CHARGE

(3.3V * 2200pE) / 430uA

E

OSC

1 / T

OSC

59 KHZ

Eor Push-Pull applications:

E

PUSH-PULL

1 / 2 T

OSC

V33

52K

V5

81K

V12

52K

VCC

NMOS1

NMOS2

VGS1

VGS2

PT

SAWTOOTH OSC.

VCC

I

CT

CT

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 7

3. REMOTE ON/OEE

4. Under Voltage Protection Delay Time

5. Pulse Width Modulation Block

The output pulse width modulation is generated by comparision oI the sawtooth

waveIorm Irom the capacitor C

T

to the Ieedback oI the voltage.

ThereIore, an increase in Ieedback control signal amplitude cause a linear decrease oI the

output pulse width. The timing diagram is shown as below:

CT

FF-Q

FF-CLK

C2

C1

FF-QN

DTC

PWM OUT

REM

REMONF

REMON

trem trem

toff toff

REM

REMONF

UVP

trem

td,uvp

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 8

6. The Iunction oI 'PT: (DeIault Iloating V

PT

0.8V)

This signal is prepared Ior extra Over Voltage Protection Input (V

PT

~ 1.25V) or another

Disable Under Voltage Protection Iunction (V

PT

0.62V)

7. ReIerence Application Ciruit:

V33

V5

V12

PT VCC

PG

REM

VCC

C7

C6

C5

C4

C3

C2

R22 R21

R11

R10

R9

R8

R6

R5

2.2uF

10

9 8

7

6

5

4

3

2

R7

VR1

R3 R4

R1 C1

2200pF

VCC

DET

PG

REM

TPG

C2

C1

CT

GND

PT

V12

V5

V33

11

12

13

OPOUT

14

16

15

OPNEGlN

VADJ

1

WT7514L

Data Sheet Rev. 1.30

Weltrend Semiconductor, Inc.

Page 9

MECHANICAL INFORMATION

PLASTIC DUAL-IN-LINE PACKAGE

NOTE 1All linear dimensions are in inchesmillimeters.

NOTE 2This drawing is subject to change without notice.

NOTE 3Falls within JEDEC MS001

You might also like

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Guidance On Lineside Signal Aspect and Indication RequirementsDocument83 pagesGuidance On Lineside Signal Aspect and Indication Requirementsle5100kw100% (1)

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- Nikon D7000 User's Manual (English) PrintableDocument348 pagesNikon D7000 User's Manual (English) PrintablegoldfiresNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Current Mode PWM Controller: Features DescriptionDocument9 pagesCurrent Mode PWM Controller: Features DescriptionJozo ĆurčićNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Data SheetDocument7 pagesData Sheetitamar_123No ratings yet

- WT7520Document9 pagesWT7520Inajá FerreiraNo ratings yet

- 4-Channel Secondary Monitoring IC with OCP and OTPDocument11 pages4-Channel Secondary Monitoring IC with OCP and OTPseyyedali2006No ratings yet

- Uc284xa Uc384xaDocument16 pagesUc284xa Uc384xayusufwpNo ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- Power Suply Mac WT7515Document11 pagesPower Suply Mac WT7515Wade DyerNo ratings yet

- Datasheet sg6105dDocument13 pagesDatasheet sg6105dCartman SantosNo ratings yet

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 pagesUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceNo ratings yet

- STP9NK65ZFPDocument16 pagesSTP9NK65ZFPJacson FagundesNo ratings yet

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiNo ratings yet

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNo ratings yet

- PM 150 CSD 120Document7 pagesPM 150 CSD 120elecompinnNo ratings yet

- Single Bilateral Switch: Order CodesDocument11 pagesSingle Bilateral Switch: Order CodesGaryTechNo ratings yet

- Stp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii MosfetDocument11 pagesStp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii Mosfetmiguel angel jaramilloNo ratings yet

- Fet 60NF06Document9 pagesFet 60NF06Anh Nguyễn HoàngNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- Uc3842 Monitor Power Supply Regulator IcDocument7 pagesUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- Uc 3845Document23 pagesUc 3845Bahram RN100% (1)

- Apl 5336Document20 pagesApl 5336FlavianoSilvaNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- Datasheet Fairchild UC3843Document7 pagesDatasheet Fairchild UC3843Tina JohnsonNo ratings yet

- Datasheet.... Schmitt TriggerDocument22 pagesDatasheet.... Schmitt TriggerIc CruiseNo ratings yet

- Sn7414 Schmitt TriggerDocument13 pagesSn7414 Schmitt TriggerFaazil FairoozNo ratings yet

- Viper 53Document24 pagesViper 53Cadena CesarNo ratings yet

- 4-Channel Secondary Monitoring IC DatasheetDocument11 pages4-Channel Secondary Monitoring IC DatasheetIdelbrando RochaNo ratings yet

- 74LS14Document16 pages74LS14Daniela S Arroba CNo ratings yet

- Eds GMB51001Document11 pagesEds GMB51001negrusrlNo ratings yet

- D D D D D D D D D: DescriptionDocument18 pagesD D D D D D D D D: DescriptionNalin Lochan GuptaNo ratings yet

- IC 3842 para FonteDocument8 pagesIC 3842 para FonteTomNedscNo ratings yet

- Fan 7313Document11 pagesFan 7313KathafiNo ratings yet

- Apl 5913Document19 pagesApl 5913Aldemir Fernando Battaglia100% (1)

- 74HC374Document13 pages74HC374jnax101No ratings yet

- FaDocument20 pagesFaVishwanath ShervegarNo ratings yet

- Datasheet 53315Document30 pagesDatasheet 53315Bladimir AngamarcaNo ratings yet

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliNo ratings yet

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocument7 pagesUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitEnica LiviaNo ratings yet

- Single Ended Active Clamp/Reset PWM: Features DescriptionDocument16 pagesSingle Ended Active Clamp/Reset PWM: Features Descriptioncatsoithahuong84No ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFperro sNo ratings yet

- CPT Technical Specification for 17-inch TFT-LCD ModuleDocument21 pagesCPT Technical Specification for 17-inch TFT-LCD Modulem_tOmNo ratings yet

- WT7527 - v1.20 POWER GOOD CIRCUITDocument12 pagesWT7527 - v1.20 POWER GOOD CIRCUITLuis PereiraNo ratings yet

- 4-Channel Secondary Monitoring IC With 4-Channel OCP and An Additional OTPDocument11 pages4-Channel Secondary Monitoring IC With 4-Channel OCP and An Additional OTPDanniel Martin0% (1)

- STRW6252Document15 pagesSTRW6252miltoncgNo ratings yet

- European Medicines Agency Questions & Answers On Signal ManagementDocument9 pagesEuropean Medicines Agency Questions & Answers On Signal Managementle5100kwNo ratings yet

- Do Canadian Railroad Signals Make Sense 5 PDFDocument55 pagesDo Canadian Railroad Signals Make Sense 5 PDFle5100kwNo ratings yet

- ASPeCT Unambiguous Sine BOC Acquisition Tracking Technique For Navigation ApplicationsDocument13 pagesASPeCT Unambiguous Sine BOC Acquisition Tracking Technique For Navigation Applicationsle5100kwNo ratings yet

- CRN SD 001 Signalling Design Principles Signals v11 Apl 2016Document84 pagesCRN SD 001 Signalling Design Principles Signals v11 Apl 2016le5100kwNo ratings yet

- BNSF Railway - SIGNAL ASPECTS AND INDICATIONS April 7, 2010Document2 pagesBNSF Railway - SIGNAL ASPECTS AND INDICATIONS April 7, 2010le5100kwNo ratings yet

- Aspect Sequences With High SpeedTurnoutsDocument9 pagesAspect Sequences With High SpeedTurnoutsle5100kwNo ratings yet

- Traffic Signal Pole Handbook For HeliosDocument37 pagesTraffic Signal Pole Handbook For Heliosle5100kwNo ratings yet

- Lineside Signal Aspect and Indication RequirementsDocument37 pagesLineside Signal Aspect and Indication Requirementsle5100kwNo ratings yet

- Fujifilm Xt1 Manual enDocument152 pagesFujifilm Xt1 Manual encoho_hcNo ratings yet

- Railway Signal Standards Revised June 2007Document6 pagesRailway Signal Standards Revised June 2007mkashkooli_scribdNo ratings yet

- CRN SD 011 Signalling Design Principles Approach Locking v11 Apl 2016Document8 pagesCRN SD 011 Signalling Design Principles Approach Locking v11 Apl 2016le5100kwNo ratings yet

- PBH 2000 ReDocument2 pagesPBH 2000 Rele5100kwNo ratings yet

- Box2D v2.3.0 User ManualDocument69 pagesBox2D v2.3.0 User ManualTonyR123No ratings yet

- Iphone User GuideDocument184 pagesIphone User GuideflaxehyttNo ratings yet

- HD Hero Um Eng 110110Document2 pagesHD Hero Um Eng 110110panosscribdNo ratings yet

- Din. Digital Temperature Controller: Ttm-000 Series User'S Manual Operation Flow and Setting MenuDocument1 pageDin. Digital Temperature Controller: Ttm-000 Series User'S Manual Operation Flow and Setting MenuDennis ArhinNo ratings yet

- STP1806 PDFDocument9 pagesSTP1806 PDFle5100kwNo ratings yet

- At2005b Ate PDFDocument7 pagesAt2005b Ate PDFle5100kwNo ratings yet

- Din. Digital Temperature Controller: Ttm-000 Series User'S Manual Operation Flow and Setting MenuDocument1 pageDin. Digital Temperature Controller: Ttm-000 Series User'S Manual Operation Flow and Setting MenuDennis ArhinNo ratings yet

- Din. Digital Temperature Controller: Ttm-000 Series User'S Manual Operation Flow and Setting MenuDocument1 pageDin. Digital Temperature Controller: Ttm-000 Series User'S Manual Operation Flow and Setting MenuDennis ArhinNo ratings yet