Professional Documents

Culture Documents

Design Logic Gates VHDL

Uploaded by

Prem Prakash0 ratings0% found this document useful (0 votes)

13 views6 pagesThe document describes an experiment to design various logical gates using VHDL. The aim was to create VHDL code for AND, OR, NAND, NOR, XOR, XNOR, and NOT gates. VHDL code was written and tested in Active HDL 7.2 software to generate the logic functions of each gate based on the input values. Output waveforms confirmed the gates were functioning correctly as designed.

Original Description:

experiment of mdu syllabus

Original Title

Dsd Experiment1

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document describes an experiment to design various logical gates using VHDL. The aim was to create VHDL code for AND, OR, NAND, NOR, XOR, XNOR, and NOT gates. VHDL code was written and tested in Active HDL 7.2 software to generate the logic functions of each gate based on the input values. Output waveforms confirmed the gates were functioning correctly as designed.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

13 views6 pagesDesign Logic Gates VHDL

Uploaded by

Prem PrakashThe document describes an experiment to design various logical gates using VHDL. The aim was to create VHDL code for AND, OR, NAND, NOR, XOR, XNOR, and NOT gates. VHDL code was written and tested in Active HDL 7.2 software to generate the logic functions of each gate based on the input values. Output waveforms confirmed the gates were functioning correctly as designed.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 6

Experiment No: - 1

Aim: - To design various logical gates using VHDL.

Software Used: - Active HDL 7.2 VHDL Source Code: (i) For AND gate:library IEEE; use IEEE.std_logic_1164.all; entity and_g is port(a,b:in std_logic; z:out std_logic); end and_g; architecture beh of and_g is begin process(a,b) begin if a='0' and b='0' then z<='0'; elsif a='0' and b='1' then z<='0'; elsif a='1' and b='0' then z<='0'; else z<='1'; end if; end process; end beh;

(ii) For OR gate:

library IEEE; use IEEE.std_logic_1164.all; entity or_g is port(a,b:in std_logic; z:out std_logic); end or_g; architecture beh1 of or_g is begin process(a,b) begin

Name:-Prem Prakash

Roll No.:-241/09

C.S.E(6th Sem.)

if a='0' and b='0' then z<='0'; elsif a='0' and b='1' then z<='1'; elsif a='1' and b='0' then z<='1'; else z<='1'; end if; end process; end beh1;

(iii) For NAND gate:

library IEEE; use IEEE.std_logic_1164.all; entity nand_g is port(a,b:in std_logic; z:out std_logic); end nand_g; architecture beh2 of nand_g is begin process(a,b) begin if a='0' and b='0' then z<='1'; elsif a='0' and b='1' then z<='1'; elsif a='1' and b='0' then z<='1'; else z<='0'; end if; end process; end beh2;

(iv) For NOR gate:

library IEEE; use IEEE.std_logic_1164.all; entity nor_g is port(a,b:in std_logic; z:out std_logic); end nor_g; architecture beh2 of nor_g is

Name:-Prem Prakash

Roll No.:-241/09

C.S.E(6th Sem.)

begin process(a,b) begin if a='0' and b='0' then z<='1'; elsif a='0' and b='1' then z<='0'; elsif a='1' and b='0' then z<='0'; else z<='0'; end if; end process; end beh2;

(v) For XOR gate:

library IEEE; use IEEE.std_logic_1164.all; entity xor_g is port(a,b:in std_logic; z:out std_logic); end xor_g; architecture beh4 of xor_g is begin process(a,b) begin if a= b then z<='0'; else z<='1'; end if; end process; end beh4;

(vi) For XNOR gate:

library IEEE; use IEEE.std_logic_1164.all; entity xnor_g is port(a,b:in std_logic; z:out std_logic); end xnor_g; architecture beh5 of xnor_g is begin

Name:-Prem Prakash

Roll No.:-241/09

C.S.E(6th Sem.)

process(a,b) begin if a= b then z<='1'; else z<='0'; end if; end process; end beh5;

(vii) For NOT gate:

library IEEE; use IEEE.std_logic_1164.all; entity not_g is port(a:in std_logic;z:out std_logic); end not_g; architecture beh6 of not_g is begin process(a) begin if a='0' then z<='1'; else z<='0'; end if; end process; end beh6;

Name:-Prem Prakash

Roll No.:-241/09

C.S.E(6th Sem.)

Output waveform of programs:

For AND gate:

For OR gate:

For NAND gate:

For NOR gate:

Name:-Prem Prakash

Roll No.:-241/09

C.S.E(6th Sem.)

For XOR gate:

For XNOR gate:

For NOT gate:

Name:-Prem Prakash

Roll No.:-241/09

C.S.E(6th Sem.)

You might also like

- DSD Lab ManualDocument16 pagesDSD Lab ManualPreeti SinghNo ratings yet

- Computer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringDocument71 pagesComputer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringSankhadeep ChakrabartiNo ratings yet

- Build your own Blockchain: Make your own blockchain and trading bot on your pcFrom EverandBuild your own Blockchain: Make your own blockchain and trading bot on your pcNo ratings yet

- VHDL Implementation: NAME:-Aman Kumar ROLL NO.: - 2020UCO1539Document6 pagesVHDL Implementation: NAME:-Aman Kumar ROLL NO.: - 2020UCO1539AMAN KUMARNo ratings yet

- Network Security All-in-one: ASA Firepower WSA Umbrella VPN ISE Layer 2 SecurityFrom EverandNetwork Security All-in-one: ASA Firepower WSA Umbrella VPN ISE Layer 2 SecurityNo ratings yet

- Experiment-1: Aim: Program of VHDL To Study The Not GateDocument75 pagesExperiment-1: Aim: Program of VHDL To Study The Not GatejaigodaraNo ratings yet

- HDL Experiment1Document3 pagesHDL Experiment1choudharyarjun1121No ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- VHDL CompleteDocument21 pagesVHDL CompleteMridanku Shekhar PramanickNo ratings yet

- IP Routing Protocols All-in-one: OSPF EIGRP IS-IS BGP Hands-on LabsFrom EverandIP Routing Protocols All-in-one: OSPF EIGRP IS-IS BGP Hands-on LabsNo ratings yet

- VHDL TutorialDocument14 pagesVHDL TutorialMohan Kumar SmkNo ratings yet

- Wa0000.Document35 pagesWa0000.KARTAVYANo ratings yet

- PDF Lab 1Document4 pagesPDF Lab 1Yoonji MinNo ratings yet

- VHDL AND, OR, NOT, XOR, XNOR Gate CodeDocument7 pagesVHDL AND, OR, NOT, XOR, XNOR Gate CodeRishi Raj YadavNo ratings yet

- Exp No: 01 Verification of Logic Gates AimDocument54 pagesExp No: 01 Verification of Logic Gates AimDivya ChanduriNo ratings yet

- VHDL Lab FileDocument48 pagesVHDL Lab FileAnkit Gupta100% (1)

- Adsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'Document29 pagesAdsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'AnkitShubhoeMukherjeeNo ratings yet

- UNIT-3: Design Combinational CKT Using Architecture ModelDocument36 pagesUNIT-3: Design Combinational CKT Using Architecture Modelankit_4382No ratings yet

- Design and Simulation of Logic Gates Using VHDLDocument26 pagesDesign and Simulation of Logic Gates Using VHDLSushanth BabuNo ratings yet

- Sri Venkateswara College of Engineering & Technology R.V.S Nagar, Chittoor M.Tech. I Semester (Decs) Digital System Design Lab List of ExperimentsDocument47 pagesSri Venkateswara College of Engineering & Technology R.V.S Nagar, Chittoor M.Tech. I Semester (Decs) Digital System Design Lab List of ExperimentssubbuNo ratings yet

- VHDL CodeDocument34 pagesVHDL CodeHimanshu Thakur100% (1)

- Digital Circuits & Systems - Ii Lab ETEC 351: Maharaja Agrasen Institute of TechnologyDocument16 pagesDigital Circuits & Systems - Ii Lab ETEC 351: Maharaja Agrasen Institute of Technologysandeepdaiya45gmailcNo ratings yet

- VHDL Code for Common Logic Gates and Ripple Carry AdderDocument7 pagesVHDL Code for Common Logic Gates and Ripple Carry AdderSyrine DabbecheNo ratings yet

- VHDL Codes for Basic Digital CircuitsDocument12 pagesVHDL Codes for Basic Digital CircuitsPrabhjinder Singh AulakhNo ratings yet

- VHDL Models for Half Adder, Multiplexer, Multiplier, D-Latch and Other Digital ComponentsDocument17 pagesVHDL Models for Half Adder, Multiplexer, Multiplier, D-Latch and Other Digital ComponentssanjanaNo ratings yet

- VHDL Code for 4:1 Mux and 1:4 DemuxDocument2 pagesVHDL Code for 4:1 Mux and 1:4 DemuxAbdul RehmanNo ratings yet

- VHDL ReportDocument29 pagesVHDL ReportSalman AliNo ratings yet

- VHDL Codes for Logic Gates and Sequential CircuitsDocument42 pagesVHDL Codes for Logic Gates and Sequential CircuitsNaresh KumarNo ratings yet

- Digital Lab Cs 6211 VHDL ProgramsDocument13 pagesDigital Lab Cs 6211 VHDL ProgramsMurugan GNo ratings yet

- VHDLDocument55 pagesVHDLparassh knowledgeNo ratings yet

- Digital Circuits & Systems – II LabDocument35 pagesDigital Circuits & Systems – II LabAbhinav RajNo ratings yet

- VHDL Code For Halfadder: - Logic - XorDocument30 pagesVHDL Code For Halfadder: - Logic - XorAnushNo ratings yet

- Comparateur 1bit StructurelleDocument5 pagesComparateur 1bit StructurelleMohamed ChamessNo ratings yet

- VHDL Assignments Digital Logic GatesDocument48 pagesVHDL Assignments Digital Logic GatesALEX100% (1)

- Lab3 - Achmad Mauludin H. - 165060301111002Document4 pagesLab3 - Achmad Mauludin H. - 165060301111002Mauudin BRgNo ratings yet

- Half Adder: Ieee Ieee STD - LOGIC - 1164 Ieee STD - Logic - Arith Ieee STD - Logic - UnsignedDocument11 pagesHalf Adder: Ieee Ieee STD - LOGIC - 1164 Ieee STD - Logic - Arith Ieee STD - Logic - UnsignedUma ShankarNo ratings yet

- VHDL Operators BasicsDocument0 pagesVHDL Operators BasicsjushwanthNo ratings yet

- Tut 6 Digital VHDLDocument16 pagesTut 6 Digital VHDLShobhit GargNo ratings yet

- vhdlDocument13 pagesvhdlSrijeeta SenNo ratings yet

- VHDL ProgramDocument5 pagesVHDL ProgramJaswanth TejaNo ratings yet

- Experiment No. 1: Objective: Apparatus Used TheoryDocument21 pagesExperiment No. 1: Objective: Apparatus Used TheoryShashank AgarwalNo ratings yet

- Malviya National Institute of Technology, JaipurDocument18 pagesMalviya National Institute of Technology, JaipurAnand Singh KaviyaNo ratings yet

- HDL Lab ManualDocument56 pagesHDL Lab ManualAvinash C Sheshu100% (3)

- CALab - Jalish BuktawarDocument19 pagesCALab - Jalish BuktawarSouvik PalNo ratings yet

- Modeling Scheme.: Objective 1: VHDL Code For 2 Input XOR Gate Using BehavioralDocument24 pagesModeling Scheme.: Objective 1: VHDL Code For 2 Input XOR Gate Using BehavioralAmrinder SinghNo ratings yet

- VHDL Lab ProgramsDocument57 pagesVHDL Lab Programsedrredy100% (5)

- E Cad Lab ManualDocument51 pagesE Cad Lab ManualRajesh DoradlaNo ratings yet

- (B) Simulate The Simplified Logic Expression Using VHDL and Verify It's WorkingDocument19 pages(B) Simulate The Simplified Logic Expression Using VHDL and Verify It's WorkingAparna RoyNo ratings yet

- Rapport 2:VHDL: Réalisé Par: RAIS Aya LAZREK GhitaDocument9 pagesRapport 2:VHDL: Réalisé Par: RAIS Aya LAZREK GhitaEssNo ratings yet

- 4x1 Multiplexer and Other VHDL Code ExamplesDocument25 pages4x1 Multiplexer and Other VHDL Code Examplesnitin_280890No ratings yet

- VHDL ManualDocument19 pagesVHDL ManualDr.B.Krishna KumarNo ratings yet

- Experiment 1: Aim: WAP in VHDL To Implement Basic GatesDocument10 pagesExperiment 1: Aim: WAP in VHDL To Implement Basic GatesMrigya JainNo ratings yet

- Collection of VHDL Lab Experiments Part - IDocument8 pagesCollection of VHDL Lab Experiments Part - Ijobchunkath_26274013No ratings yet

- Saloni Garg (B21AI036) - (Lab 3) Practice QuestionsDocument11 pagesSaloni Garg (B21AI036) - (Lab 3) Practice QuestionsSaloni GargNo ratings yet

- VHDL Code Examples for Digital Logic Design ComponentsDocument20 pagesVHDL Code Examples for Digital Logic Design ComponentsVasu SiriNo ratings yet

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDocument20 pagesAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluNo ratings yet

- EXOR Gate Using Concurrent Statements: RTL ViewDocument59 pagesEXOR Gate Using Concurrent Statements: RTL ViewSurbhit SinhaNo ratings yet

- All CertificationsDocument5 pagesAll CertificationsPrem PrakashNo ratings yet

- Experiment n1 in JavaDocument6 pagesExperiment n1 in JavaPrem PrakashNo ratings yet

- Windows Server 2008 Directory Services Lab ManualDocument11 pagesWindows Server 2008 Directory Services Lab ManualPrem PrakashNo ratings yet

- Windows Server 2008 Directory Services Lab ManualDocument11 pagesWindows Server 2008 Directory Services Lab ManualPrem PrakashNo ratings yet

- Windows Server 2008 Directory Services Lab ManualDocument11 pagesWindows Server 2008 Directory Services Lab ManualPrem PrakashNo ratings yet

- Windows Server 2008 Directory Services Lab ManualDocument11 pagesWindows Server 2008 Directory Services Lab ManualPrem PrakashNo ratings yet

- Bisectors and altitudes of trianglesDocument6 pagesBisectors and altitudes of trianglesPrem PrakashNo ratings yet

- Preschool Teacher Resume SampleDocument5 pagesPreschool Teacher Resume Samplemuwebuwynug3100% (1)

- Multiple Menu ModelDocument39 pagesMultiple Menu Modelapi-281764670No ratings yet

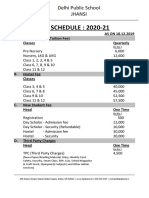

- Fee Shedule 2020-21 Final DiosDocument2 pagesFee Shedule 2020-21 Final Diosapi-210356903No ratings yet

- Dbatu MisDocument1 pageDbatu Misgamingaao75No ratings yet

- SocratesDocument119 pagesSocratesLeezl Campoamor OlegarioNo ratings yet

- A Brief History of The Chakras in Human Body: March 2019Document8 pagesA Brief History of The Chakras in Human Body: March 2019Shyamanta SharmaNo ratings yet

- 495 TextDocument315 pages495 TextSaiful LahidjunNo ratings yet

- Lesson Plan For Teaching GrammarDocument9 pagesLesson Plan For Teaching Grammarruszita75% (4)

- Global GuideDocument110 pagesGlobal GuideAstrid RahardjoNo ratings yet

- WHERE ARE YOU FROMDocument2 pagesWHERE ARE YOU FROMCamille Nagel0% (1)

- ECD & Brain DevelopmentDocument23 pagesECD & Brain DevelopmentMuhammad Iqbal Khan SonNo ratings yet

- Sri Ramachandra University Application-09Document5 pagesSri Ramachandra University Application-09Mohammed RaziNo ratings yet

- Prototype Lesson Plan Using Trimodal Delivery PlatformDocument5 pagesPrototype Lesson Plan Using Trimodal Delivery PlatformJEAN P DE PERALTANo ratings yet

- Study Skills and Health NotesDocument35 pagesStudy Skills and Health Notesmohamed osman0% (1)

- Mid-Term Examination Card of First Semester of 2016/2017Document1 pageMid-Term Examination Card of First Semester of 2016/2017Keperawatan14No ratings yet

- Collins Ks3 Science Homework Book 1Document7 pagesCollins Ks3 Science Homework Book 1afmseodmf100% (1)

- Mechanical CADD CourseDocument8 pagesMechanical CADD CourseCadd CentreNo ratings yet

- Residential Comprehensive 2015 Leaflet PDFDocument7 pagesResidential Comprehensive 2015 Leaflet PDFmsatpathy2003No ratings yet

- Hotel ManagerDocument2 pagesHotel ManagerImee S. YuNo ratings yet

- Company Contact: Kushagra Bajaj Purushottam RunthalaDocument25 pagesCompany Contact: Kushagra Bajaj Purushottam RunthalakumarneerajNo ratings yet

- Health 5 LAS Quarter 3Document31 pagesHealth 5 LAS Quarter 3Josephine Acio100% (4)

- Cover LetterDocument7 pagesCover LetterThế TuấnNo ratings yet

- Examen A2 VirtualDocument2 pagesExamen A2 VirtualMiguel MedinaNo ratings yet

- Habits of The Household Audiobook PDFDocument38 pagesHabits of The Household Audiobook PDFHOPE TOOLS STORE100% (2)

- S8A2Document16 pagesS8A2eddiewalsh25No ratings yet

- 43 All India Conference of Dravidian LinguistsDocument6 pages43 All India Conference of Dravidian LinguistsV N BHATTATHIRINo ratings yet

- OutLines of European Board Exam-HNS - ExamDocument19 pagesOutLines of European Board Exam-HNS - ExamDrMohmd ZidaanNo ratings yet

- IIP HostDocument7 pagesIIP HostadityaNo ratings yet

- Post Graduate Diploma in Horticulture and Landscape GardeningDocument9 pagesPost Graduate Diploma in Horticulture and Landscape GardeningNilesh KshirsagarNo ratings yet

- Goshgar Narimanli: Work ExperienceDocument2 pagesGoshgar Narimanli: Work ExperienceZiyaNo ratings yet

- Let's Draw Flowers: A Creative Workbook for Doodling and BeyondFrom EverandLet's Draw Flowers: A Creative Workbook for Doodling and BeyondNo ratings yet

- Art Models AnaRebecca002: Figure Drawing Pose ReferenceFrom EverandArt Models AnaRebecca002: Figure Drawing Pose ReferenceRating: 1 out of 5 stars1/5 (1)

- One Zentangle a Day: A 6-Week Course in Creative Drawing for Relaxation, Inspiration, and FunFrom EverandOne Zentangle a Day: A 6-Week Course in Creative Drawing for Relaxation, Inspiration, and FunRating: 4 out of 5 stars4/5 (25)

- Coloring Book for Adults & Grown Ups : An Easy & Quick Guide to Mastering Coloring for Stress Relieving Relaxation & Health Today!: The Stress Relieving Adult Coloring PagesFrom EverandColoring Book for Adults & Grown Ups : An Easy & Quick Guide to Mastering Coloring for Stress Relieving Relaxation & Health Today!: The Stress Relieving Adult Coloring PagesRating: 2 out of 5 stars2/5 (12)

- Art Models Paris015: Figure Drawing Pose ReferenceFrom EverandArt Models Paris015: Figure Drawing Pose ReferenceRating: 3 out of 5 stars3/5 (3)

- CROCHET FOR BEGINNERS TO ADVANCED GUIDE: A Step-by-Step Journey from Novice to Expert in the Art of Crochet (2024)From EverandCROCHET FOR BEGINNERS TO ADVANCED GUIDE: A Step-by-Step Journey from Novice to Expert in the Art of Crochet (2024)No ratings yet

- Art Models SarahAnn031: Figure Drawing Pose ReferenceFrom EverandArt Models SarahAnn031: Figure Drawing Pose ReferenceRating: 3 out of 5 stars3/5 (4)

- Celestial Watercolor: Learn to Paint the Zodiac Constellations and Seasonal Night SkiesFrom EverandCelestial Watercolor: Learn to Paint the Zodiac Constellations and Seasonal Night SkiesRating: 3.5 out of 5 stars3.5/5 (6)

- Sharpie Art Workshop: Techniques & Ideas for Transforming Your WorldFrom EverandSharpie Art Workshop: Techniques & Ideas for Transforming Your WorldRating: 3 out of 5 stars3/5 (16)

- Just Draw Botanicals: Beautiful Botanical Art, Contemporary Artists, Modern MaterialsFrom EverandJust Draw Botanicals: Beautiful Botanical Art, Contemporary Artists, Modern MaterialsRating: 3.5 out of 5 stars3.5/5 (3)

- Drawing: Flowers: Learn to Draw Step-by-StepFrom EverandDrawing: Flowers: Learn to Draw Step-by-StepRating: 5 out of 5 stars5/5 (2)

- Creative Abstract Watercolor: The beginner's guide to expressive and imaginative paintingFrom EverandCreative Abstract Watercolor: The beginner's guide to expressive and imaginative paintingNo ratings yet

- Art Models AnaIv309: Figure Drawing Pose ReferenceFrom EverandArt Models AnaIv309: Figure Drawing Pose ReferenceRating: 3 out of 5 stars3/5 (2)

- The Illustrator's Guide To Procreate: How to make digital art on your iPadFrom EverandThe Illustrator's Guide To Procreate: How to make digital art on your iPadNo ratings yet

- Beginner's Guide To Procreate: Characters: How to create characters on an iPad ®From EverandBeginner's Guide To Procreate: Characters: How to create characters on an iPad ®3dtotal PublishingRating: 4 out of 5 stars4/5 (1)

- Living Color: Painting, Writing, and the Bones of SeeingFrom EverandLiving Color: Painting, Writing, and the Bones of SeeingRating: 4 out of 5 stars4/5 (4)

- Art Models Ginger040: Figure Drawing Pose ReferenceFrom EverandArt Models Ginger040: Figure Drawing Pose ReferenceRating: 4 out of 5 stars4/5 (5)

- The Everything Drawing Book: From Basic Shape to People and Animals, Step-by-step Instruction to get you startedFrom EverandThe Everything Drawing Book: From Basic Shape to People and Animals, Step-by-step Instruction to get you startedRating: 3 out of 5 stars3/5 (5)

- Generative Art: A practical guide using ProcessingFrom EverandGenerative Art: A practical guide using ProcessingRating: 4 out of 5 stars4/5 (4)

- Portrait Painting in Oil: 10 Step by Step Guides from Old Masters: Learn to Paint Portraits via Detailed Oil Painting DemonstrationsFrom EverandPortrait Painting in Oil: 10 Step by Step Guides from Old Masters: Learn to Paint Portraits via Detailed Oil Painting DemonstrationsRating: 4.5 out of 5 stars4.5/5 (3)

- Drawing Mandalas: How to Create Beautiful, Intricate PatternsFrom EverandDrawing Mandalas: How to Create Beautiful, Intricate PatternsNo ratings yet

- Art Models Becca425: Figure Drawing Pose ReferenceFrom EverandArt Models Becca425: Figure Drawing Pose ReferenceRating: 3.5 out of 5 stars3.5/5 (3)

- How to Draw Anything Anytime: A Beginner's Guide to Cute and Easy Doodles (Over 1,000 Illustrations)From EverandHow to Draw Anything Anytime: A Beginner's Guide to Cute and Easy Doodles (Over 1,000 Illustrations)Rating: 4.5 out of 5 stars4.5/5 (18)

- Jackie Shaw's Learn to Paint Flowers: A Step-by-Step Approach to Beautiful ResultsFrom EverandJackie Shaw's Learn to Paint Flowers: A Step-by-Step Approach to Beautiful ResultsRating: 5 out of 5 stars5/5 (1)

- Braid Girl!: The Hair Braiding Instructional BookFrom EverandBraid Girl!: The Hair Braiding Instructional BookRating: 3 out of 5 stars3/5 (1)

- Journal with Purpose: Over 1000 motifs, alphabets and icons to personalize your bullet or dot journalFrom EverandJournal with Purpose: Over 1000 motifs, alphabets and icons to personalize your bullet or dot journalRating: 4.5 out of 5 stars4.5/5 (39)