Professional Documents

Culture Documents

Di 182

Uploaded by

Sebastian QuaroneOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Di 182

Uploaded by

Sebastian QuaroneCopyright:

Available Formats

DI-182 Design Idea TOPSwitch-HX

Standard 65 W Notebook Adapter Which Meets Requirements for Energy Star 2.0 (ES 2.0)

Application

Notebook

Device

TOP259EN

Power Output

65 W

Input Voltage

90 265 VAC

Output Voltage

19 V 5%

Topology

Flyback

Design Highlights Very compact, low part-count Low prole eSIP-7C Single-Inline package Same thermal impedance characteristics as standard TO-220 package Allows lower overall height and smaller board footprint Clip mounted eSIP package easily passes shock and vibration test to IEC60068 Highly energy efcient Very low no-load input power: <250 mW at 230 VAC High average efciency: >87.5% meeting ENERGY STAR v2.0 draft requirements (measured at the end of cable: 1.8 m, 18 AWG, 100 m impedance) 132 kHz operation allows small transformer (EE28) Internal current-limit reduction vs line-voltage increase removes need for secondary side current limiting used to meet powerlimited source requirements Accurate hysteretic thermal shutdown protection Timed over-load protection with automatic recovery Meets CISPR-22/EN55022 B conducted EMI limits

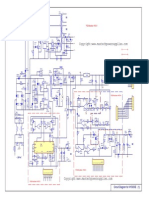

Operation The power supply design shown in Figure 1 utilizes the TOP259EN. The TOPSwitch-HX products integrate a 700 V MOSFET with a multi-function PWM controller in one device. The optimized combination of switching MOSFET and integrated driver present for low switching loss enable a highly efcient and compact 65 W notebook power supply able to safely operate in a sealed enclosure up to an ambient temperature of 40 C. The bridge rectier BR1, at the input of the power supply, recties the line input; electrolytic capacitor C2 lters the input. Fuse F1 protects against catastrophic failure. Common mode EMI is ltered by L1, L2, L3, C3, and C11. Common-mode choke L2 lters lower frequencies while L3 lters higher frequencies. Differential ltering is provided by the leakage inductance of L2 and X capacitor C1. As C1 has a capacitance greater than 0.1 F, discharge resistors R1 and R2 are required to discharge C1 after removal of AC. To reduce differential EMI generation C5 provides decoupling for the primary switching current.

C11 2.2 nF 250 VAC C12 1 nF R16 100 V 33 � C14 C13 470 �F 470 �F 25 V 25 V D6 MBR20100CT R10 C10 VR1 22 �F 301 � 1N5248B 1% 50 V 18 V D5 BAV 19WS R11 2 M� C8 100 nF 50 V RTN

C4 2.2 nF 1 kV BR1 3KBP08M R6 33 � R3 2.0 M� R7 5.1 M�

T1 1 EE28 FL1 R5 100 k� 1/2 W 3

19 V, 3.42 A

FL2

D1 DL4937

L3 12 mH L2 200 �H C2 120 �F 400 V

R4 2.0 M�

R8 6.8 M� C5 100 nF 400 V

R22 C19 20 k� 470 pF 50 V R12 5.1 k� D3 BAV19WS TOPSwitch-HX U1

D V TOP259EN CONTROL C

R18 680 �

R1 R2 2.2 M� 2.2 M� F1 4A L

S X

C9 100 nF 25 V

U3B ISP817C

U3A ISP817C

C1 330 nF 275 VAC

R19 C17 68.1 k� 100 nF R15 6.8 � C7 47 �F 16 V R21 1 k� U2 LM431 2%

E N 90 - 265 VAC L1 Ferrite Bead C3 470 pF 250 VAC R9 14 k� 1%

C6 100 nF 50 V

R20 10 k� 1%

PI-5023-071408

Figure 1: Schematic of a 65 W Notebook Adapter Power Supply Using TOPSwitch-HX TOP259EN.

www.powerint.com

July 2008

The TOP259EN, with its integrated multi-mode controller, is used in a yback conguration. It maintains output regulation by changing the duty cycle as a function of the control pin current. To maintain high efciency across the whole load range, the multimode controller changes between pulse width modulation and xed on-time variable frequency control. To provide constant output overload power with changing line voltage, as line voltage increases, resistors R7, R8, and R9 reduce the internal current limit of the TOP259EN. This allows the supply to limit the output overload power to <100 VA at high line, while still delivering the rated output at low line. The primary sides output overvoltage protection (OVP) senses the bias-winding voltage using Zener diode VR1. This is used to provide both open-loop protection and output-overload protection under a single-fault condition. Resistors R10 and R11 with capacitor C8 determine the delay before shutdown is triggered. This prevents false triggering during startup and load transients. The value of R12 selects the hysteretic shutdown behavior of U1. Capacitor C9 helps to lter high frequency noise that may appear on the V pin. The output is rectied by diode D6 which has an RC snubber (C12 and R16) to dampen leakage inductance ringing and reduce radiated EMI. The output is ltered by capacitors C13 and C14. Feedback is derived from the output via optocoupler U3A. Resistor R18 sets the DC gain. Shunt regulator U2 has an accurate internal voltage reference, and with resistors R19 and R20, sets the output voltage to 19 V. Diode D3 prevents loading of the V pin by the OVP circuit and also isolates the line sense circuit from the OVP circuit.

Key Design Points Verify that the maximum drain voltage does not exceed 650 V at high line and maximum overload. Adjust the values of C4 and R5 as necessary. Resistor R6 dampens high frequency ringing and improves EMI. Select the value of VR1 such that it does not falsely trigger OVP. VR1 should be chosen above the bias-winding voltage measured under low line and full load conditions. If latching OVP is desired, select R12 as 20 . U1 does not require an insulating pad for reduced EMI. It has a tab connected to the electrically quiet source.

PI-5049-032508

80 70 60 50 40

QP AV

dB�V

30 20 10 0 -10 -20 0.15 1.0 10.0 100.0

MHz

Figure 3. Conducted EMI, EN55022 B Limits. Measurements Made at 230 VAC With 5.6 Resistive Load (Output Grounded).

Transformer Parameters

Core Material

PI-5048-032508

EE28, TDK or equivalent, gapped for ALG of 299 nH/t Vertical 10 pin, pin 6 to pin 10 are to be removed Bias: 5T 3, 30 AWG Primary 1: 17T 2, 26 AWG Shield: 1T Cu foil, 1 mil thick Secondary: 6T 4, 26 AWG-TIW Shield: 1T Cu foil, 1 mil thick Primary 2: 17T 2, 25 AWG Bias (45), Primary-1 (32), Shield (1NC), Secondary (FL1FL2), Shield (1NC), Primary-2 (21)

320 280

Bobbin

Input Power (mW)

240 200 160

Winding Details

Winding Order

120 80 40 0

Primary Inductance 343 H, 5% at 132 kHz Primary Resonant Frequency Leakage Inductance 1.1 MHz (minimum) 4 H (maximum)

90

115

140

165

190

215

240

265

Input Voltage (VAC)

Figure 2. No Load Input Power vs. Line Voltage.

Table 1. Transformer Parameters. (AWG = American Wire Gauge, TIW = Triple Insulated Wire, NC = No Connection)

Power Integrations 5245 Hellyer Avenue San Jose, CA 95138, USA. Main: +1 408-414-9200 Customer Service Phone: +1-408-414-9665 Fax: +1-408-414-9765 Email: usasales@powerint.com On the Web www.powerint.com A 07/08

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS. The products and applications illustrated herein (transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm. The PI logo, TOPSwitch, TinySwitch, LinkSwitch, DPA-Switch, PeakSwitch, EcoSmart, Clampless, E-Shield, Filterfuse, StackFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. 2008, Power Integrations, Inc.

DI-182

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- 300VF WD DescriptionDocument59 pages300VF WD DescriptionSamuel Acevedo50% (2)

- PLC Based Sequential Batch Process CONTROL System1Document27 pagesPLC Based Sequential Batch Process CONTROL System1Ritesh Vaishnav100% (1)

- Drive Test Problems (Part 2)Document25 pagesDrive Test Problems (Part 2)Abdelrahman.Mostafa100% (7)

- Mainboard ESC Model P4M800PRO MDocument29 pagesMainboard ESC Model P4M800PRO MHo Thanh BinhNo ratings yet

- ESP8266EX EspressifSystemsDocument31 pagesESP8266EX EspressifSystemsSigit SandjajaNo ratings yet

- W00tsec Unpacking Firmware Images From Cable ModemsDocument10 pagesW00tsec Unpacking Firmware Images From Cable ModemsSebastian QuaroneNo ratings yet

- 197 TrainDocument174 pages197 Trainshrk6915689No ratings yet

- An 197Document12 pagesAn 197Anonymous lB6SsHu5KNo ratings yet

- A New Upper Pleistocene Tapir From ArgenDocument8 pagesA New Upper Pleistocene Tapir From ArgenSebastian QuaroneNo ratings yet

- LTY400HM02 Samsung PDFDocument30 pagesLTY400HM02 Samsung PDFSebastian QuaroneNo ratings yet

- HISENSE NOBLEX EA32X5000 Chasis MTK5655EPDJDocument88 pagesHISENSE NOBLEX EA32X5000 Chasis MTK5655EPDJalvaro marcos manuel lopez100% (1)

- Service Manual: HCD-GT22/GT44/GT55Document98 pagesService Manual: HCD-GT22/GT44/GT55Sebastian QuaroneNo ratings yet

- Samsung Card-UFD Authentication Utility Manual English 1.3Document6 pagesSamsung Card-UFD Authentication Utility Manual English 1.3Sebastian QuaroneNo ratings yet

- User Manual: Chipper Check IIDocument38 pagesUser Manual: Chipper Check IISebastian QuaroneNo ratings yet

- LTY400HM02 Samsung PDFDocument30 pagesLTY400HM02 Samsung PDFSebastian QuaroneNo ratings yet

- Ad1888 Ac '97 Soundmax Codec: This Datasheet Has Been Downloaded From at ThisDocument32 pagesAd1888 Ac '97 Soundmax Codec: This Datasheet Has Been Downloaded From at ThisSebastian QuaroneNo ratings yet

- SN 74 LVC 1 G 32Document34 pagesSN 74 LVC 1 G 32Sebastian QuaroneNo ratings yet

- Taipei, May 26, 2005 - Silicon Integrated Systems Corp (Sis) and Agere Systems (Nyse: Agr.ADocument1 pageTaipei, May 26, 2005 - Silicon Integrated Systems Corp (Sis) and Agere Systems (Nyse: Agr.ASebastian QuaroneNo ratings yet

- MCP4725Document42 pagesMCP4725vadmax2011No ratings yet

- En 25 F 80Document33 pagesEn 25 F 80mactocheNo ratings yet

- Admiral TG2100 Chasis PTFM05-1Document4 pagesAdmiral TG2100 Chasis PTFM05-1Daniel AvecillaNo ratings yet

- MCP 4725Document15 pagesMCP 4725Sebastian QuaroneNo ratings yet

- Epson T500series Printer MechsDocument2 pagesEpson T500series Printer MechsSebastian QuaroneNo ratings yet

- Manual Calefon Orbis 320BTO - 0000000600-DCMDocument2 pagesManual Calefon Orbis 320BTO - 0000000600-DCMjulioramos1No ratings yet

- Manual Calefon Orbis 320BTO - 0000000600-DCMDocument2 pagesManual Calefon Orbis 320BTO - 0000000600-DCMjulioramos1No ratings yet

- 6ZG 1Document22 pages6ZG 1dmst622No ratings yet

- CD40106 Hex Schmitt Trigger DatasheetDocument6 pagesCD40106 Hex Schmitt Trigger Datasheetlookb64No ratings yet

- HY3030EDocument2 pagesHY3030ESebastian QuaroneNo ratings yet

- Epson T500series Printer MechsDocument2 pagesEpson T500series Printer MechsSebastian QuaroneNo ratings yet

- Msi ms-7125 Rev 0a SCHDocument33 pagesMsi ms-7125 Rev 0a SCHSebastian QuaroneNo ratings yet

- HS-GMX600 HS-PX107: Service ManualDocument0 pagesHS-GMX600 HS-PX107: Service ManualSebastian QuaroneNo ratings yet

- Msi MS-6633 - Rev 1.0Document35 pagesMsi MS-6633 - Rev 1.0Claudia MarquezNo ratings yet

- The World of PC Recording by Dave Casey of TASCAM PDFDocument28 pagesThe World of PC Recording by Dave Casey of TASCAM PDFnetzah2padreNo ratings yet

- Powered, Tri-Amplified Compact Line Array Module: SeriesDocument2 pagesPowered, Tri-Amplified Compact Line Array Module: SeriesIrvanda ENVIOUSNo ratings yet

- PC Express - Dealer's Price ListDocument2 pagesPC Express - Dealer's Price ListJazz AdazaNo ratings yet

- Fiti Power Products Presentation 2013 Q2 Kingpex V2Document33 pagesFiti Power Products Presentation 2013 Q2 Kingpex V2Renato HernandezNo ratings yet

- Single Phase TransformerDocument53 pagesSingle Phase TransformerGurpreet Singh100% (2)

- IC615 Embedded Systems - 23 - 09 - 2020 PDFDocument154 pagesIC615 Embedded Systems - 23 - 09 - 2020 PDFHussainNo ratings yet

- Easy refrigeration controllers connection diagramsDocument1 pageEasy refrigeration controllers connection diagramskelvinNo ratings yet

- 2SK2876 01MR PDFDocument4 pages2SK2876 01MR PDFAnonymous Uk3JxlHANo ratings yet

- Documented Routine and Type Testing For Transformers To IEC 60076 1 PDFDocument1 pageDocumented Routine and Type Testing For Transformers To IEC 60076 1 PDFMando MandoNo ratings yet

- HDL10 A Small System Config PDFDocument2 pagesHDL10 A Small System Config PDFDavid JaraNo ratings yet

- Technology For Life: Medical SolutionsDocument12 pagesTechnology For Life: Medical SolutionsĐông PhùngNo ratings yet

- Profibus Introduction Aug2005 PDFDocument9 pagesProfibus Introduction Aug2005 PDFMohamed IyadNo ratings yet

- CM108 Datasheet PDFDocument26 pagesCM108 Datasheet PDFFco. Jefferson Ferreira de SáNo ratings yet

- GTX 770 OC V299 P2005-A01 Rev 1.0 SchematicsDocument33 pagesGTX 770 OC V299 P2005-A01 Rev 1.0 SchematicsGed Donis100% (1)

- Pelco Endura NVR5100 Series Network Video Recorder SpecDocument2 pagesPelco Endura NVR5100 Series Network Video Recorder Specr0cks0lidNo ratings yet

- Tea 1601Document27 pagesTea 1601Leonel Edgardo MoncadaNo ratings yet

- Design and Implementation of Boost Converter For Photovoltaic SystemsDocument5 pagesDesign and Implementation of Boost Converter For Photovoltaic SystemsGaurav SharmaNo ratings yet

- Kendriya Vidyalaya Physics ProjectDocument17 pagesKendriya Vidyalaya Physics ProjectPrajwal SalviNo ratings yet

- Westermo User Guide Ma-21 PDFDocument8 pagesWestermo User Guide Ma-21 PDFsolomonicbdmNo ratings yet

- SMD NPN Transistors TIP41 Series Technical Specifications and ParametersDocument3 pagesSMD NPN Transistors TIP41 Series Technical Specifications and Parametersrendy pradanaNo ratings yet

- 2500 VA 230V safety isolation transformerDocument1 page2500 VA 230V safety isolation transformerpadminittNo ratings yet

- Nmec-I Basics of Computers and Office Automation UNIT-I (Start) Introduction To ComputersDocument21 pagesNmec-I Basics of Computers and Office Automation UNIT-I (Start) Introduction To ComputersstaalinNo ratings yet

- Della Fave Renard ResumeDocument3 pagesDella Fave Renard ResumeRenard DellaFaveNo ratings yet

- Parallel Processing: An IntroductionDocument27 pagesParallel Processing: An IntroductionنورالدنياNo ratings yet

- Sup MotorolaDocument18 pagesSup MotorolaMario João MarioNo ratings yet

- Data Sheet: BCY58 BCY59Document8 pagesData Sheet: BCY58 BCY59Santz TechNo ratings yet

- Quiz With Answer CgaDocument2 pagesQuiz With Answer CgaAnonymous TvppppNo ratings yet