Professional Documents

Culture Documents

DFM

Uploaded by

Shashikiran HP0 ratings0% found this document useful (0 votes)

42 views40 pagesDesign rules are nothing but creating trace'idth spacing between pins. Design rules are created by importing netlist into pcb design software. A Design Rule is nothing but creating %iducials and types and di%erences bet'een them1.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentDesign rules are nothing but creating trace'idth spacing between pins. Design rules are created by importing netlist into pcb design software. A Design Rule is nothing but creating %iducials and types and di%erences bet'een them1.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

42 views40 pagesDFM

Uploaded by

Shashikiran HPDesign rules are nothing but creating trace'idth spacing between pins. Design rules are created by importing netlist into pcb design software. A Design Rule is nothing but creating %iducials and types and di%erences bet'een them1.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 40

1.

Flow of Complete PCB design

Library creation

Board outline and mechanicals

Importing netlist

Design Rule settings

Component Placement

Routing

Split plans

Silkscreen and Assembly settings

Gerber Settings

2. What are the inputs you need to design a PCB?

We need schematic B!" and netlist #some pcb engineer generates

netlist$ %rom &ard'are side and Board mechanicals %rom client i(e( board

outline mounting holes etc( Another important thing that 'e need is PCB

stack up it is based on comple)ity o% the board %or e)ample i% 'e are using

%pga %irst 'e should kno' number o% signal layers need %or %pga signal

breakout(

3. How to create footprint?

*ootprint %lo'

Pad stack creation

Pin placement

Assembly outline

Silkscreen outline

Place bound top #'e can mention height o% the here$

d%a bound top

+o probe top

Silk and assembly re%erence designator

,hese are the basic things 'e need to create a %ootprint %ollo' IPC

standards %or proper guidelines(

4. Board mechanicals

Dra' board outline by considering client re-uirementsplace mechanical

holes and global %iducials(create route keepin and place keepin areas

.uestions that can be raised %rom this

Si/e o% the mechanical holes that you ha0e used in your design and

clearances that you ha0e gi0en to these(

What are %iducials and use o% these %iducials and types and di%%erences

bet'een them1

*iducial placement and clearances(

What are the clearances you ha0e gi0en %rom board outline to route and

place keep in1

. What are the errors you got while importing netlist ?

Pcb %ootprint not %ound pins mismatch bet'een symbol and %ootprint etc(

!. How do you define design rules ?

Design rules are nothing but creating trace'idth spacing0ias limitations(

Generally 'e get trace 'idth and spacing details %rom stack up(

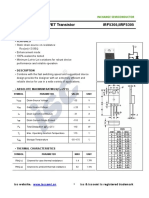

&ere are some standard 0ia si/es

". How do place components ?

Place ma2or components %irst i(e( connectors BGA3sma2or ICs then place

other sections(

a(&o' do you place connectors 1

*irst check 'eather i(e right angle or straight(I% it is right angle place at

edge o% the board and consider i% there any recommendations %rom client(

#.How do you plan routing and what are the parameters you consider

while routing ?

Placement routing plays ma2or rules in pcb design -uality o% the board

depends on placement and routing good placement and routing can

reduce your board %abrication cost also(

Place components by considering routing strategy and %ollo' schematic

%lo' once your placement is done do %an out %or all the components route

high speed inter%aces and comple) areas %irst and maintain ground

re%erence plane %or all high speed signals and make sure that e0ery trace

has re%erence plane and try to reduce 0ias on signals 0ias can change trace

characteristic impedance(

,ypes o% 4DA tools you used(

Stackup details(

What is characteristic impedance(

What are crosstalk 2itter ske' skin e%%ect(

Signal integrity concepts(

What is the use o% re%erence plane1

Guidelines %or di%%erent high speed inter%aces(

DDR5 routing guidelines and routing topologies(

,ypes o% 0ias and their standard si/es(

About decoupling capacitors(

Decoupling capacitor placement(

I% you used BGA in your designs type o% BGA and number o% pins and pitch(

Design for manufacturability

$. %esign for Fa&rication'

$.$ Board thic(ness

Standard board thickness are 6(657 6(689 6(6:5 ; 6(79< inches

$.2 Board si)e

As per the customer re-uirement(

$.3 Pad stac(

$.3.$ "inimum annular ring on a non=component hole is < mils

$.3.2 "inimum annular ring on a component hole is 76 mils(

$.3.3 Gang mask %or 0ery %ine pitch #less than 96 mils pitch$

Components i% re-uired(

$.4 *race width

"inimum trace 'idth > pre%erred 6(668 inches(

6(66? inches is also possible in select areas

$. +pacing

$..$ ,race > ,race "inimum > pre%erred 6(668 6(66? inches Possible

in select areas(

$..2 Pad > Pad "inimum > pre%erred 6(668 inches

$..3 Pad > ,race "inimum > pre%erred 6(668 inches

$..4 +o copper 'ithin 6(6<6 inches %rom edges o% PCB(

$.! ,ia si)e

$.!.$ "icro 0ia si/e #inches$ > 6(679 drill @ 6(69? pad

6(676 drill @ 6(67: pad Possible in select areas(

$.!.2 Po'er 0ia si/e #inches$ > 6(69? Drill @ 6(6?6 pad(

$." All %ine pitch components ha0e the pin numbers marked %or e0ery %i0e to

tenth pins depends on the density(

2. %esign for -ssem&ly

2.$ -ssem&ly tooling holes

6(79< inches dia( &oles added in minimum three corners o% the board(

,ooling hole locate 6(7:A inches %rom the edge o% the board(

2.2 Fiducials

2.2.$ Locate minimum o% three Global %iducials #6(6?6 inches Dia$ in a

,riangular position o% the board corner(

2.2.2 Locate minimum o% t'o local %iducials #6(6?6 inches Dia$ diagonally

across the perimeter o% the lo' pitch S"D components(

2.3 Component Placement

2.3.$ All components on one side pre%erable

2.3.2 All like components oriented in the same direction pre%erable

2.3.3 S"D and through hole components 6(766 inches %rom edge o%

PCB

2.3.4 "a2or components 'ill be placed 'ith 9< mils grid(

2.3. Discrete3s 'ill be placed 'ith 76 mils grid(

2.3.! Bnless other'ise there is a routing re-uirement all polari/ed

Components #diodes capacitors etc($ are placed 'ith a polarity

"ark to'ards top or right side(

7( When &oard trace starts radiating?

I ha0e no idea 'hat you are trying to ask here(

2. Propagation delay is more in which topology .stipline or

microstrip/

Stripline has longer propogation delay since there is high dielectric #i(e(

no air as in microstrip$

5( &o' to decide layer stack upC

&ighly dependant on number o% routes on the board controlled

impedance etc( Controlled impedance 'ill typically al'ays need some

type o% plane near it

?( What is signi%icance o% dielectric constant1C

,his is basically a measure o% capacitance o% the insulator material(

&igher numbers imply more signal loss(

. When you call signal as high speed signals?

Good rule o% thumbD 'hen propagation time is much longer than the

rise time then you ha0e a high speed signal

!. What is the difference &etween FP0- and -+1C?

*PGA is %ield programmable and ASIC is not

". What is C2B and its significance in FP0-?

Con%igurable Logic Block this is the programmable parts in an

*PGA like multiple)er %lip %lops adders etc(

#. What is ++*2 and its ad3antages?

Stub=series terminated logic( its main ad0antage is that the 0oltage

s'ing is %airly lo' so it operates -uickly and the dri0er 'ill sink@source

current %rom@to E,, island(

4 When to use terminations5 +eries termination when? -nd parallel

termination when?

,erminations are used 'hen there is a risk o% un'anted re%lections or

ringing clobbering senderFs data stream( Series termination is used

'hen increased rise@%all time is acceptable and 'hen dri0ing one load(

Series is most po'er e%%icient too(

Parallel termination typically has less propagation delay but more

po'er(

$6. %isad3antage of each termination

See abo0e

$$. Propagation delay of $ inch PCB trace on micro strip

,ypical 0alues are (7? ns@inch

$2. What is &uried 3ia

Eia is not e)posed to outer layers o% board(

$3. %raw the near end cross tal( shape?

$4. What is far end cross tal( and near end cross tal(

+ear=endD Inter%erence bet'een t'o pairs in a cable measured at the

same end o% the cable as the inter%ering transmitter(

*ar=endD Inter%erence bet'een t'o pairs o% a cable measured at the

other end o% the cable 'ith respect to the inter%ering transmitter(

7<( What is the band'idth o% a signalC

Range o% signal %re-uencies that are passed in the signal

78( I% you increase 'idth and height o% transmission line 'hat is e%%ect

on characteristic impedance #Go$C

Wider trace means lo'er Go( Increasing height o% trace #i assume you

mean distance %rom plane$ increases Go(

7A( I% 'e measure a cable impedance #G6H<6 ohm$ using millimeter

'hat is impedance

D!nFt understand the -uestion be more speci%ic

7I( 'hat is the min band'idth o% oscilloscope re-uired to measure

766"&/ signal(C

966 "&G

7:( What is skin e%%ect C

As %re-uency gets 0ery high i(e( se0eral hundreds o% "&G or into

the G&G the current 'ill %lo' mostly along outsides o% the

conductor1

&ere is a compilation o% the -uestions that may be asked to a PCB Design

4ngineer( Be sure to read a lot about high speed design rules layer stackup and

characteristic impedance(

7$. How do you calculate the trace impedance of a PCB trace?

Ans'er > ,here are many methods( A %ormula method gi0es a -uick result

though it is not highly accurate( A 9D *ield sol0er gi0es more accurate result( ,he

,race impedance depends upon the 'idth o% the trace separation %rom the

ground @ po'er plane and the relati0e permitti0ity o% the material

72. What is the difference &etween a &lind and &uried 3ia

Ans'er =blind 0ias are used to connect an inner layer to either the top or bottom

layer( A buried 0ia is used %or connecting t'o inner layers( It does not go either to

the top or the bottom layer( A regular 0ia #di%%erent %rom the blind and the buried

0ia connects the top and the bottom layer and also passes through the inner

layers(

Do not stop here( Go ahead and dra' the diagram o% the blind and the buried 0ia(

73. What is the use of a decoupling capacitor?

Ans'er > A decoupling capacitor is used to smoothen the po'er supply noise( It

should be placed as close to the ICs %or 'hich it is intended as possible(

74. What is %8C? What 9ind of %8C errors you find in PCB %esign?

Ans'er > DRC stands %or Design Rule checking( A PCB should not ha0e any

electrical %ailure be%ore 'e tape out %or the manu%acturing( Common DRC errors

include trace to pad 0iolation pad to pad 0iolation component keep out

0iolation( Additionally a PCB Design may ha0e high speed design rule related

constraints( ,his may include length matching constraints di%%erential signal

length matching constraint(

7. What are the things you should do you ensure design for compliance

for :;1?

Ans'er > We should use common mode chokes %or all cables connectors( ,he

common mode chokes should be placed as close to the connector as possible(

,he Po'er and ground planes should be as close to each other as possible( ,he

&igh speed signal should re%er to a ground or po'er plane and should not cross

a split plane( Stitching capacitor should be used in case split plane is used(

7!.- large thermal pad is di3ided into four sections? What is the use of it?

Ans'er > ,he open area bet'een the ? sections lead to escape o% the gases

during the re%lo' and soldering process( It leads to better manu%acturability(

7". *he width of a trace is increased? Will its characteristic impedance

increase of decrease?

Ans'er > ,he Capacitance per unit length o% the trace increases and there%ore

the characteristic impedance o% the trace decreases(

,erilog inter3iew <uestions and answers

C"!S inter0ie' -uestions(

$/ What is latch up?

Latch=up pertains to a %ailure mechanism 'herein a parasitic thyristor #such as a

parasitic silicon controlled recti%ier or SCR$ is inad0ertently created 'ithin a

circuit causing a high amount o% current to continuously %lo' through it once it is

accidentally triggered or turned on( Depending on the circuits in0ol0ed the

amount o% current %lo' produced by this mechanism can be large enough to

result in permanent destruction o% the de0ice due to electrical o0erstress #4!S$

2/ why is =-=% gate preferred o3er =>8 gate for fa&rication?

+A+D is a better gate %or design than +!R because at the transistor le0el the

mobility o% electrons is normally three times that o% holes compared to +!R and

thus the +A+D is a %aster gate(

Additionally the gate=leakage in +A+D structures is much lo'er( I% you consider

tJphl and tJplh delays you 'ill %ind that it is more symmetric in case o% +A+D

# the delay pro%ile$ but %or +!R one delay is much higher than the

other#ob0iously tJplh is higher since the higher resistance p mosFs are in series

connection 'hich again increases the resistance$(

3/ What is =oise ;argin? :?plain the procedure to determine =oise ;argin

,he minimum amount o% noise that can be allo'ed on the input stage %or 'hich

the output 'ill not be e%%ected(

4/ :?plain si)ing of the in3erter?

In order to dri0e the desired load capacitance 'e ha0e to increase the si/e

#'idth$ o% the in0erters to get an optimi/ed per%ormance(

/ How do you si)e =;>+ and P;>+ transistors to increase the threshold

3oltage?

!/ What is =oise ;argin? :?plain the procedure to determine =oise

;argin?

,he minimum amount o% noise that can be allo'ed on the input stage %or 'hich

the output 'ill not be e%%ected(

"/ What happens to delay if you increase load capacitance?

Delay increases(

#/ What happens to delay if we include a resistance at the output of a

C;>+ circuit?

Increases( #RC delay$

4/What are the limitations in increasing the power supply to reduce delay?

,he delay can be reduced by increasing the po'er supply but i% 'e do so the

heating e%%ect comes because o% e)cessi0e po'er to compensate this 'e ha0e

to increase the die si/e 'hich is not practical(

$6/ How does 8esistance of the metal lines 3ary with increasing thic(ness

and increasing length?

R H # Kl$ @ A(

$$/ For C;>+ logic5 gi3e the 3arious techni<ues you (now to minimi)e

power consumption?

Po'er dissipationHCE9% %rom this minimi/e the load capacitance dc 0oltage and

the operating %re-uency(

$2/ What is Charge +haring? :?plain the Charge +haring pro&lem while

sampling data from a Bus?

In the serially connected +"!S logic the input capacitance o% each gate shares

the charge 'ith the load capacitance by 'hich the logical le0els drastically

mismatched than that o% the desired once( ,o eliminate this load capacitance

must be 0ery high compared to the input capacitance o% the gates #appro)imately

76 times$(

$3/Why do we gradually increase the si)e of in3erters in &uffer design?

Why not gi3e the output of a circuit to one large in3erter?

Because it can not dri0e the output load straight a'ay so 'e gradually increase

the si/e to get an optimi/ed per%ormance(

$4/ What is 2atch @p? :?plain 2atch @p with cross section of a C;>+

1n3erter. How do you a3oid 2atch @p?

Latch=up is a condition in 'hich the parasitic components gi0e rise to the

4stablishment o% lo' resistance conducting path bet'een EDD and ESS 'ith

Disastrous results(

$/ 0i3e the e?pression for C;>+ switching power dissipation?

CE9

$!/ what is Body :ffect?

In general multiple "!S de0ices are made on a common substrate( As a result

the substrate 0oltage o% all de0ices is normally e-ual( &o'e0er 'hile connecting

the de0ices serially this may result in an increase in source=to=substrate 0oltage

as 'e proceed 0ertically along the series chain #Esb7H6 Esb9 6$(Which results

Eth9LEth7(

$"/ Why is the su&strate in =;>+ connected to 0round and in P;>+ to

,%%?

'e try to re0erse bias not the channel and the substrate but 'e try to maintain

the drainsource 2unctions re0erse biased 'ith respect to the substrate so that 'e

dont loose our current into the substrate(

$#/ What is the fundamental difference &etween a ;>+F:* and BA*?

In "!S*4, current %lo' is either due to electrons #n=channel "!S$ or due to

holes#p=channel "!S$ = In BM, 'e see current due to both the carriers((

4lectrons and holes( BM, is a current controlled de0ice and "!S*4, is a 0oltage

controlled de0ice(

$4/ Which transistor has higher gain. BA* or ;>+ and why?

BM, has higher gain because it has higher transconductance(,his is because the

current in BM, is e)ponentially dependent on input 'here as in "!S*4, it is

s-uare la'(

26/ Why do we gradually increase the si)e of in3erters in &uffer design

when trying to dri3e a high capaciti3e load? Why not gi3e the output of a

circuit to one large in3erter?

We cannot use a big in0erter to dri0e a large output capacitance because 'ho

'ill dri0e the big in0erter1 ,he signal that has to dri0e the output cap 'ill no' see

a larger gate capacitance o% the BIG in0erter( So this results in slo' raise or %all

times (A unit in0erter can dri0e appro)imately an in0erter that3s ? times bigger in

si/e( So say 'e need to dri0e a cap o% 8? unit in0erter then 'e try to keep the

si/ing like say 7?788? so that each in0erter sees a same ratio o% output to input

cap( ,his is the prime reason behind going %or progressi0e si/ing(

2$/1n C;>+ technology5 in digital design5 why do we design the si)e of

pmos to &e higher than the nmos.What determines the si)e of pmos wrt

nmos. *hough this is a simple <uestion try to list all the reasons possi&le?

In P"!S the carriers are holes 'hose mobility is lessN aprro) hal% O than the

electrons the carriers in +"!S( ,hat means P"!S is slo'er than an +"!S( In

C"!S technology nmos helps in pulling do'n the output to ground ann P"!S

helps in pulling up the output to Edd( I% the si/es o% P"!S and +"!S are the

same then P"!S takes long time to charge up the output node( I% 'e ha0e a

larger P"!S than there 'ill be more carriers to charge the node -uickly and

o0ercome the slo' nature o% P"!S ( Basically 'e do all this to get e-ual rise and

%all times %or the output node(

22/ Why P;>+ and =;>+ are si)ed e<ually in a *ransmission 0ates?

In ,ransmission Gate P"!S and +"!S aid each other rather competing 'ith

each other( ,hatFs the reason 'hy 'e need not si/e them like in C"!S( In

C"!S design 'e ha0e +"!S and P"!S competing 'hich is the reason 'e try

to si/e them proportional to their mobility(

23/ -ll of us (now how an in3erter wor(s. What happens when the P;>+

and =;>+ are interchanged with one another in an in3erter?

I ha0e seen similar .s in some o% the discussions( I% the source ; drain also

connected properly(((it acts as a bu%%er( But suppose input is logic 7 !@P 'ill be

degraded 7 Similarly degraded 6P

24/- good <uestion on 2ayouts. 0i3e important %esign techni<ues you

would follow when doing a 2ayout for %igital Circuits?

a$In digital design decide the height o% standard cells you 'ant to layout(It

depends upon ho' big your transistors 'ill be(&a0e reasonable 'idth %or EDD

and G+D metal paths("aintaining uni%orm &eight %or all the cell is 0ery important

since this 'ill help you use place route tool easily and also incase you 'ant to do

manual connection o% all the blocks it sa0es on lot o% area(

b$Bse one metal in one direction only ,his does not apply %or metal 7( Say you

are using metal 9 to do hori/ontal connections then use metal 5 %or 0ertical

connections metal? %or hori/ontal metal < 0ertical etc(((

c$Place as many substrate contact as possible in the empty spaces o% the layout(

d$Do not use poly o0er long distances as it has huge resistances unless you

ha0e no other choice(

e$Bse %ingered transistors as and 'hen you %eel necessary(

%$,ry maintaining symmetry in your design( ,ry to get the design in BI, Sliced

manner(

2/What is metasta&ility? WhenBwhy it will occur?%ifferent ways to a3oid

this?

"etastable stateD A un=kno'n state in bet'een the t'o logical kno'n states(,his

'ill happen i% the !@P cap is not allo'ed to charge@discharge %ully to the re-uired

logical le0els(

!ne o% the cases isD I% there is a setup time 0iolation metastability 'ill occur,o

a0oid this a series o% **s is used #normally 9 or 5$ 'hich 'ill remo0e the

intermediate states(

2!/2et - and B &e two inputs of the =-=% gate. +ay signal - arri3es at the

=-=% gate later than signal B. *o optimi)e delay of the two series =;>+

inputs - and B which one would you place near to the output?

,he late coming signals are to be placed closer to the output node ie A should go

to the nmos that is closer to the output(

%igital design inter3iew <uestions C answers.

$/ :?plain a&out setup time and hold time5 what will happen if there is

setup time and hold tine 3iolation5 how to o3ercome this?

Set up time is the amount o% time be%ore the clock edge that the input signal

needs to be stable to guarantee it is accepted properly on the clock edge(

&old time is the amount o% time a%ter the clock edge that same input signal has to

be held be%ore changing it to make sure it is sensed properly at the clock edge(

Whene0er there are setup and hold time 0iolations in any %lip=%lop it enters a

state 'here its output is unpredictableD this state is kno'n as metastable state

#-uasi stable state$P at the end o% metastable state the %lip=%lop settles do'n to

either F7F or F6F( ,his 'hole process is kno'n as metastability

2/ What is s(ew5 what are pro&lems associated with it and how to minimi)e

it?

In circuit design clock ske' is a phenomenon in synchronous circuits in 'hich

the clock signal #sent %rom the clock circuit$ arri0es at di%%erent components at

di%%erent times(

,his is typically due to t'o causes( ,he %irst is a material %la' 'hich causes a

signal to tra0el %aster or slo'er than e)pected( ,he second is distanceD i% the

signal has to tra0el the entire length o% a circuit it 'ill likely #depending on the

circuitFs si/e$ arri0e at di%%erent parts o% the circuit at di%%erent times( Clock ske'

can cause harm in t'o 'ays( Suppose that a logic path tra0els through

combinational logic %rom a source %lip=%lop to a destination %lip=%lop( I% the

destination %lip=%lop recei0es the clock tick later than the source %lip=%lop and i% the

logic path delay is short enough then the data signal might arri0e at the

destination %lip=%lop be%ore the clock tick destroying there the pre0ious data that

should ha0e been clocked through( ,his is called a hold 0iolation because the

pre0ious data is not held long enough at the destination %lip=%lop to be properly

clocked through( I% the destination %lip=%lop recei0es the clock tick earlier than the

source %lip=%lop then the data signal has that much less time to reach the

destination %lip=%lop be%ore the ne)t clock tick( I% it %ails to do so a setup 0iolation

occurs so=called because the ne' data 'as not set up and stable be%ore the

ne)t clock tick arri0ed( A hold 0iolation is more serious than a setup 0iolation

because it cannot be %i)ed by increasing the clock period(

Clock ske' i% done right can also bene%it a circuit( It can be intentionally

introduced to decrease the clock period at 'hich the circuit 'ill operate correctly

and@or to increase the setup or hold sa%ety margins( ,he optimal set o% clock

delays is determined by a linear program in 'hich a setup and a hold constraint

appears %or each logic path( In this linear program /ero clock ske' is merely a

%easible point(

Clock ske' can be minimi/ed by proper routing o% clock signal #clock distribution

tree$ or putting 0ariable delay bu%%er so that all clock inputs arri0e at the same

time

3/ What is slac(?

FSlackF is the amount o% time you ha0e that is measured %rom 'hen an e0ent

Factually happensF and 'hen it Fmust happenF(( ,he term Factually happensF can

also be taken as being a predicted time %or 'hen the e0ent 'ill Factually happenF(

When something Fmust happenF can also be called a FdeadlineF so another

de%inition o% slack 'ould be the time %rom 'hen something Factually happensF #call

this ,act$ until the deadline #call this ,dead$(

Slack H ,dead = ,act(

+egati0e slack implies that the Factually happenF time is later than the FdeadlineF

time(((in other 'ords itFs too late and a timing 0iolation((((you ha0e a timing

problem that needs some attention(

4/ What is glitch? What causes it .e?plain with wa3eform/? How to

o3ercome it?

,he %ollo'ing %igure sho's a synchronous alternati0e to the gated clock using a

data path( ,he %lip=%lop is clocked at e0ery clock cycle and the data path is

controlled by an enable( When the enable is Lo' the multiple)er %eeds the

output o% the register back on itsel%( When the enable is &igh ne' data is %ed to

the %lip=%lop and the register changes its state

/ 0i3en only two ?or gates one must function as &uffer and another as

in3erter?

,ie one o% )or gates input to 7 it 'ill act as in0erter(

,ie one o% )or gates input to 6 it 'ill act as bu%%er(

!/ What is difference &etween latch and flipflop?

,he main di%%erence bet'een latch and ** is that latches are le0el sensiti0e 'hile

** are edge sensiti0e( ,hey both re-uire the use o% clock signal and are used in

se-uential logic( *or a latch the output tracks the input 'hen the clock signal is

high so as long as the clock is logic 7 the output can change i% the input also

changes( ** on the other hand 'ill store the input only 'hen there is a

rising@%alling edge o% the clock(

"/ Build a 4'$ mu? using only 2'$ mu??

Di%%erence bet'een heap and stack1

,he Stack is more or less responsible %or keeping track o% 'hatFs e)ecuting in our

code #or 'hatFs been CcalledC$( ,he &eap is more or less responsible %or keeping

track o% our ob2ects #our data 'ell((( most o% it = 'eFll get to that later($(

,hink o% the Stack as a series o% bo)es stacked one on top o% the ne)t( We keep

track o% 'hatFs going on in our application by stacking another bo) on top e0ery

time 'e call a method #called a *rame$( We can only use 'hatFs in the top bo) on

the stack( When 'eFre done 'ith the top bo) #the method is done e)ecuting$ 'e

thro' it a'ay and proceed to use the stu%% in the pre0ious bo) on the top o% the

stack( ,he &eap is similar e)cept that its purpose is to hold in%ormation #not keep

track o% e)ecution most o% the time$ so anything in our &eap can be accessed at

any time( With the &eap there are no constraints as to 'hat can be accessed

like in the stack( ,he &eap is like the heap o% clean laundry on our bed that 'e

ha0e not taken the time to put a'ay yet = 'e can grab 'hat 'e need -uickly( ,he

Stack is like the stack o% shoe bo)es in the closet 'here 'e ha0e to take o%% the

top one to get to the one underneath it(

4/ %ifference &etween mealy and moore state machine?

A$ "ealy and "oore models are the basic models o% state machines( A state

machine 'hich uses only 4ntry Actions so that its output depends on the state

is called a "oore model( A state machine 'hich uses only Input Actions so that

the output depends on the state and also on inputs is called a "ealy model( ,he

models selected 'ill in%luence a design but there are no general indications as to

'hich model is better( Choice o% a model depends on the application e)ecution

means #%or instance hard'are systems are usually best reali/ed as "oore

models$ and personal pre%erences o% a designer or programmer

B$ "ealy machine has outputs that depend on the state and input #thus the *S"

has the output 'ritten on edges$

"oore machine has outputs that depend on state only #thus the *S" has the

output 'ritten in the state itsel%(

Ad0 and Disad0

In "ealy as the output 0ariable is a %unction both input and state changes o%

state o% the state 0ariables 'ill be delayed 'ith respect to changes o% signal le0el

in the input 0ariables there are possibilities o% glitches appearing in the output

0ariables( "oore o0ercomes glitches as output dependent on only states and not

the input signal le0el(

All o% the concepts can be applied to "oore=model state machines because any

"oore state machine can be implemented as a "ealy state machine although

the con0erse is not true(

"oore machineD the outputs are properties o% states themsel0es((( 'hich means

that you get the output a%ter the machine reaches a particular state or to get

some output your machine has to be taken to a state 'hich pro0ides you the

output(,he outputs are held until you go to some other state "ealy machineD

"ealy machines gi0e you outputs instantly that is immediately upon recei0ing

input but the output is not held a%ter that clock cycle(

$6/ %ifference &etween onehot and &inary encoding?

Common classi%ications used to describe the state encoding o% an *S" are

Binary #or highly encoded$ and !ne hot(

A binary=encoded *S" design only re-uires as many %lip=%lops as are needed to

uni-uely encode the number o% states in the state machine( ,he actual number o%

%lip=%lops re-uired is e-ual to the ceiling o% the log=base=9 o% the number o% states

in the *S"(

A onehot *S" design re-uires a %lip=%lop %or each state in the design and only

one %lip=%lop #the %lip=%lop representing the current or ChotC state$ is set at a time in

a one hot *S" design( *or a state machine 'ith := 78 states a binary *S" only

re-uires ? %lip=%lops 'hile a onehot *S" re-uires a %lip=%lop %or each state in the

design

*PGA 0endors %re-uently recommend using a onehot state encoding style

because %lip=%lops are plenti%ul in an *PGA and the combinational logic re-uired

to implement a onehot *S" design is typically smaller than most binary encoding

styles( Since *PGA per%ormance is typically related to the combinational logic

si/e o% the *PGA design onehot *S"s typically run %aster than a binary encoded

*S" 'ith larger combinational logic blocks

$$/ What are different ways to synchroni)e &etween two cloc( domains?

$2/ How to calculate ma?imum operating fre<uency?

$3/ How to find out longest path?

Qou can %ind ans'er to this in timing(ppt o% presentations section on this site

$4/ %raw the state diagram to output a D$D for one cycle if the se<uence

D6$$6D sho's up #the leading 6s cannot be used in more than one se-uence$1

$/ How to achie3e $#6 deree e?act phase shift?

+e0er tell using in0erter

a$ dcmFs an inbuilt resource in most o% %pga can be con%igured to get 7I6 degree

phase shi%t(

b$ Bu%gds that is di%%erential signaling bu%%ers 'hich are also inbuilt resource o%

most o% *PGA can be used(

$!/ What is significance of ras and cas in +%8-;?

SDRA" recei0es its address command in t'o address 'ords(

It uses a multiple) scheme to sa0e input pins( ,he %irst address 'ord is latched

into the DRA" chip 'ith the ro' address strobe #RAS$(

*ollo'ing the RAS command is the column address strobe #CAS$ %or latching the

second address 'ord(

Shortly a%ter the RAS and CAS strobes the stored data is 0alid %or reading(

$"/ *ell some of applications of &uffer?

a$,hey are used to introduce small delays

b$,hey are used to eliminate cross talk caused due to inter electrode capacitance

due to close routing(

c$,hey are used to support high %anoutegDbu%g

$#/ 1mplement an -=% gate using mu??

,his is the basic -uestion that many inter0ie'ers ask( %or and gate gi0e one

input as select line incase i% u r gi0ing b as select line connect one input to logic

F6F and other input to a(

7:$ What 'ill happen i% contents o% register are shi%ter le%t right1

It is 'ell kno'n that in le%t shi%t all bits 'ill be shi%ted le%t and LSB 'ill be

appended 'ith 6 and in right shi%t all bits 'ill be shi%ted right and "SB 'ill be

appended 'ith 6 this is a straight%or'ard ans'er

What is e)pected is in a le%t shi%t 0alue gets "ultiplied by 9 egDconsider

6666J7776H7? a le%t shi%t 'ill make it 6667J776H9I it the same %ashion right

shi%t 'ill Di0ide the 0alue by 9(

26/ 0i3en the following F1F> and rules5 how deep does the F1F> need to &e

to pre3ent underflow or o3erflow?

RBL4SD

7$ %re-uency#clkJA$ H %re-uency#clkJB$ @ ?

9$ period#enJB$ H period#clkJA$ K 766

5$ dutyJcycle#enJB$ H 9<R

Assume clkJB H 766"&/ #76ns$

*rom #7$ clkJA H 9<"&/ #?6ns$

*rom #9$ period#enJB$ H ?6ns K ?66 H ?666ns but 'e only output %or

7666nsdue to #5$ so 5666ns o% the enable 'e are doing no output 'ork(

,here%ore *I*! si/e H 5666ns@?6ns H A< entries

2$/ %esign a fourEinput =-=% gate using only twoEinput =-=% gates.

AD Basically you can tie the inputs o% a +A+D gate together to get an in0erter

so(((

22/ %ifference &etween +ynchronous and -synchronous reset?

Synchronous reset logic 'ill synthesi/e to smaller %lip=%lops particularly i% the

reset is gated 'ith the logic generating the d=input( But in such a case the

combinational logic gate count gro's so the o0erall gate count sa0ings may not

be that signi%icant(

,he clock 'orks as a %ilter %or small reset glitchesP ho'e0er i% these glitches

occur near the acti0e clock edge the *lip=%lop could go metastable( In some

designs the reset must be generated by a set o% internal conditions( A

synchronous reset is recommended %or these types o% designs because it 'ill

%ilter the logic e-uation glitches bet'een clocks(

Disad0antages o% synchronous resetD

Problem 'ith synchronous resets is that the synthesis tool cannot easily

distinguish the reset signal %rom any other data signal(

Synchronous resets may need a pulse stretcher to guarantee a reset pulse 'idth

'ide enough to ensure reset is present during an acti0e edge o% the clock Ni% you

ha0e a gated clock to sa0e po'er the clock may be disabled coincident 'ith the

assertion o% reset( !nly an asynchronous reset 'ill 'ork in this situation as the

reset might be remo0ed prior to the resumption o% the clock(

Designs that are pushing the limit %or data path timing cannot a%%ord to ha0e

added gates and additional net delays in the data path due to logic inserted to

handle synchronous resets(

Asynchronous resetD

,he biggest problem 'ith asynchronous resets is the reset release also called

reset remo0al( Bsing an asynchronous reset the designer is guaranteed not to

ha0e the reset added to the data path( Another ad0antage %a0oring asynchronous

resets is that the circuit can be reset 'ith or 'ithout a clock present(

Disad0antages o% asynchronous resetD ensure that the release o% the reset can

occur 'ithin one clock period( i% the release o% the reset occurred on or near a

clock edge such that the %lip=%lops 'ent metastable(

23/ Why are most interrupts acti3e low?

,his ans'ers 'hy most signals are acti0e lo'

I% you consider the transistor le0el o% a module acti0e lo' means the capacitor in

the output terminal gets charged or discharged based on lo' to high and high to

lo' transition respecti0ely( 'hen it goes %rom high to lo' it depends on the pull

do'n resistor that pulls it do'n and it is relati0ely easy %or the output capacitance

to discharge rather than charging( hence people pre%er using acti0e lo' signals(

24/ 0i3e two ways of con3erting a two input =-=% gate to an in3erter?

#a$ short the 9 inputs o% the nand gate and apply the single input to it(

#b$ Connect the output to one o% the input and the other to the input signal(

2/ What are set up time C hold time constraints? What do they signify?

Which one is critical for estimating ma?imum cloc( fre<uency of a circuit?

set up timeD = the amount o% time the data should be stable be%ore the application

o% the clock signal 'here as the hold time is the amount o% time the data should

be stable a%ter the application o% the clock( Setup time signi%ies ma)imum delay

constraintsP hold time is %or minimum delay constraints( Setup time is critical %or

establishing the ma)imum clock %re-uency(

2!/ %ifferences &etween %E2atch and % flipEflop?

D=latch is le0el sensiti0e 'hereas %lip=%lop is edge sensiti0e( *lip=%lops are made

up o% latches(

2"/ What is a multiple?er?

Is combinational circuit that selects binary in%ormation %rom one o% many input

lines and directs it to a single output line( #9n HLn$(

2#/ How can you con3ert an +8 FlipEflop to a A9 FlipEflop?

By gi0ing the %eedback 'e can con0ert i(e S.HLS and .HLR( &ence the S and R

inputs 'ill act as M and T respecti0ely(

24/ How can you con3ert the A9 FlipEflop to a % FlipEflop?

By connecting the M input to the T through the in0erter(

36/ What is 8aceEaround pro&lem? How can you rectify it?

,he clock pulse that remains in the 7 state 'hile both M and T are e-ual to 7 'ill

cause the output to complement again and repeat complementing until the pulse

goes back to 6 this is called the race around problem( ,o a0oid this undesirable

operation the clock pulse must ha0e a time duration that is shorter than the

propagation delay time o% the *=* this is restricti0e so the alternati0e is master=

sla0e or edge=triggered construction(

3$/How do you detect if two #E&it signals are same?

U!R each bits o% A 'ith B #%or e(g( AN6O )or BN6O $ and so on(the o@p o% I )or gates

are then gi0en as i@p to an I=i@p nor gate( i% o@p is 7 then AHB(

32/" &it ring counterFs initial state is 6$666$6. -fter how many cloc( cycles

will it return to the initial state?

8 cycles

33/ Con3ert %EFF into di3ide &y 2. .not latch/ What is the ma? cloc(

fre<uency the circuit can handle5 gi3en the following information?

,JsetupH 8nS ,Jhold H 9nS ,Jpropagation H 76nS

CircuitD Connect .bar to D and apply the clk at clk o% D** and take the !@P at .(

It gi0es %re-@9( "a)( *re- o% operationD 7@ #propagation delayVsetup time$ H

7@78ns H 89(< "&/

34/0uys this is the &asic <uestion as(ed most fre<uently. %esign all the

&asic gates.=>*5-=%5>85=-=%5=>85G>85G=>8/ using 2'$ ;ultiple?er?

Bsing 9D7 "u) #9 inputs 7 output and a select line$

#a$ +!,

Gi0e the input at the select line and connect I6 to 7 ; I7 to 6( So i% A is 7 'e 'ill

get I7 that is 6 at the !@P(

#b$ A+D

Gi0e input A at the select line and 6 to I6 and B to I7( !@p is A ; B

#c$ !R

Gi0e input A at the select line and 7 to I7 and B to I6( !@p 'ill be A W B

#d$ +A+D

A+D V +!, implementations together

#e$ +!R

!R V +!, implementations together

#%$ U!R

A at the select line B at I6 and XB at I7( XB can be obtained %rom #a$ #g$ U+!R

A at the select line B at I7 and XB at I6

3/= num&er of G=>8 gates are connected in series such that the = inputs

.-65-$5-2....../ are gi3en in the following way' -6 C -$ to first G=>8 gate

and -2 C >BP of First G=>8 to second G=>8 gate and so on..... =th G=>8

gates output is final output. How does this circuit wor(? :?plain in detail?

I% +H!dd the circuit acts as e0en parity detector ie the output 'ill 7 i% there are

e0en number o% 7Fs in the + input(((,his could also be called as odd parity

generator since 'ith this additional 7 as output the total number o% 7Fs 'ill be

!DD(

I% +H40en 2ust the opposite it 'ill be !dd parity detector or 40en Parity

Generator(

58$ An assembly line has 5 %ail sa%e sensors and one emergency shutdo'n

s'itch( ,he line should keep mo0ing unless any o% the %ollo'ing conditions ariseD

#i$ I% the emergency s'itch is pressed

#ii$ I% the senor7 and sensor9 are acti0ated at the same time(

#iii$ I% sensor 9 and sensor5 are acti0ated at the same time(

#i0$ I% all the sensors are acti0ated at the same time

Suppose a combinational circuit %or abo0e case is to be implemented only 'ith

+A+D Gates( &o' many minimum number o% 9 input +A+D gates are re-uired1

+o o% 9=input +A+D Gates re-uired H 8 Qou can try the 'hole implementation(

5A$ Design a circuit that calculates the s-uare o% a number1 It should not use any

multiplier circuits( It should use "ultiple)ers and other logic1

,his is interesting((((

7Y9H6V7H7

9Y9H7V5H?

5Y9H?V<H:

?Y9H:VAH78

<Y9H78V:H9<

and so on( See a pattern yet1,o get the ne)t s-uare all you ha0e to do is add

the ne)t odd number to the pre0ious s-uare that you %ound(See ho' 75<A and

%inally : are added( WouldnFt this be a possible solution to your -uestion since it

only 'ill use a counter multiple)er and a couple o% adders1 It seems it 'ould

take n clock cycles to calculate s-uare o% n(

5I$ &o' 'ill you implement a *ull subtractor %rom a *ull adder1

All the bits o% subtrahend should be connected to the )or gate( !ther input to the

)or being one(,he input carry bit to the %ull adder should be made 7( ,hen the %ull

adder 'orks like a %ull subtractor

34/- 3ery good inter3iew <uestion... What is difference &etween setup and

hold time.

,he inter0ie'er 'as looking %or one speci%ic reason and its really a good ans'er

too((,he hint is hold time doesnFt depend on clock 'hy is it so(((1

Setup 0iolations are related to t'o edges o% clock i mean you can 0ary the clock

%re-uency to correct setup 0iolation( But %or hold time you are only concerned

'ith one edge and does not basically depend on clock %re-uency(

46/ 1n a 3E&it AohnsonFs counter what are the unused states?

9#po'er n$=9n is the one used to %ind the unused states in 2ohnson counter(

So %or a 5=bit counter it is I=8H9(Bnused statesH9( the t'o unused states are 676

and 767

?7$ ,he -uestion is to design minimal hard'are system 'hich encrypts I=bit

parallel data( A synchroni/ed clock is pro0ided to this system as 'ell( ,he output

encrypted data should be at the same rate as the input data but no necessarily

'ith the same phase(

,he encryption system is centered around a memory de0ice that per%orm a LB,

#Look=Bp ,able$ con0ersion( ,his memory %unctionality can be achie0ed by using

a PR!" 4PR!" *LAS& and etc( ,he de0ice contains an encryption code

'hich may be burned into the de0ice 'ith an e)ternal programmer( In encryption

operation the dataJin is an address pointer into a memory cell and the

combinatorial logic generates the control signals( ,his creates a read access

%rom the memory( ,hen the memory de0ice goes to the appropriate address and

outputs the associate data( ,his data represent the dataJin a%ter encryption( ?7$

What is an L*SR (List a %e' o% its industry applications(1

L*SR is a linear %eedback shi%t register 'here the input bit is dri0en by a linear

%unction o% the o0erall shi%t register 0alue( Coming to industrial applications as %ar

as I kno' it is used %or encryption and decryption and in BIS,#built=in=sel%=test$

based applications((

42/ What is false path?how it determine in c(t? What the effect of false path

in c(t?

By timing all the paths in the circuit the timing analy/er can determine all the

critical paths in the circuit( &o'e0er the circuit may ha0e %alse paths 'hich are

the paths in the circuit 'hich are ne0er e)ercised during normal circuit operation

%or any set o% inputs(

An e)ample o% a %alse path is sho'n in %igure belo'( ,he path going %rom the

input A o% the %irst "BU through the combinational logic out through the B input o%

the second "BS is a %alse path( ,his path can ne0er be acti0ated since i% the A

input o% the %irst "BU is acti0ated then Sel line 'ill also select the A input o% the

second "BU(

S,A #Static ,iming Analysis$ tools are able to identi%y simple %alse pathsP

ho'e0er they are not able to identi%y all the %alse paths and sometimes report

%alse paths as critical paths( Remo0al o% %alse paths makes circuit testable and its

timing per%ormance predictable #sometimes %aster$

43/Consider two similar processors5 one with a cloc( s(ew of $66ps and

other with a cloc( s(ew of 6ps. Which one is li(ely to ha3e more power?

Why?

Clock ske' o% <6ps is more likely to ha0e clock po'er( ,his is because it is likely

that lo'=ske' processor has better designed clock tree 'ith more po'er%ul and

number o% bu%%ers and o0erheads to make ske' better(

44/ What are multiEcycle paths?

"ulti=cycle paths are paths bet'een registers that take more than one clock

cycle to become stable(

*or e)( Analy/ing the design sho'n in %ig belo' sho's that the output SI+@C!S

re-uires ? clock=cycles a%ter the input A+GL4 is latched in( ,his means that the

combinatorial block #the Bnrolled Cordic$ can take up to ? clock periods #9<"&/$

to propagate its result( Place and Route tools are capable o% %i)ing multi=cycle

paths problem(

4/Hou ha3e two counters counting upto $!5 &uilt from negedge %FF 5 First

circuit is synchronous and second is DrippleD .cascading/5 Which circuit

has a less propagation delay? Why?

,he synchronous counter 'ill ha0e lesser delay as the input to each %lop is

readily a0ailable be%ore the clock edge( Whereas the cascade counter 'ill take

long time as the output o% one %lop is used as clock to the other( So the delay 'ill

be propagating( *or 4gD 78 state counter H ? bit counter H ? *lip %lops Let 76ns

be the delay o% each %lop ,he 'orst case delay o% ripple counter H 76 K ? H ?6ns

,he delay o% synchronous counter H 76ns only(#Delay o% 7 %lop$

4!/ what is difference &etween 8-; and F1F>?

*I*! does not ha0e address lines

Ram is used %or storage purpose 'here as %i%o is used %or synchroni/ation

purpose i(e( 'hen t'o peripherals are 'orking in di%%erent clock domains then 'e

'ill go %or %i%o(

4"/*he circle can rotate cloc(wise and &ac(. @se minimum hardware to

&uild a circuit to indicate the direction of rotating.?

9 sensors are re-uired to %ind out the direction o% rotating( ,hey are placed like at

the dra'ing( !ne o% them is connected to the data input o% D %lip=%lopand a

second one = to the clock input( I% the circle rotates the 'ay clock sensor sees the

light %irst 'hile D input #second sensor$ is /ero = the output o% the %lip=%lop e-uals

/ero and i% D input sensor C%iresC %irst = the output o% the %lip=%lop becomes high(

4#/ %raw timing diagrams for following circuit.?

44/1mplement the following circuitsD

#a$ 5 input +A+D gate using min no o% 9 input +A+D Gates

#b$ 5 input +!R gate using min no o% 9 inpur +!R Gates

#c$ 5 input U+!R gate using min no o% 9 inpur U+!R Gates

Assuming 5 inputs ABC1

5 input +A+DD

Connect D

a$ A and B to the %irst +A+D gate

b$ !utput o% %irst +and gate is gi0en to the t'o inputs o% the second +A+D gate

#this basically reali/es the in0erter %unctionality$

c$ !utput o% second +A+D gate is gi0en to the input o% the third +A+D gate

'hose other input is C

##A +A+D B$ +A+D #A +A+D B$$ +A+D C ,hus can be implemented using F5F

9=input +A+D gates( I guess this is the minimum number o% gates that need to be

used(

5 input +!RD

Same as abo0e 2ust interchange +A+D 'ith +!R ##A +!R B$ +!R #A +!R B$$

+!R C

5 input U+!RD

Same as abo0e e)cept the inputs %or the second U+!R gate !utput o% the %irst

U+!R gate is one o% the inputs and connect the second input to ground or logical

F6F ##A U+!R B$ U+!R 6$$ U+!R C

<6$ Is it possible to reduce clock ske' to /ero1 4)plain your ans'er 1

40en though there are clock layout strategies #&=tree$ that can in theory reduce

clock ske' to /ero by ha0ing the same path length %rom each %lip=%lop %rom the

pll process 0ariations in R and C across the chip 'ill cause clock ske' as 'ell

as a pure &=,ree scheme is not practical #consumes too much area$(

$/%esign a F+; .Finite +tate ;achine/ to detect a se<uence $6$$6?

2/Con3ert %EFF into di3ide &y 2. .not latch/? What is the ma? cloc(

fre<uency of the circuit 5 gi3en the following information?

,JsetupH 8nS

,Jhold H 9nS

,Jpropagation H 76nS

CircuitD

Connect .bar to D and apply the clk at clk o% D** and take the !@P at .( It gi0es

%re-@9(

"a)( *re- o% operationD

7@ #propagation delayVsetup time$ H 7@78ns H 89(< "&/

3/0i3e the circuit to e?tend the falling edge of the input &y 2 cloc( pulses?

*he wa3eforms are shown in the following figure.

4/ For the Circuit +hown &elow5 What is the ;a?imum Fre<uency of

>peration? -re there any hold time 3iolations for FF2? 1f yes5 how do you

modify the circuit to a3oid them?

,he minimum time period H 5V9V#7V7V7$ H Ins "a)imum *re-uency H 7@InH

79<"&/(

And there is a hold time 0iolation in the circuit because o% %eedback i% you

obser0e tc-9VA+D gate delay is less than thold9,o a0oid this 'e need to use

e0en number o% in0erters#bu%%ers$( &ere 'e need to use 9 in0erters each 'ith a

delay o% 7ns( then the hold time 0alue e)actly meets(

/%esign a %Elatch using .a/ using 2'$ ;u? .&/ from +E8 2atch ?

!/How to implement a ;aster +la3e flip flop using a 2 to $ mu??

"/how many 2 input ?orFs are needed to inplement $! input parity

generator ?

It is al'ays n=7 Where n is number o% inputs(So 78 input parity generator 'ill

re-uire 7< t'o input )orFs (

#/%esign a circuit for finding the 4Fs compliment of a BC% num&er using 4E

&it &inary adder and some e?ternal logic gates?

:Fs compliment is nothing but subracting the gi0en no %rom :(So using a ? bit

binary adder 'e can 2ust subract the gi0en binary no %rom 7667#i(e( :$(&ere 'e

can use the 9Fs compliment method addition(

4/ What is %ifference &etween write&ac( and write through cache?

A caching method in 'hich modi%ications to data in the cache arenFt copied to the

cache source until absolutely necessary( Write=back caching is a0ailable on

many microprocessors including all Intel processors since the I6?I8( With

these microprocessors data modi%ications to data stored in the L7 cache arenFt

copied to main memory until absolutely necessary( In contrast a 'rite=through

cache per%orms all 'rite operations in parallel == data is 'ritten to main memory

and the L7 cache simultaneously( Write=back caching yields some'hat better

per%ormance than 'rite=through caching because it reduces the number o% 'rite

operations to main memory( With this per%ormance impro0ement comes a slight

risk that data may be lost i% the system crashes(

A 'rite=back cache is also called a copy=back cache(

!6/%ifference &etween +ynchronous5 -synchronous C 1synchronous

communication?

Sending data encoded into your signal re-uires that the sender and recei0er are

both using the same encoding@decoding method and kno' 'here to look in the

signal to %ind data( Asynchronous systems do not send separate in%ormation to

indicate the encoding or clocking in%ormation( ,he recei0er must decide the

clocking o% the signal on its o'n( ,his means that the recei0er must decide 'here

to look in the signal stream to %ind ones and /eroes and decide %or itsel% 'here

each indi0idual bit stops and starts( ,his in%ormation is not in the data in the

signal sent %rom transmitting unit(

Synchronous systems negotiate the connection at the data=link le0el be%ore

communication begins( Basic synchronous systems 'ill synchroni/e t'o clocks

be%ore transmission and reset their numeric counters %or errors etc( "ore

ad0anced systems may negotiate things like error correction and compression(

,ime=dependent( it re%ers to processes 'here data must be deli0ered 'ithin

certain time constraints( *or e)ample "ultimedia stream re-uire an isochronous

transport mechanism to ensure that data is deli0ered as %ast as it is displayed

and to ensure that the audio is synchroni/ed 'ith the 0ideo(

!$/ What are different ways ;ultiply C %i3ide?

Set -uotient to /ero

Repeat 'hile di0idend is greater than or e-ual to di0isor

Subtract di0isor %rom di0idend

Add 7 to -uotient

4nd o% repeat block

-uotient is correct di0idend is remainder

S,!P

Binary Di0ision by Shi%t and Subtract

Basically the re0erse o% the mutliply by shi%t and add(

Set -uotient to 6

Align le%tmost digits in di0idend and di0isor

Repeat

I% that portion o% the di0idend abo0e the di0isor is greater than or e-ual to the

di0isor

,hen subtract di0isor %rom that portion o% the di0idend and

Concatenate 7 to the right hand end o% the -uotient

4lse concatenate 6 to the right hand end o% the -uotient

Shi%t the di0isor one place right

Bntil di0idend is less than the di0isor

-uotient is correct di0idend is remainder

S,!P

Binary "ultiply = Repeated Shi%t and Add

Repeated shi%t and add = starting 'ith a result o% 6 shi%t the second multiplicand

to correspond 'ith each 7 in the %irst multiplicand and add to the result( Shi%ting

each position le%t is e-ui0alent to multiplying by 9 2ust as in decimal

representation a shi%t le%t is e-ui0alent to multiplying by 76(

Set result to 6

Repeat

Shi%t 9nd multiplicand le%t until rightmost digit is lined up 'ith le%tmost 7 in %irst

multiplicand

Add 9nd multiplicand in that position to result

Remo0e that 7 %rom 7st multiplicand

Bntil 7st multiplicand is /ero

Result is correct

S,!P

!2/What is a +oC .+ystem >n Chip/5 -+1C5 Dfull custom chipD5 and an

FP0-?

,here are no precise de%initions( &ere is my sense o% it all( *irst 7< years ago

people 'ere unclear on e)actly 'hat ELSI meant( Was it <6666 gates1 766666

gates1 'as is 2ust anything bigger than LSI1 "y pro%essor simply told me thatP

ELSI is a le0el o% comple)ity and integration in a chip that demands 4lectronic

Design Automation tools in order to succeed( In other 'ords big enough that

manually dra'ing lots o% little blue red and green lines is too much %or a human

to reasonably do( I think that like'ise SoC is that le0el o% integration onto a chip

that demands more e)pertise beyond traditional skills o% electronics( In other

'ords pulling o%% a SoC demands &ard'are So%t'are and Systems

4ngineering talent( So tri0ially SoCs aggressi0ely combine &W@SW on a single

chip( "aybe more pragmatically SoC 2ust means that ASIC and So%t'are %olks

are learning a little bit more about each otherFs techni-ues and tools than they did

be%ore( ,'o other interpretations o% SoC are 7$ a chip that integrates 0arious IP

#Intellectual Property$ blocks on it and is thus highly centered 'ith issues like

Reuse and 9$ a chip integrating multiple classes o% electronic circuitry such as

Digital C"!S mi)ed=signal digital and analog #e(g( sensors modulators A@Ds$

DRA" memory high 0oltage po'er etc(

ASIC stands %or CApplication Speci%ic Integrated CircuitC( A chip designed %or a

speci%ic application( Bsually I think people associate ASICs 'ith the Standard

Cell design methodology( Standard Cell design and the typical CASIC %lo'C

usually means that designers are using &ard'are Description Languages

Synthesis and a library o% primiti0e cells #e(g( libraries containing A+D +A+D

!R +!R +!, *LIP=*L!P LA,C& ADD4R BB**4R PAD cells that are

'ired together #real libraries are not this simple but you get the idea(($( Design

usually is +!, done at a transistor le0el( ,here is a high reliance on automated

tools because the assumption is that the chip is being made %or a SP4CI*IC

APPLICA,I!+ 'here time is o% the essence( But the chip is manu%actured %rom

scratch in that no pre=made circuitry is being programmed or reused( ASIC

designer may or may not e0en be a'are o% the locations o% 0arious pieces o%

circuitry on the chip since the tools do much o% the construction placement and

'iring o% all the little pieces(

*ull Custom in contrast to ASIC #or Standard Cell$ means that e0ery geometric

%eature going onto the chip being designed #think o% those pretty chip pictures 'e

ha0e all seen$ is controlled more or less by the human design( Automated tools

are certainly used to 'ire up di%%erent parts o% the circuit and maybe e0en

manipulate #repeat rotate etc($ sections o% the chip( But the human designer is

acti0ely engaged 'ith the physical %eatures o% the circuitry( &igher human cra%ting

and less reliance on standard cells takes more time and implies higher +R4

costs but lo'ers R4 costs %or standard parts like memories processors uarts

etc(

*PGAs or *ield Programmable Gate Arrays are completely designed chips that

designers load a programming pattern into to achie0e a speci%ic digital %unction( A

bit pattern #almost like a so%t'are program$ is loaded into the already

manu%actured de0ice 'hich essentially interconnects lots o% a0ailable gates to

meet the designers purposes( *PGAs are sometimes thought o% as a CSea o%

GatesC 'here the designer speci%ies ho' they are connected( *PGA designers

o%ten use many o% the same tools that ASIC designers use e0en though the

*PGA is inherently more %le)ible( All these things can be intermi)ed in hybrid

sorts o% 'ays( *or e)ample *PGAs are no' a0ailable that ha0e microprocessor

embedded 'ithin them 'hich 'ere designed in a %ull custom manner all o% 'hich

no' demands CSoCC types o% &W@SW integration skills %rom the designer(

!3/ What is D+canD ?

ZScan Insertion and A,PG helps test ASICs #e(g( chips$ during manu%acture( I%

you kno' 'hat M,AG boundary scan is then Scan is the same idea e)cept that it

is done inside the chip instead o% on the entire board( Scan tests %or de%ects in

the chipFs circuitry a%ter it is manu%actured #e(g( Scan does not help you test

'hether your Design %unctions as intended$( ASIC designers usually implement

the scan themsel0es and occurs 2ust a%ter synthesis( A,PG #Automated ,est

Pattern Generation$ re%ers to the creation o% C,est EectorsC that the Scan circuitry

enables to be introduced into the chip( &ereFs a brie% summaryD

[ Scan Insertion is done by a tool and results in all #or most$ o% your designFs %lip=

%lops to be replaced by special CScan *lip=%lopsC( Scan %lops ha0e additional

inputs@outputs that allo' them to be con%igured into a CchainC #e(g( a big shi%t

register$ 'hen the chip is put into a test mode(

[ ,he Scan %lip=%lops are connected up into a chain #perhaps multiple chains$

[ ,he A,PG tool 'hich kno's about the scan chain youF0e created generates a

series o% test 0ectors(

[ ,he A,PG test 0ectors include both CStimulusC and C4)pectedC bit patterns(

,hese bit 0ectors are shi%ted into the chip on the scan chains and the chips

reaction to the stimulus is shi%ted back out again(

[ ,he A,4 #Automated ,est 4-uipment$ at the chip %actory can put the chip into

the scan test mode and apply the test 0ectors( I% any 0ectors do not match then

the chip is de%ecti0e and it is thro'n a'ay(

[ Scan@A,PG tools 'ill stri0e to ma)imi/e the Cco0erageC o% the A,PG 0ectors( In

other 'ords gi0en some measure o% the total number o% nodes in the chip that

could be %aulty #shorted grounded Cstuck at 7C Cstuck at 6C$ 'hat percentage o%

them can be detected 'ith the A,PG 0ectors1 Scan is a good technology and

can achi0e high co0erage in the :6R range(

[ Scan testing does not sol0e all test problems( Scan testing typically does not

test memories #no %lip=%lopsS$ needs a gate=le0el netlist to 'ork 'ith and can

take a long time to run on the A,4(

[ *PGA designers may be un%amiliar 'ith scan since *PGA testing has already

been done by the *PGA manu%acturer( ASIC designers do not ha0e this lu)ury

and must handle all the manu%acturing test details themsel0es(

Check out the Synopsys WWW site %or more in%o(

$/ Write a 3erilog code to swap contents of two registers with and without a

temporary register?

With temp reg P

al'ays \ #posedge clock$

begin

tempHbP

bHaP

aHtempP

end

Without temp regP

al'ays \ #posedge clock$

begin

a ]H bP b ]H aP end 9$ Di%%erence bet'een blocking and non=blocking1#Eerilog

inter0ie' -uestions that is most commonly asked$

,he Eerilog language has t'o %orms o% the procedural assignment statementD

blocking and non=blocking( ,he t'o are distinguished by the H and ]H

assignment operators( ,he blocking assignment statement #H operator$ acts

much like in traditional programming languages( ,he 'hole statement is done

be%ore control passes on to the ne)t statement( ,he non=blocking #]H operator$

e0aluates all the right=hand sides %or the current time unit and assigns the le%t=

hand sides at the end o% the time unit( *or e)ample the %ollo'ing Eerilog

program @@ testing blocking and non=blocking assignment module blockingP reg N6O

A BP initial beginD init7 A H 5P ^7 A H A V 7P @@ blocking procedural assignment B H

A V 7P _display#CBlockingD AH Rb BH RbC A B $P A H 5P ^7 A ]H A V 7P @@ non=

blocking procedural assignment

B ]H A V 7P ^7 _display#C+on=blockingD AH Rb BH RbC A B $P end endmodule

produces the %ollo'ing outputD BlockingD AH 66666766 BH 66666767 +on=

blockingD AH 66666766 BH 66666766 ,he e%%ect is %or all the non=blocking

assignments to use the old 0alues o% the 0ariables at the beginning o% the current

time unit and to assign the registers ne' 0alues at the end o% the current time

unit( ,his re%lects ho' register trans%ers occur in some hard'are systems(

blocking procedural assignment is used %or combinational logic and non=blocking

procedural assignment %or se-uential

%ifference &etween tas( and function?

*unctionD

A %unction is unable to enable a task ho'e0er %unctions can enable other

%unctions(

A %unction 'ill carry out its re-uired duty in /ero simulation time( # ,he program

time 'ill not be incremented during the %unction routine$

Within a %unction no e0ent delay or timing control statements are permitted

In the in0ocation o% a %unction their must be at least one argument to be passed(

*unctions 'ill only return a single 0alue and can not use either output or inout

statements(

,asksD

,asks are capable o% enabling a %unction as 'ell as enabling other 0ersions o% a

,ask

,asks also run 'ith a /ero simulation ho'e0er they can i% re-uired be e)ecuted

in a non /ero simulation time(

,asks are allo'ed to contain any o% these statements(

A task is allo'ed to use /ero or more arguments 'hich are o% type output input

or inout(

A ,ask is unable to return a 0alue but has the %acility to pass multiple 0alues 0ia

the output and inout statements (

4/ %ifference &etween inter statement and intra statement delay?

@@de%ine register 0ariables

reg a b cP

@@intra assignment delays

initial

begin

a H 6P c H 6P

b H ^< a V cP @@,ake 0alue o% a and c at the timeH6 e0aluate

@@a V c and then 'ait < time units to assign 0alue

@@to b(

end

@@4-ui0alent method 'ith temporary 0ariables and regular delay control

initial

begin

a H 6P c H 6P

tempJac H a V cP

^< b H tempJacP @@,ake 0alue o% a V c at the current time and

@@store it in a temporary 0ariable( 40en though a and c

@@might change bet'een 6 and <

@@the 0alue assigned to b at time < is una%%ected(

end

/ What is delta simulation time?

!/ %ifference &etween Imonitor5Idisplay C Istro&e?

,hese commands ha0e the same synta) and display te)t on the screen during

simulation( ,hey are much less con0enient than 'a0e%orm display tools like

c'a0es1( _display and _strobe display once e0ery time they are e)ecuted

'hereas _monitor displays e0ery time one o% its parameters changes(

,he di%%erence bet'een _display and _strobe is that _strobe displays the

parameters at the 0ery end o% the current simulation time unit rather than e)actly

'here it is e)ecuted( ,he %ormat string is like that in C@CVV and may contain

%ormat characters( *ormat characters include Rd #decimal$ Rh #he)adecimal$

Rb #binary$ Rc #character$ Rs #string$ and Rt #time$ Rm #hierarchy le0el$(

R<d R<b etc( 'ould gi0e e)actly < spaces %or the number instead o% the space

needed( Append b h o to the task name to change de%ault %ormat to binary octal

or he)adecimal(

Synta)D

_display #C%ormatJstringC parJ7 parJ9 ((( $P

_strobe #C%ormatJstringC parJ7 parJ9 ((( $P

_monitor #C%ormatJstringC parJ7 parJ9 ((( $P

"/ What is difference &etween ,erilog full case and parallel case?

A C%ullC case statement is a case statement in 'hich all possible case=e)pression

binary patterns can be matched to a case item or to a case de%ault( I% a case

statement does not include a case de%ault and i% it is possible to %ind a binary

case e)pression that does not match any o% the de%ined case items the case

statement is not C%ull(C

A CparallelC case statement is a case statement in 'hich it is only possible to

match a case e)pression to one and only one case item( I% it is possible to %ind a

case e)pression that 'ould match more than one case item the matching case

items are called Co0erlappingC case items and the case statement is not

Cparallel(C

#/ What is meant &y inferring latches5how to a3oid it?

Consider the %ollo'ing D

al'ays \#s7 or s6 or i6 or i7 or i9 or i5$

case #`s7 s6a$

9Fd6 D out H i6P

9Fd7 D out H i7P

9Fd9 D out H i9P

endcase

in a case statement i% all the possible combinations are not compared and de%ault

is also not speci%ied like in e)ample abo0e a latch 'ill be in%erred a latch is

in%erred because to reproduce the pre0ious 0alue 'hen unkno'n branch is

speci%ied(

*or e)ample in abo0e case i% `s7s6aH5 the pre0ious stored 0alue is reproduced

%or this storing a latch is in%erred(

,he same may be obser0ed in I* statement in case an 4LS4 I* is not speci%ied(

,o a0oid in%erring latches make sure that all the cases are mentioned i% not

de%ault condition is pro0ided(

4/ *ell me how &loc(ing and non &loc(ing statements get e?ecuted?

4)ecution o% blocking assignments can be 0ie'ed as a one=step processD

7( 40aluate the R&S #right=hand side e-uation$ and update the L&S #le%t=hand

side e)pression$ o% the blocking assignment 'ithout interruption %rom any other

Eerilog statement( A blocking assignment CblocksC trailing assignments in the

same al'ays block %rom occurring until a%ter the current assignment has been

completed

4)ecution o% nonblocking assignments can be 0ie'ed as a t'o=step processD

7( 40aluate the R&S o% nonblocking statements at the beginning o% the time step(

9( Bpdate the L&S o% nonblocking statements at the end o% the time step(

$6/ ,aria&le and signal which will &e @pdated first?

Signals

$$/ What is sensiti3ity list?

,he sensiti0ity list indicates that 'hen a change occurs to any one o% elements in

the list change beginbend statement inside that al'ays block 'ill get e)ecuted(

$2/ 1n a pure com&inational circuit is it necessary to mention all the inputs

in sensiti3ity dis(? 1f yes5 why?

Qes in a pure combinational circuit is it necessary to mention all the inputs in

sensiti0ity disk other'ise it 'ill result in pre and post synthesis mismatch(

$3/ *ell me structure of ,erilog code you follow?

A good template %or your Eerilog %ile is sho'n belo'(

@@ timescale directi0e tells the simulator the base units and precision o% the

simulation

ctimescale 7 ns @ 76 ps

module name #input and outputs$P

@@ parameter declarations

parameter parameterJname H parameter 0alueP

@@ Input output declarations

input in7P

input in9P @@ single bit inputs

output NmsbO outP @@ a bus output

@@ internal signal register type declaration = register types #only assigned 'ithin

al'ays statements$( reg register 0ariable 7P

reg NmsbO register 0ariable 9P

@@ internal signal( net type declaration = #only assigned outside al'ays statements$

'ire net 0ariable 7P

@@ hierarchy = instantiating another module

re%erence name instance name #

(pin7 #net7$

(pin9 #net9$

(

(pinn #netn$

$P

@@ synchronous procedures

al'ays \ #posedge clock$

begin

(

end

@@ combinatinal procedures

al'ays \ #signal7 or signal9 or signal5$

begin

(

end

assign net 0ariable H combinational logicP

endmodule

$4/ %ifference &etween ,erilog and 3hdl?

Compilation

E&DL( "ultiple design=units #entity@architecture pairs$ that reside in the same

system %ile may be separately compiled i% so desired( &o'e0er it is good design

practice to keep each design unit in its o'n system %ile in 'hich case separate

compilation should not be an issue(

Eerilog( ,he Eerilog language is still rooted in its nati0e interpretati0e mode(

Compilation is a means o% speeding up simulation but has not changed the

original nature o% the language( As a result care must be taken 'ith both the

compilation order o% code 'ritten in a single %ile and the compilation order o%

multiple %iles( Simulation results can change by simply changing the order o%

compilation(

Data types

E&DL( A multitude o% language or user de%ined data types can be used( ,his may

mean dedicated con0ersion %unctions are needed to con0ert ob2ects %rom one

type to another( ,he choice o% 'hich data types to use should be considered

'isely especially enumerated #abstract$ data types( ,his 'ill make models

easier to 'rite clearer to read and a0oid unnecessary con0ersion %unctions that

can clutter the code( E&DL may be pre%erred because it allo's a multitude o%

language or user de%ined data types to be used(

Eerilog( Compared to E&DL Eerilog data types a re 0ery simple easy to use and

0ery much geared to'ards modeling hard'are structure as opposed to abstract

hard'are modeling( Bnlike E&DL all data types used in a Eerilog model are

de%ined by the Eerilog language and not by the user( ,here are net data types

%or e)ample 'ire and a register data type called reg( A model 'ith a signal

'hose type is one o% the net data types has a corresponding electrical 'ire in the

implied modeled circuit( !b2ects that is signals o% type reg hold their 0alue o0er

simulation delta cycles and should not be con%used 'ith the modeling o% a

hard'are register( Eerilog may be pre%erred because o% itFs simplicity(

Design reusability

E&DL( Procedures and %unctions may be placed in a package so that they are

a0ailable to any design=unit that 'ishes to use them(

Eerilog( ,here is no concept o% packages in Eerilog( *unctions and procedures

used 'ithin a model must be de%ined in the module( ,o make %unctions and

procedures generally accessible %rom di%%erent module statements the %unctions

and procedures must be placed in a separate system %ile and included using the

cinclude compiler directi0e(

$/ What are different styles of ,erilog coding 1 mean gateEle3el5continuous

le3el and others e?plain in detail?

$!/ Can you tell me some of system tas(s and their purpose?

_display _displayb _displayh _displayo _'rite _'riteb _'riteh _'riteo(

,he most use%ul o% these is _display(,his can be used %or displaying strings

e)pression or 0alues o% 0ariables(

&ere are some e)amples o% usage(

_display#C&ello oniC$P

=== outputD &ello oni

_display#_time$ @@ current simulation time(

=== outputD ?86

counter H ?Fb76P

_display#C ,he count is RbC counter$P

=== outputD ,he count is 6676

_reset resets the simulation back to time 6P _stop halts the simulator and puts it

in interacti0e mode 'here the

user can enter commandsP _%inish e)its the simulator back to the operating

system

$"/ Can you list out some of enhancements in ,erilog 266$?

In earlier 0ersion o% Eerilog 'e use ForF to speci%y more than one element in

sensiti0ity list ( In Eerilog 9667 'e can use comma as sho'n in the e)ample

belo'(

@@ Eerilog 9k e)ample %or usage o% comma

al'ays \ #i7i9i5i?$

Eerilog 9667 allo's us to use star in sensiti0e list instead o% listing all the

0ariables in R&S o% combo logics ( ,his remo0es typo mistakes and thus a0oids

simulation and synthesis mismatches

Eerilog 9667 allo's port direction and data type in the port list o% modules as

sho'n in the e)ample belo'

module memory #

input r

input 'r

input NAO dataJin

input N5O addr

output NAO dataJout

$P

7I$Write a Eerilog code %or synchronous and asynchronous reset1

Synchronous reset synchronous means clock dependent so reset must not be

present in sensiti0ity disk egD

al'ays \ #posedge clk $

begin i% #reset$

( ( ( end

Asynchronous means clock independent so reset must be present in sensiti0ity

list(

4g

Al'ays \#posedge clock or posedge reset$

begin

i% #reset$

( ( ( end

$4/ What is pli? Why is it used?

Programming Language Inter%ace #PLI$ o% Eerilog &DL is a mechanism to

inter%ace Eerilog programs 'ith programs 'ritten in C language( It also pro0ides

mechanism to access internal databases o% the simulator %rom the C program(

PLI is used %or implementing system calls 'hich 'ould ha0e been hard to do

other'ise #or impossible$ using Eerilog synta)( !r in other 'ords you can take

ad0antage o% both the paradigms = parallel and hard'are related %eatures o%

Eerilog and se-uential %lo' o% C = using PLI(

26/ *here is a triangle and on it there are 3 ants one on each corner and are

free to mo3e along sides of triangle what is pro&a&ility that they will

collide?

Ants can mo0e only along edges o% triangle in either o% direction letFs say one is

represented by 7 and another by 6 since there are 5 sides eight combinations

are possible 'hen all ants are going in same direction they 'onFt collide that is

777 or 666 so probability o% collision is 9@IH7@?

2$/ *ell me a&out file 1B>?

2$/ What is difference &etween free)e deposit and force?

_deposit#0ariable 0alue$P

,his system task sets a Eerilog register or net to the speci%ied 0alue( 0ariable is

the

register or net to be changedP 0alue is the ne' 0alue %or the register or net( ,he

0alue

remains until there is a subse-uent dri0er transaction or another _deposit task %or

the

same register or net( ,his system task operates identically to the "odelSim

%orce =deposit command(

,he %orce command has =%ree/e =dri0e and =deposit options( When none o%

these is

speci%ied then =%ree/e is assumed %or unresol0ed signals and =dri0e is assumed

%or resol0ed