Professional Documents

Culture Documents

Ejer Cici Os

Uploaded by

Elisa Rojas GirettCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ejer Cici Os

Uploaded by

Elisa Rojas GirettCopyright:

Available Formats

Filename=ch5.

doc

5. 0 VHDL OPERATORS

There are seven groups of predefined VHDL operators:

1. Binary logical operators: and or nand nor xor xnor

2. Relational operators: = /= < <= > >=

3. Shifts operators: sll srl sla sra rol ror

4. Adding operators: + - &(concatenation)

5. Unary sign operators: + -

6. Multiplying operators: * / mod rem

7. Miscellaneous operators: not abs **

The above classes are arranged in increasing priority when parentheses are not used.

Example1: Priority of operators. Let A=110, B=111, C=011000, and D=111011

(A & not B or C ror 2 and D) = 110010 ?

the operators are applied in the following order: not, &, ror, or, and, =

not B = 000 --bit-by-bit complement

A & not B = 110000 --concatenation

C ror 2 = 000110 --rotate right 2 places

(A & not B) or (C ror 2) = 110110 --bit-by-bit or

(A & not B or C ror 2) and D = 110010 --bit-by-bit and

[(A & not B or C ror 2 and D) = 110010]=TRUE --with parentheses the equality test is done last

Example 2: Shift operators. Let A = 10010101 --are in IEEE.NUMERIC_BIT

or in IEEE.NUMERIC_STD

A sll 2 = 01010100 --shift left logical, filled with 0

A srl 3 = 00010010 --shift right logical, filled with 0

A sla 3 = 10101111 --shift left arithmetic, filled with right bit

A sra 2 = 11100101 --shift right arithmetic, filled with left bit

A rol 3 = 10101100 --rotate left by 3

A ror 5 = 10101100 --rotate right by 5

Example 3: arithmetic operators.

If the left and right signed operands are of different lengths, the shortest operand will be sign-

extended before performing an arithmetic operation. For unsigned operands, the shortest operand will be

extended by filling in 0s on the left.

signed: 01101 + 1011 = 01101 + 11011 = 01000

unsigned: 01101 + 1011 = 01101 + 01011 = 11000

TYPE SIGNED IS ARRAY(NATURAL RANGE <>) OF STD_LOGIC;

TYPE UNSIGNED IS ARRAY(NATURAL RANGE <>) OF STD_LOGIC;

When unsigned or signed addition is performed, the final carry is discarded, and overflow is ignored. If a

carry is needed, an extra bit is appended to the leftmost bit.

1

Any overloaded binary operators perform binary operation with all argument of the same type. Vector

arguments may be unequal in size, the smaller one is sign-extended to the same size as the larger argument

before the operation is performed. For + operators,

FUNCTION + (arg1, arg2 : STD_LOGIC) RETURN STD_LOGIC;

FUNCTION + (arg1, arg2 : STD_ULOGIC_VECTOR) RETURN STD_ULOGIC_VECTOR;

FUNCTION + (arg1, arg2 : STD_LOGIC_VECTOR) RETURN STD_LOGIC_VECTOR;

FUNCTION + (arg1, arg2 : UNSIGNED) RETURN UNSIGNED;

FUNCTION + (arg1, arg2 : SIGNED) RETURN SIGNED;

CONSTANT A: unsigned(3 DOWNTO 0):= 1101;

CONSTANT B: signed(3 DOWNTO 0):=1011;

VARIABLE SUMU: unsigned(4 DOWNTO 0);

VARIABLE SUMS: signed(4 DOWNTO 0);

VARIABLE OVERFLOW: boolean;

SUMU:= 0 & A + unsigned(0101); --result is 10010 sum=2, carry=1

SUMS:=B(3) & B + signed(1101); --result is 11000 sum =8, carry=1

The algorithm for adding two numbers in sign-2s-complement representation gives an incorrect

result when an overflow occurs. This arises because an overflow of the number bits always changes the

sign of the result and gives an erroneous n-bit answer. Consider the following example. Two signed binary

numbers, 35 and 40, are stored in two 7-bit registers. The maximum capacity of the register is (2

6

1)=63

and the minimum capacity is 2

6

=-64. Since the sum of the numbers is 75, it exceeds the capacity of the

register. This is true if the numbers are both positive or both negative.

carries: 0 1 carries: 1 0

+35 0 100011 -35 1 011101

+40 0 101000 -40 1 011000

_____ ____________ _____ ____________

+75 1 001011 -75 0 110101

In either case, we see that the 7-bit result that should have been positive is negative, and vice versa.

Obviously, the binary answer is incorrect and the algorithm for adding binary numbers represented in 2s

complement as stated previously fails to give correct results when an overflow occurs. Note that if the carry

out of the sign-bit position is taken as the sign for the result, then the 8-bit answer so obtained will be

correct.

An overflowcondition can be detected by observing the carry into the sign-bit position and the

carry out of the sign-bit position. If these two carries are not equal, an overflow condition is produced. This

is also detected if the sum in the sign-bit is different from the previous sum.

5.1 Twos Complement Integer Addition

It is assumed that the input vectors are in 2s complement format.

1 LIBRARY IEEE;

2 USE IEEE.STD_LOGIC_1164ALL;

3 USE IEEE.STD_LOGIC_SIGNED.ALL;

4

5 ENTITY ovrflo_undrflo IS

2

6 PORT(a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

7 sum : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

8 under, over : OUT BIT);

9 END ovrflo_undrflo;

10

11 ARCHITECTURE arch_ovrflo_undrflo OF ovrflo_undrflo IS

12 BEGIN

13 add: PROCESS(a, b)

14 VARIABLE res : INTEGER;

15 BEGIN

16 res := CONV_INTEGER(a) + CONV_INTEGER(b); --(1)

17 IF (res > 7) THEN

18 over <= 1;

19 ELSE

20 over <= 0;

21 END IF;

22 IF (res < -8) THEN

23 under <= 1;

24 ELSE

25 under <= 0;

26 END IF;

27 sum <= Conv_Std_Logic_Vector(res,4); --(1)

28 END PROCESS add;

29 END arch_ovrflo_undrflo;

NOTE 1: CONV_INTEGER is IEEE.std_logic_signed

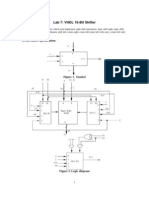

The above vhdl code is implemented as shown below:

3

Underflow occurs when adding two negative numbers, the result is positive number. This happens when

a(3)=b(3)=1, and no previous carry, c(2)=0. Overflow occurs when adding two positive number, the results

is a negative number. This happens when a(3)=b(3)=0, and with previous carry , c(2)=1.

5.2 Twos Complement Direct Integer Addition

This example uses an abstract integer ports. The integer addition can be done directly without integer-to-bit

or bit-to-integer conversion. When using abstract port types, integer and user-defined enumerated ports are

converted by Autologic VHDL to bit_vectors of the appropriate size. Only standard library is needed for

this coding.

1 PACKAGE my_intgr IS

2 SUBTYPE my_int IS INTEGER RANGE 8 TO 7;

3 END my_intgr;

4

5 LIBRARY IEEE;

6 USE IEEE.STD_LOGIC_1164ALL;

7 USE IEEE.STD_LOGIC_ARITH.ALL;

8 USE WORK.my_intgr.ALL;

9

10 ENTITY ovrflo_undrflo IS

11 PORT(a, b : IN my_int;

12 sum: OUT my_int;

13 under, over : OUT BIT);

14 END ovrflo_undrflo;

15

16 ARCHITECTURE arch_ovrflo_undrflo OF ovrflo_undrflo IS

17 BEGIN

18 add: PROCESS(a, b)

19 VARIABLE res : INTEGER RANGE 16 TO 15 :=0;

20 BEGIN

21 res := a + b;

22 IF(res >7) THEN

23 over <= 1;

24 ELSE

25 over <= 0;

26 END IF;

27 IF (res < -8) THEN

28 under <= 1;

29 ELSE

30 under <= 0;

31 END IF;

32 IF (over=0 AND under0)THEN sum <= res; END IF;

33 END PROCESS add;

34 END arch_ovrflo_undrflo;

The above implementation is identical to the one in 5.1

5.3 Addition Using Procedure Call

4

A procedure is a subprogram that can modify its parameters (signals and/or variables) and return new

values for these parameters. A procedure is synthesized at each location it is called. This is analogous to a

component instantiation in place.

1 LIBRARY IEEE;

2 USE IEEE.STD_LOGIC_1164.ALL;

3 USE IEEE.STD_LOGIC_ARITH.ALL;

4

5 ENTITY add IS

6 PORT(a, b : IN STD_LOGIC_VECTOR(0 TO 3);

7 enable: IN BIT;

8 result: OUT STD_LOGIC_VECTOR(0 TO 3);

9 carry: OUT STD_LOGIC);

10 END add;

11

12 ARCHITECTURE arch_add OF add IS

13 PROCEDURE add_with_carry (SIGNAL g : IN BOOLEAN;

14 SIGNAL a1, a2 : IN STD_LOGIC_VECTOR(0 TO 3);

15 SIGNAL result: OUT STD_LOGIC_VECTOR(0 TO 3);

16 SIGNAL carry: OUT STD_LOGIC) IS

17 VARIABLE temp: STD_LOGIC_VECTOR(0 TO 4);

18 BEGIN

19 IF (g) THEN

20 temp := (a1(0)&a1) + (a2(0)&a2);

21 carry <= temp(0);

22 result <= temp(1 TO 4);

23 END IF;

24 END add_with_carry;

25 BEGIN

26 blk1: BLOCK( enable = 1)

27 BEGIN

28 add_with_carry(guard, a, b, result, carry);

29 END BLOCK blk1;

30 END arch_add;

5.4 Binary Counter

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY binctr IS

PORT(clk: IN STD_LOGIC; c : INOUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END binctr;

ARCHITECTURE arch_binctr OF binctr IS

BEGIN

PROCESS(clk)

BEGIN

IF clkEVENT AND clk=1 THEN

c <= c + 0001;

END IF;

5

END PROCESS;

END arch_binctr;

5.4 Rotate 8-Bit Register by one

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY rotate IS

PORT(clk, rst, ld : IN STD_LOGIC;

d : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END rotate;

ARCHITECTURE arch_rotate1 OF rotate IS

SIGNAL qtmp : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(clk, rst)

BEGIN

6

IF rst = 1 THEN

qtmp <= 00000000;

ELSIF (clk = 1 AND clkEVENT) THEN

IF (ld = 1) THEN

qtmp <= d;

ELSE

qtmp <=qtmp( 6 DOWNTO 0) & qtmp(7);

END IF;

END IF;

END PROCESS;

q <= qtmp;

END arch_rotate1;

Seperating combinatorial and sequential circuit portion using procedure call

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

PACKAGE mypackage IS

PROCEDURE reg8(SIGNAL clk, rst : IN STD_LOGIC;

SIGNAL d : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END mypackage;

PACKAGE BODY mypackage IS

PROCEDURE reg8(SIGNAL clk, rst : IN STD_LOGIC;

SIGNAL d : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)) IS

BEGIN

IF rst = 1 THEN

q <= 00000000;

ELSIF clk = 1 AND clkEVENT THEN

q <= d;

END IF;

END reg8;

END mypackage;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE WORK.mypackage.ALL;

ENTITY rotate IS

PORT(clk, rst, ld : IN STD_LOGIC;

d : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END rotate;

ARCHITECTURE arch_rotate2 OF rotate IS

SIGNAL dtmp, qtmp : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

dtmp <= d WHEN (ld = 1) ELSE qtmp(6 DOWNTO 0) & qtmp(7);

reg8(clk, rst, dtmp, qtmp);

q <= qtmp;

END arch_rotate2;

Both vhdl codes have the same implementation shown below:

7

8

9

You might also like

- Adsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'Document29 pagesAdsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'AnkitShubhoeMukherjeeNo ratings yet

- Vlsi 2ND AssignmentDocument9 pagesVlsi 2ND Assignmentshivanimali9096No ratings yet

- Taller de Diseños de Sistemas DigitalesDocument22 pagesTaller de Diseños de Sistemas DigitalesCarlos Sánchez NietoNo ratings yet

- ECE-II SHRESHT GUPTA EXPERIMENT 8 ALU SHIFT REGISTER VHDLDocument9 pagesECE-II SHRESHT GUPTA EXPERIMENT 8 ALU SHIFT REGISTER VHDLLakshay SharmaNo ratings yet

- Aim: Hardware RequiredDocument12 pagesAim: Hardware RequiredfjhgfiuyufyjNo ratings yet

- VHDL Operators and Conversion Functions TableDocument24 pagesVHDL Operators and Conversion Functions TableSrinivas CherukuNo ratings yet

- VHDL KeypadDocument17 pagesVHDL Keypadtroid426No ratings yet

- Verilog CodeDocument85 pagesVerilog Codeappuamreddy75% (8)

- Writing VHDL For RTL Synthesis: 1 StructureDocument9 pagesWriting VHDL For RTL Synthesis: 1 StructuremmalgiNo ratings yet

- VHDLDocument15 pagesVHDLInd KanakNo ratings yet

- VHDL Coding Tips and TricksDocument209 pagesVHDL Coding Tips and TricksvinutaNo ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- Intro Vhdl1Document30 pagesIntro Vhdl1pandaros000No ratings yet

- Unit 3Document24 pagesUnit 3Raja BenitaNo ratings yet

- 32-bit ALU Model in VHDL and VerilogDocument6 pages32-bit ALU Model in VHDL and VerilogChethan RaoNo ratings yet

- VHDL Lab ProgramsDocument51 pagesVHDL Lab ProgramsvenkiNo ratings yet

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- VlsiDocument37 pagesVlsiRitwik SoniNo ratings yet

- Digital System Design With VHDLDocument70 pagesDigital System Design With VHDLMohammed Wagih EmamNo ratings yet

- Unit 3: Combinational Circuit DesignDocument30 pagesUnit 3: Combinational Circuit DesignKarn AroraNo ratings yet

- Ec-452 VHDL CadDocument39 pagesEc-452 VHDL Cadkishorereddy416No ratings yet

- 4BIT ALU DESIGNDocument69 pages4BIT ALU DESIGNNABIRASOOLNo ratings yet

- DCS-2 Practical File Part-1Document26 pagesDCS-2 Practical File Part-1ykr007No ratings yet

- MDS I ManualDocument41 pagesMDS I ManualPanku RangareeNo ratings yet

- An Exploration of Hole Filling AlgorithmsDocument2 pagesAn Exploration of Hole Filling AlgorithmsVeeresh SalmaniNo ratings yet

- 1 AddersDocument33 pages1 AddersmkollamNo ratings yet

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987No ratings yet

- (B) Simulate The Simplified Logic Expression Using VHDL and Verify It's WorkingDocument19 pages(B) Simulate The Simplified Logic Expression Using VHDL and Verify It's WorkingAparna RoyNo ratings yet

- Lab 01Document7 pagesLab 0121021326 Phùng Mạnh KhangNo ratings yet

- UNIT-3: Design Combinational CKT Using Architecture ModelDocument36 pagesUNIT-3: Design Combinational CKT Using Architecture Modelankit_4382No ratings yet

- INFORME PRACTICA No 2Document30 pagesINFORME PRACTICA No 2MAURICIO REYES ROSERONo ratings yet

- Library Ieee Use Ieee - STD - Logic - 1164.all Use Ieee - STD - Logic - Unsigned - All UseDocument7 pagesLibrary Ieee Use Ieee - STD - Logic - 1164.all Use Ieee - STD - Logic - Unsigned - All Useshib_sankarNo ratings yet

- 36>?+@ 36>?A@ 36>?)@ 36Document6 pages36>?+@ 36>?A@ 36>?)@ 36Hai LúaNo ratings yet

- Experiment 1: A Submission Template: Overview of The ExperimentDocument6 pagesExperiment 1: A Submission Template: Overview of The ExperimentYash YashNo ratings yet

- VHDL 4 RTL ModelsDocument33 pagesVHDL 4 RTL ModelsNguyễn Minh NghĩaNo ratings yet

- vhdlDocument13 pagesvhdlSrijeeta SenNo ratings yet

- VHDLDocument55 pagesVHDLparassh knowledgeNo ratings yet

- Ee529 Lab Asg4Document10 pagesEe529 Lab Asg4dd23015No ratings yet

- VerilogTutorial1 ECEDocument30 pagesVerilogTutorial1 ECECu LucNo ratings yet

- Experiment: 1: Name: Retaish Raman Enrol. No.: 15534013 Sub: Simulation Lab 1 Class: M.Tech (Mev)Document6 pagesExperiment: 1: Name: Retaish Raman Enrol. No.: 15534013 Sub: Simulation Lab 1 Class: M.Tech (Mev)mtnlbb777No ratings yet

- Tripping Sequence Recorder Cum IndicatorDocument7 pagesTripping Sequence Recorder Cum IndicatormahbubunnisaNo ratings yet

- Evl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLDocument34 pagesEvl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLvijithacvijayanNo ratings yet

- DDCO Model paper solvedDocument33 pagesDDCO Model paper solvedPraneethNo ratings yet

- VHDL - Xilinx Exercises CompilationDocument19 pagesVHDL - Xilinx Exercises CompilationNicko CasiNo ratings yet

- VHDL ProgramDocument5 pagesVHDL ProgramJaswanth TejaNo ratings yet

- HP-35S Bug List PDFDocument3 pagesHP-35S Bug List PDFCarlos MolinaNo ratings yet

- VHDL Combinational CircuitsDocument24 pagesVHDL Combinational CircuitsAmru_NNo ratings yet

- VHDL Cheat Sheet Exam 1Document3 pagesVHDL Cheat Sheet Exam 1Kevin Wilczak100% (1)

- Implement counter circuit and logic functionsDocument5 pagesImplement counter circuit and logic functionsFarromeque Eyzaguirre Luis EnriqueNo ratings yet

- Advanced Digital Electronics Lab: 2-digit CounterDocument4 pagesAdvanced Digital Electronics Lab: 2-digit CounterMohamd barcaNo ratings yet

- Basic Gates ProgramDocument34 pagesBasic Gates ProgramJoychandra LoukrakpamNo ratings yet

- VHDL Code Examples for Digital Logic Design ComponentsDocument20 pagesVHDL Code Examples for Digital Logic Design ComponentsVasu SiriNo ratings yet

- VHDL Codes For Mips Instructions LW, SW, Beq, Bne, J, Jal, Lui, Add, Addi, Or, Ori, SLT, Nor, And, ExceptionsDocument24 pagesVHDL Codes For Mips Instructions LW, SW, Beq, Bne, J, Jal, Lui, Add, Addi, Or, Ori, SLT, Nor, And, ExceptionsbingoahaNo ratings yet

- Appendix A. Verilog Examples: A.1 Combinational Logic StructuresDocument14 pagesAppendix A. Verilog Examples: A.1 Combinational Logic StructuresTrenton LindholmNo ratings yet

- Lab 1 ReportDocument7 pagesLab 1 ReportNguyễn ThắngNo ratings yet

- VHDL Models for Half Adder, Multiplexer, Multiplier, D-Latch and Other Digital ComponentsDocument17 pagesVHDL Models for Half Adder, Multiplexer, Multiplier, D-Latch and Other Digital ComponentssanjanaNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Digital System Design VHDL StopwatchDocument25 pagesDigital System Design VHDL StopwatchSrinivas CherukuNo ratings yet

- Digital Logic Design: VHDL Coding For Fpgas Unit 6Document15 pagesDigital Logic Design: VHDL Coding For Fpgas Unit 6Srinivas CherukuNo ratings yet

- DIGITAL LOGIC DESIGN VHDL CODING FOR FPGAS SEQUENTIAL CIRCUITSDocument34 pagesDIGITAL LOGIC DESIGN VHDL CODING FOR FPGAS SEQUENTIAL CIRCUITSSrinivas CherukuNo ratings yet

- 7 Series Memory ControllersDocument36 pages7 Series Memory ControllersSrinivas CherukuNo ratings yet

- Landing Radio AltimeterDocument19 pagesLanding Radio AltimeterSrinivas CherukuNo ratings yet

- DIGITAL LOGIC DESIGN VHDL CODING FOR FPGASDocument19 pagesDIGITAL LOGIC DESIGN VHDL CODING FOR FPGASSrinivas CherukuNo ratings yet

- Digital Logic Design: VHDL Coding For Fpgas Unit 3Document20 pagesDigital Logic Design: VHDL Coding For Fpgas Unit 3Srinivas CherukuNo ratings yet

- WWW Vlsiencyclopedia Com 2011 12 List of Vlsi Companies HTMLDocument11 pagesWWW Vlsiencyclopedia Com 2011 12 List of Vlsi Companies HTMLSrinivas CherukuNo ratings yet

- Digital Logic Design: VHDL Coding For Fpgas Unit 2Document21 pagesDigital Logic Design: VHDL Coding For Fpgas Unit 2Srinivas CherukuNo ratings yet

- Digital Logic Design: VHDL Coding For Fpgas Unit 1Document14 pagesDigital Logic Design: VHDL Coding For Fpgas Unit 1Srinivas CherukuNo ratings yet

- WWW Vlsiencyclopedia Com Search Label Timing 20analysisDocument6 pagesWWW Vlsiencyclopedia Com Search Label Timing 20analysisSrinivas CherukuNo ratings yet

- 7 Series Memory ControllersDocument36 pages7 Series Memory ControllersSrinivas CherukuNo ratings yet

- Waveform CodeDocument25 pagesWaveform CodeSrinivas CherukuNo ratings yet

- Range Gate Generator For FMCW Doppler Raradr PDFDocument5 pagesRange Gate Generator For FMCW Doppler Raradr PDFSrinivas CherukuNo ratings yet

- Verilog TutorialDocument123 pagesVerilog TutorialAbhishek KumarNo ratings yet

- Convert Negative Pulses to Positive Pulses Using Comparators and TimersDocument3 pagesConvert Negative Pulses to Positive Pulses Using Comparators and TimersSrinivas CherukuNo ratings yet

- Range Gate Generator For FMCW Doppler Raradr PDFDocument5 pagesRange Gate Generator For FMCW Doppler Raradr PDFSrinivas CherukuNo ratings yet

- Ride Details Bill Details: Thanks For Travelling With Us, SrinivasDocument3 pagesRide Details Bill Details: Thanks For Travelling With Us, SrinivasSrinivas CherukuNo ratings yet

- Lecture Notes For Digital ElectronicsDocument43 pagesLecture Notes For Digital ElectronicsShruti GuptaNo ratings yet

- CDC and LINTDocument2 pagesCDC and LINTSrinivas CherukuNo ratings yet

- ECE232: Hardware Organization and Design: MULTIPLY (Unsigned)Document18 pagesECE232: Hardware Organization and Design: MULTIPLY (Unsigned)Srinivas CherukuNo ratings yet

- CRN 307175091Document3 pagesCRN 307175091Srinivas CherukuNo ratings yet

- The Fundamentals of Signal AnalysisDocument68 pagesThe Fundamentals of Signal Analysispunith666No ratings yet

- Coaxial Cable Delay MeasurementsDocument12 pagesCoaxial Cable Delay MeasurementsSrinivas CherukuNo ratings yet

- SOC Design Verif White PaperDocument44 pagesSOC Design Verif White PaperSrinivas CherukuNo ratings yet

- Convert Negative Pulses to Positive Pulses Using Comparators and TimersDocument3 pagesConvert Negative Pulses to Positive Pulses Using Comparators and TimersSrinivas CherukuNo ratings yet

- METMEL 43 PP2 MNAI SmolaDocument32 pagesMETMEL 43 PP2 MNAI SmolaSrinivas CherukuNo ratings yet

- Signal Processing and Data Transmission Using A FpgaDocument54 pagesSignal Processing and Data Transmission Using A FpgaSrinivas CherukuNo ratings yet

- De RatingDocument24 pagesDe RatingravindradsNo ratings yet

- Digital Signal Processing Designing For FPGA Architectures: Mariusz Rawski, Bogdan J. Falkowski, and Tadeusz ŁubaDocument23 pagesDigital Signal Processing Designing For FPGA Architectures: Mariusz Rawski, Bogdan J. Falkowski, and Tadeusz ŁubaSrinivas CherukuNo ratings yet