Professional Documents

Culture Documents

Intel 8086 Microprocessor

Uploaded by

Enock Omari0 ratings0% found this document useful (0 votes)

22 views3 pageserere

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documenterere

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

22 views3 pagesIntel 8086 Microprocessor

Uploaded by

Enock Omarierere

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 3

ELECTRICAL AND ELECTRONIC ENGINEERING

Intel 8086 Microprocessor

General Operation

The internal functions of the 8086 processor are partitioned logically into two processing units. The first is the

Bus Interface Unit (BIU) and the second is the !ecution Unit (U) as shown in the "loc# diagra$ of %igure &.

These units can interact directly "ut for the $ost part perfor$ as separate asynchronous operational processors.

The "us interface unit pro'ides the functions related to instruction fetching and (ueuing) operand fetch and

store) and address relocation. This unit also pro'ides the "asic "us control. The o'erlap of instruction pre*

fetching pro'ided "y this unit ser'es to increase processor perfor$ance through i$pro'ed "us "andwidth

utili+ation. Up to 6 "ytes of the instruction strea$ can "e (ueued while waiting for decoding and e!ecution.

The instruction strea$ (ueuing $echanis$ allows the BIU to #eep the $e$ory utili+ed 'ery efficiently.

,hene'er there is space for at least - "ytes in the (ueue) the BIU will atte$pt a word fetch $e$ory cycle. This

greatly reduces ..dead ti$e// on the $e$ory "us. The (ueue acts as a %irst*In*%irst*Out (%I%O) "uffer) fro$

which the U e!tracts instruction "ytes as re(uired. If the (ueue is e$pty (following a "ranch instruction) for

e!a$ple)) the first "yte into the (ueue i$$ediately "eco$es a'aila"le to the U.

The e!ecution unit recei'es pre*fetched instructions fro$ the BIU (ueue and pro'ides un*relocated operand

addresses to the BIU. 0e$ory operands are passed through the BIU for processing "y the U) which passes

results to the BIU for storage. 1ee the Instruction 1et description for further register set and architectural

descriptions.

%igure &2 3rchitectural layout

&

%igure -2 1i$plified 8086 0icroprocessor

0icroprocessors ha'e two $a4or co$ponents

The !ecution unit (U)

The Bus interface unit (BIU)

The Execution unit

(U) is used $ainly to e!ecute instructions. It contains a circuit called the arith$etic and logic unit (35U). The

35U perfor$s arith$etic (6) * ) 7) 8) and logic (39:) O;) 9OT) operations. The data for operations are stored

in circuit called ;egisters. 3 register is li#e a $e$ory location e!cept that we nor$ally refer to it "y a na$e

rather than address. The U has eight registers for storing data< their na$es are 3=) B=) >=) :=) 1I) :I) B?)

1? and %53G1 register.

Bus interfce unit !BI"#

BIU facilitates co$$unication "etween the U and $e$ory or I8O circuits. It is responsi"le for trans$itting

address) data) and control signals on the "uses. Its registers are na$ed >1) :1) 1) 11) I?< they hold addresses

of $e$ory locations. The I? contains the address of ne!t instruction to "e e!ecuted "y the U.

The E" n$ the BI"

3re connected 'ia an internal "us and they wor# together. ,hile the U is e!ecuting an instruction) the BIU

fetches up to si! "ytes of the ne!t instruction and places the$ in the instruction (ueue. This operation is called

Instruction pre*fetch. The purpose is to speed up the processor.

I%O &orts'

I8O de'ices are connected to the co$puter through I8O circuits. ach of these circuits contains se'eral register

called I8O ?orts. 1o$e are used for data while others are used control co$$ands. 5i#e $e$ory locations) the

I8O ports ha'e address and they are connected to the "us syste$. These addresses are #nown as I8O address and

can only "e use in input (I9) or output (OUT) instructions.

-

T(E )LAG REGI*TER !)R# AND BIT )IELD*

The flag register is a &6*"it register so$eti$es referred as the status register. 3lthough the register is &6*"it) not

all the "its are used. >onditional flags2 1i! (6) of the flags are called the conditional flags) $eaning that they

indicate so$e condition that resulted after an instruction was e!ecuted. These 6 are2 >%) ?%) 3%) @%) 1%) and O%.

The +6 ,its of the fl- re-isters'

C). the Crr/ )l-' This flag is set whene'er there is a carry out) either fro$ dA after an 8*"it operation) or

fro$ d&B after a &6*"it data operation.

&). the &rit/ )l-' 3fter certain operations) the parity of the resultCs low*order "yte is chec#ed. If the "yte has

an e'en nu$"er of &s) the parity flag is set to &< otherwise) it is cleared.

A). the Auxilir/ Crr/ )l-' If there is a carry fro$ dD to dE of an operation this "it is set to &) otherwise

cleared (set to 0).

0). the 0ero )l-' The @% is set to & if the result of the arith$etic or logical operation is +ero) otherwise) it is

cleared (set to 0).

*). the *i-n )l-' 01B is used as the sign "it of the "inary representation of the signed nu$"ers. 3fter

arith$etic or logical operations the 01B is copied into 1% to indicate the sign of the result.

T). the Trp )l-' ,hen this flag is set it allows the progra$ to single step) $eaning to e!ecute one instruction

at a ti$e. Used for de"ugging purposes.

I). Interrupt En,le )l-' This "it is set or cleared to ena"le or disa"le only the e!ternal interrupt re(uests.

D). the Direction )l-' This "it is used to control the direction of the string operations.

O). the O1erflo2 )l-' This flag is set whene'er the result of a signed nu$"er operation is too large) causing

the high*order "it to o'erflow into the sign "it.

%igure D2 8086 %lag ;egisters

D

You might also like

- Guru Tegh Bahadur Institute of Technology Question BankDocument12 pagesGuru Tegh Bahadur Institute of Technology Question Bankhakkem bNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Unit - 3 The Processor Organization StructureDocument16 pagesUnit - 3 The Processor Organization Structuretheresa.painterNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Unit 6: Intel 8051 MicrcontrollerDocument19 pagesUnit 6: Intel 8051 Micrcontrollerachuu1987No ratings yet

- 8085 MICROPROCESSOR ARCHITECTUREDocument36 pages8085 MICROPROCESSOR ARCHITECTUREKalai SelvanNo ratings yet

- Basics of Computers & Programming in C (Cst-105)Document22 pagesBasics of Computers & Programming in C (Cst-105)Rishabh GoyalNo ratings yet

- Design and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLDocument6 pagesDesign and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLIOSRjournalNo ratings yet

- Basic Computer Organization: Unit - 1Document9 pagesBasic Computer Organization: Unit - 1theresa.painterNo ratings yet

- 1.0 Computer Hardwar and Flow of Information 1.1 Basic Concepts of Computer ArchitectureDocument3 pages1.0 Computer Hardwar and Flow of Information 1.1 Basic Concepts of Computer ArchitectureAdam AlvarezNo ratings yet

- Sms 32 V 50Document107 pagesSms 32 V 50Mihret SaracNo ratings yet

- 1000 SAP ABAP Interview QuesDASDions and AnswersDocument19 pages1000 SAP ABAP Interview QuesDASDions and AnswersSreenith SathianNo ratings yet

- Ec53 - Computer Architecture and OrganizationDocument7 pagesEc53 - Computer Architecture and OrganizationmanjuesNo ratings yet

- SQL PL/SQL Triggers Types Joins Indexes Procedures Functions ExceptionsDocument25 pagesSQL PL/SQL Triggers Types Joins Indexes Procedures Functions ExceptionsSunil ReddyNo ratings yet

- Chapter 5 Exercises and Answers: Answers Are in BlueDocument5 pagesChapter 5 Exercises and Answers: Answers Are in BluemalikhassangulNo ratings yet

- Unit 6: Intel 8051 MicrcontrollerDocument16 pagesUnit 6: Intel 8051 Micrcontrollerachuu1987No ratings yet

- Parallel ProcessingDocument33 pagesParallel ProcessingShivansh tomarNo ratings yet

- Unit III CPU Organization PG 1-20Document20 pagesUnit III CPU Organization PG 1-20dhruwchanchal31No ratings yet

- Designing An ALU: 2.1 Operations of Our ALUDocument8 pagesDesigning An ALU: 2.1 Operations of Our ALUdarklord338No ratings yet

- Suresh Gyan Vihar University, Jaipur: " Telephone Directory System"Document22 pagesSuresh Gyan Vihar University, Jaipur: " Telephone Directory System"Sunny KhanNo ratings yet

- Sewp Zc413 Computer Organization & ArchitectureDocument16 pagesSewp Zc413 Computer Organization & Architectureshravanr500No ratings yet

- 8096Document23 pages8096Sreekanth PagadapalliNo ratings yet

- Intel (R) Integrator Toolkit Package Version 3.1.1 Release: Viewing NoteDocument11 pagesIntel (R) Integrator Toolkit Package Version 3.1.1 Release: Viewing NoteRamesh AnkathiNo ratings yet

- Application SQL Issues and TuningDocument11 pagesApplication SQL Issues and Tuningjoselara19No ratings yet

- Microprocessor: Navigation SearchDocument15 pagesMicroprocessor: Navigation SearchSreedhar PugalendhiNo ratings yet

- ADDRESSING METHODS AND INSTRUCTION EXECUTIONDocument13 pagesADDRESSING METHODS AND INSTRUCTION EXECUTIONtheresa.painterNo ratings yet

- Unit I Introduction To 8085 MicroprocessorDocument55 pagesUnit I Introduction To 8085 Microprocessorsheriffwoody123No ratings yet

- UNIT-1 Introduction To Embedded Systems Two Mark Questions and AnswersDocument30 pagesUNIT-1 Introduction To Embedded Systems Two Mark Questions and AnswersBharath RamanNo ratings yet

- Assignment of CAODocument17 pagesAssignment of CAODhiraj SardaNo ratings yet

- OratopDocument16 pagesOratopjonytapiaNo ratings yet

- Irjet V5i3295 PDFDocument3 pagesIrjet V5i3295 PDFchaitanya sNo ratings yet

- Chapter 2 Textbook 8086Document31 pagesChapter 2 Textbook 8086Madan R Honnalagere100% (1)

- MPI GTU Study Material E-Notes Unit-3 13052022115048AMDocument15 pagesMPI GTU Study Material E-Notes Unit-3 13052022115048AMmailsender787No ratings yet

- SAP Workflow Interview Questions & Answers: What Are The Different Types of WF Agents?Document5 pagesSAP Workflow Interview Questions & Answers: What Are The Different Types of WF Agents?mirza_2010No ratings yet

- CS1203 System Software UNIT I Question AnsDocument10 pagesCS1203 System Software UNIT I Question AnsChippyVijayanNo ratings yet

- Epic VliwDocument4 pagesEpic VliwJeffry PiaNo ratings yet

- What Is A PLCDocument13 pagesWhat Is A PLCsushant_jhawerNo ratings yet

- SQL Server Interview Questions: Explain The Use of Keyword WITH ENCRYPTION. Create A Store Procedure With EncryptionDocument10 pagesSQL Server Interview Questions: Explain The Use of Keyword WITH ENCRYPTION. Create A Store Procedure With EncryptionRicardo Aranibar LeonNo ratings yet

- AC58-AT58 Computer OrganizationDocument26 pagesAC58-AT58 Computer OrganizationSaqib KamalNo ratings yet

- CS2253 Computer Organization and Architecture Lecture NotesDocument181 pagesCS2253 Computer Organization and Architecture Lecture NotesRoselene RebeccaNo ratings yet

- 8086 Architecture: Dr. Mohammad Najim Abdullah 1. Hardware OrganizationDocument6 pages8086 Architecture: Dr. Mohammad Najim Abdullah 1. Hardware OrganizationDhiraj KapilaNo ratings yet

- Of Rhe B0BB and 8086 Microprocessors: Software ArchitectureDocument31 pagesOf Rhe B0BB and 8086 Microprocessors: Software Architecturefazal ahmadNo ratings yet

- Intel 8085Document6 pagesIntel 8085Prakhar SrivastavaNo ratings yet

- Introduction To Routing and Packet ForwardingDocument83 pagesIntroduction To Routing and Packet ForwardingJulio Cesar EMNo ratings yet

- Question Bank-Microprocessor and ApplicaionDocument38 pagesQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- SAP R/3 Architecture OverviewDocument66 pagesSAP R/3 Architecture OverviewSandyChinnaNo ratings yet

- M.tech Lab Manual JNTUHDocument80 pagesM.tech Lab Manual JNTUHSivarama Prasad PamarthyNo ratings yet

- Answers: Chapter 2: Processes - ExercisesDocument9 pagesAnswers: Chapter 2: Processes - Exercisessigie32No ratings yet

- Coprocessor 1Document50 pagesCoprocessor 1chandanayadav8490No ratings yet

- Lecture 1.1.4 (Computer Hardware Components - ALU, Registers, Memory)Document5 pagesLecture 1.1.4 (Computer Hardware Components - ALU, Registers, Memory)adityaNo ratings yet

- 2 Marks cs2252Document9 pages2 Marks cs2252Karthik KarthiksNo ratings yet

- MicrocomputerDocument26 pagesMicrocomputerChandan Mishra100% (1)

- AdbmsDocument36 pagesAdbmssilicongmaster7060No ratings yet

- Computer Laboratory Manual1Document58 pagesComputer Laboratory Manual1Sreekanth PagadapalliNo ratings yet

- Interrupts & PollingDocument10 pagesInterrupts & Pollingwazazzu3349No ratings yet

- Venkatesham.K E-Mail:: AchievementsDocument7 pagesVenkatesham.K E-Mail:: AchievementsbelvaisudheerNo ratings yet

- Intel 8085 8-Bit MicroprocessorDocument58 pagesIntel 8085 8-Bit MicroprocessorMOHSIN BHATNo ratings yet

- Cancer Testing and PreventionDocument68 pagesCancer Testing and PreventionEnock OmariNo ratings yet

- Generic Project Proposal TemplateDocument9 pagesGeneric Project Proposal TemplateCikaNo ratings yet

- Diceman Solutions MovDocument1 pageDiceman Solutions MovEnock OmariNo ratings yet

- Debt Collection Proposal: Prepared For: Prepared byDocument8 pagesDebt Collection Proposal: Prepared For: Prepared byEnock OmariNo ratings yet

- Student ProjectsDocument27 pagesStudent ProjectsVishal Shah100% (1)

- Wien Bridge.Document11 pagesWien Bridge.Enock OmariNo ratings yet

- Eee 2202 AssignmentDocument2 pagesEee 2202 AssignmentEnock OmariNo ratings yet

- Lag-Lead Compensator Design for Frequency Response SpecsDocument3 pagesLag-Lead Compensator Design for Frequency Response SpecsEnock OmariNo ratings yet

- MTS86C DebuggingDocument8 pagesMTS86C DebuggingEnock OmariNo ratings yet

- Memory MappingDocument7 pagesMemory MappingEnock OmariNo ratings yet

- FRICTION LOSSES IN PIPESDocument10 pagesFRICTION LOSSES IN PIPESEnock OmariNo ratings yet

- EEE 2215 Electromagnetics I CAT 2&3 2012-2013Document2 pagesEEE 2215 Electromagnetics I CAT 2&3 2012-2013Enock OmariNo ratings yet

- Eee 2202 AssignmentDocument2 pagesEee 2202 AssignmentEnock OmariNo ratings yet

- ICS 2206 Database System JujaDocument61 pagesICS 2206 Database System JujaEnock OmariNo ratings yet

- Programming Intel 8086Document2 pagesProgramming Intel 8086Enock OmariNo ratings yet

- Microprocessor IntroDocument12 pagesMicroprocessor IntroEnock OmariNo ratings yet

- Programming Intel 8086Document2 pagesProgramming Intel 8086Enock OmariNo ratings yet

- Ccna 1Document13 pagesCcna 1Amilcar Fernando Ferreira MartinsNo ratings yet

- 8086 Instr FormatDocument4 pages8086 Instr FormatEnock OmariNo ratings yet

- Assembler Exercise1Document3 pagesAssembler Exercise1Enock OmariNo ratings yet

- Microprocessor Information Transfer Instruction Flow: Electrical and Electronic EngineeringDocument3 pagesMicroprocessor Information Transfer Instruction Flow: Electrical and Electronic EngineeringEnock OmariNo ratings yet

- ELECTRICAL AND ELECTRONIC ENGINEERING Cache CachingDocument15 pagesELECTRICAL AND ELECTRONIC ENGINEERING Cache CachingEnock OmariNo ratings yet

- How Laser Printers WorkDocument7 pagesHow Laser Printers WorkPradeepNo ratings yet

- System Development: EditorDocument6 pagesSystem Development: EditorEnock OmariNo ratings yet

- Logic Gates & Com Bi National Logic DesignDocument64 pagesLogic Gates & Com Bi National Logic DesignEnock Omari100% (1)

- 2D ArraysDocument32 pages2D ArraysEnock OmariNo ratings yet

- Firefly Royu Wiring Devices Price List March 2016Document2 pagesFirefly Royu Wiring Devices Price List March 2016Alvin Lagasca100% (1)

- Tanker Pipeline SystemsDocument22 pagesTanker Pipeline SystemsLogovaz91% (11)

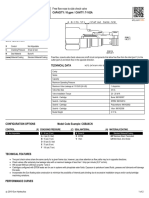

- Presettable synchronous BCD decade counter data sheetDocument11 pagesPresettable synchronous BCD decade counter data sheetIrvson SilveiraNo ratings yet

- Maintenance Schedule FormatDocument18 pagesMaintenance Schedule FormatAntoni100% (1)

- Evolution of Intel Microprocessors PDFDocument2 pagesEvolution of Intel Microprocessors PDFErikaNo ratings yet

- Terberg Fifth Wheel Service ManualDocument11 pagesTerberg Fifth Wheel Service ManualSyed Danyal SalamNo ratings yet

- 6 Operate Main and Auxiliary Machinery and Associated Control SystemsDocument5 pages6 Operate Main and Auxiliary Machinery and Associated Control SystemsridhoNo ratings yet

- Parallel Parking InstructionsDocument5 pagesParallel Parking Instructionsbra9tee9tiniNo ratings yet

- Substation Transformer Impedance Worksheet ###: Impedance in Per UnitDocument1 pageSubstation Transformer Impedance Worksheet ###: Impedance in Per UnitromoNo ratings yet

- Red Adapter DS - A0Document2 pagesRed Adapter DS - A0salunkheclNo ratings yet

- CircuitiKz ManualDocument62 pagesCircuitiKz ManualnospherathusNo ratings yet

- Addressing Modes in 8051 MicrocontrollerDocument20 pagesAddressing Modes in 8051 MicrocontrollerSia SiaNo ratings yet

- Type TBJ: ThermocoupleDocument2 pagesType TBJ: ThermocoupleRajishkumar RadhakrishnanNo ratings yet

- Tecumseh Model Lav35 40327k Parts ListDocument8 pagesTecumseh Model Lav35 40327k Parts ListTorney BenedictNo ratings yet

- Igbt & Sic Gate Driver Fundamentals: Enabling The World To Do More With Less PowerDocument35 pagesIgbt & Sic Gate Driver Fundamentals: Enabling The World To Do More With Less Powersuper_facaNo ratings yet

- STC WV30Document30 pagesSTC WV30ricardoulhoa75No ratings yet

- Rockwell JointerDocument18 pagesRockwell Jointernotjustsomeone100% (2)

- Hand Tool Checklist For All UnitDocument1 pageHand Tool Checklist For All UnitHariomNo ratings yet

- Test Water Pump Pressure 16H Motor GraderDocument2 pagesTest Water Pump Pressure 16H Motor GraderDouglas GomesNo ratings yet

- LH Door Trim Parts ListDocument1 pageLH Door Trim Parts ListNiten GuptaNo ratings yet

- Mazda Protege 1996Document36 pagesMazda Protege 1996ErasmoNieves100% (4)

- Gas Turbine Power PlantDocument7 pagesGas Turbine Power PlantYuvraj GogoiNo ratings yet

- CDHD2 ECT CAN fw2.15.x Rev.1.0 PDFDocument499 pagesCDHD2 ECT CAN fw2.15.x Rev.1.0 PDFDon BozarthNo ratings yet

- Catalog Specifications Caterpillar 7495 Electric Rope Shovel Rope CrowdDocument3 pagesCatalog Specifications Caterpillar 7495 Electric Rope Shovel Rope Crowdahmed zhranNo ratings yet

- LT Cable ScheduleDocument3 pagesLT Cable ScheduleSaquib Khan100% (2)

- Ec Lab: Course Name: Electrical Circuit Lab Course Code: CSE 133Document4 pagesEc Lab: Course Name: Electrical Circuit Lab Course Code: CSE 133Tarif Al MozahedNo ratings yet

- Tech QuizDocument3 pagesTech QuizMmohamed SuhailNo ratings yet

- SBU Micro-Switch 07-2017 enDocument3 pagesSBU Micro-Switch 07-2017 enshaonaaNo ratings yet

- Free-flow nose-to-side check valve technical detailsDocument2 pagesFree-flow nose-to-side check valve technical detailssnsnagarajanNo ratings yet