Professional Documents

Culture Documents

Institute of Engineering Studies (IES, Bangalore)

Uploaded by

Mirishkar S GaneshOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Institute of Engineering Studies (IES, Bangalore)

Uploaded by

Mirishkar S GaneshCopyright:

Available Formats

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

1

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

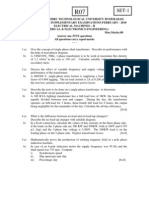

1. Sketch the output waveform for the circuit of Fig. 1. Also draw the variation of energy stored in

the capacitor as a function of time. Mark appropriate values. Take the diode to be ideal.

2. Determine

for the following network for the indicated input.

3. Determine the output wave for the network shown and calculate the output dc level and he

required PIV of each diode.

4. Determine

and

for the following network.

5. For the network shown (on page 190), determine the following parameters using the complete

hybrid equivalent model and compare with the results obtained using the approximate model in

which the effects of

and

are neglected.

(i)

and

(ii)

(iii)

and

(iv)

10 F

240 K

10 F

90

20 V

C = 1 F

R = 100 k

5V

f = 1 kHz

t

10

0

20

Fig. 1

0

2

4

6

8

t

10 V

5 V

1 3 5 7

5 V

C

10 F

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

2

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

The h parameters of the transistor are :

= 110,

= 1.6 k

6. Draw OPAMP circuits for

(i) Display driver

(ii) Instrumentation Amplifier Briefly describe the operation of these circuits.

7. For the transistor circuit shown below, determine the voltage transfer characteristic, assuming

= 0.2 and

, on 0.7 V.

8. In the transistor circuit shown below

Amp at 25C and doubles for every 10C

increase in temperature.

(i) Find maximum allowable value of

if the transistor is to remain cut off at 75 C. Assume

0.1V.

(ii) If

1.0V and

how high may the temperature increase before the transistor

comes out of cut off?

5V

450

100

640 360

+ 3.6 V

450

8 V

470 k

1 k

4.7 k

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

3

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

9. The input voltage

to the two level clipper shown below varies linearly from 0 to 150 V.

Sketch the output voltage to the same scale as the input voltage. Assume ideal diodes.

10. Three pole transfer function has all the three poles located at S = .A negative feedback is

added with feedback factor . Show that the system is unstable for |

8 where

is the dc

gain of the transfer function. Find the value of poles for |

= 8.10

11. Derive the expressions for the voltage gain

and the input resistance

of the amplifier shown.

Find the values of

and

for the following values of h parameters for the transistors :

= 0

12. For the feedback amplifier shown

(i) Draw the circuit without feedback but taking the loading of feedback network into account.

(ii) Find the feedback factor .

(iii) Assuming loop gain to be much larger than unity, find the voltage gain with feedback.

13. Draw the circuits for precision half wave and full wave rectifiers, using Op Amps. Explain

their working with the help of waveforms and equations.

14. A regenerative comparator (Schmitt Trigger) circuit is shown below.

(i) Derive expressions for upper threshold and lower threshold voltage,

and

respectively

and hence the value of hysteresis voltage

. Calculate

for the given values of

and

1 K

200 K

25 V

100 K

100 V

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

4

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

(ii) A sine wave with 2 V peak to peak amplitude and 1 kHz frequency is applied at the input

of the circuit. Plot the input and output waveforms.

15. For the circuit shown in fig. 15,

= 0.98,

= 0.96,

= 24,

and

mA.

Calculate the current

and

, the voltage

and the ratios

and

.

Neglect reverse saturation currents.

16. A silicon transistor with

0.8 V, B =

= 100,

= 0.2 V is used in the circuit

shown.

Find the minimum value of

for which the transistor remains in saturation.

17. A silicon single phase full wave bridge rectifier circuit is shown. Explain what happens if the

transformer and the load positions are interchanged.

18. For open loop transfer function A(s) =

a negative feedback is applied with a feedback factor . Find the value of A, (i) corresponding to

the breakaway, point, (ii) for which the system becomes unstable.

5 V

200 K

10 V

Fig. 15

= + 15 V

27 k

1 k

741

R =

| |

2

3

= 15 V

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

5

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

19. Calculate

for the circuit shown. Use

= 1000 ohms;

= 99 ;

0.

20. An amplifier with open loop voltage gain

= 1000 + 100 is available. It is required to have an

amplifier whose gain varies by no more than 0.2%. Find (i) reverse transmission factor of the

feedback network (ii) gain with feedback. Derive the formula you used.

21. Develop the voltage transfer function

for the amplifier shown.

22. Explain the current foldback characteristics of voltage regulators. Draw a circuit to realize the

current foldback characteristic in a low voltage regulator using 723 IC chip. Explain the working

of the circuit.

23. A two stage amplifier has the following parameters.

First stage Second stage

Voltage gain 12 20

Input resistance 500 ohms 80 K ohms

Equivalent Noise Resistance 1500 ohms 10 K ohms

Output Resistance 25 K ohms 1 M ohms

Calculate:

(i) The equivalent noise resistance of the two stage amplifier,

(ii) The noise figure of the amplifier if it is driven by a generator with output impedance 50 ohms.

24. Explain Neutralization and show how it can be realized.

The circuit shown has an internal and stray wiring capacitance of 20 pF. If

= 80 mH and

=

120 mH, determine to what value the neutralizing capacitance

should be set so as to neutralize

1 K

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

6

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

25. For the circuit shown below, calculate the Q point for both transistors. Assume silicon transistors,

= 0.7 V.

26. A power supply using half wave rectifier is to have an output dc voltage of 30 V, with a load

resistance of 500 . The ripple factor should not exceed 0.01. Find a suitable value for C.

Determine the peak diode current. Assume 50 Hz supply frequency.

27. A class B transformer coupled amplifier is to supply 4 W to a 10 load. the available supply

voltage

= 30 V. The transformer efficiency is 75%. Specify the output transformer and the

output transistors.

28. Determine the frequency of oscillation for the following circuit and the value of

needed to

maintain oscillations. Name the circuit.

29. Write PASCAL program for the dc analysis of Collector-to-Base bias circuit shown below. The

equation for Stability factor S of the circuit is to be included. Run your programme for two values

of

, 50, 150.

22 K

10 K

11 K

0.047 F

0.01 F

3.9 K

= 100

= 100

6.8 K

+ 12 V

82 K

68 K

33 K

100 K

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

7

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

Determine the values throretically and enter in your results.

30. For the common emitter amplifier shown in Fig. 30, draw the simplified high frequency

equivalent circuit and derive an approximate expression for the voltage gain and 3 dB frequency.

31. Calculate the output voltage

of the circuit shown in Fig. 31. The input voltages are

= 2.5 V

and

= 1 V.

32. (i) In the level shifter circuit shown in Fig. 32.1, calculate the value of R for

to become zero.

Assume

= 0.7 and

is very large.

(ii) Calculate

in the circuit shown in Fig. 32.2. Assume

to be large and neglect the base

current.

= 0.7 V.

12 V

8.6 V

+ 12 V

2.2 K

R

270

Fig. 32.1

2.5 V

1 V

3.3 K

1 K

2.2 K

1.5 K

Fig. 31

(Load Capacitance)

Fig. 30

1.98 k

86 k

0.7 V

Silicon transistor

= 50,150

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

8

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

33. Derive an expression for the stability factor of the circuit shown in Fig. 33.

34. An amplifier with open voltage gain

= 1000 100 is available. It is required to have an

amplifier whose voltage gain varies by no more than 0.1 percent.

(i) Find the value of feedback factor required.

(ii) Find the gain with feedback.

35. In the circuit shown in Fig. 35 calculate the value of the output current

for

= 5 V. If

of

is 0.3 V, calculate the maximum value of

that can be used in the circuit.

36. Draw the internal block diagram of an IC PLL NE 565 or equivalent. Explain how you will

realize a frequency multiplier to multiply an input frequency by a factor of 12 by using this PLL.

37.

1.8 K

+ 15 V

1 K

1 K

Fig. 35

V

V

Fig. 33

10 K

2.2 K

3.9 K

+ 12 V

4.7 K

1 K

100

Fig. 32.2

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

9

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

Find the voltage drop across each of the silicon junction diodes shown in the above figure at room

temperature. Assume that reverse saturation current flows in the circuit and the magnitude of the

reverse breakdown voltage is greater than 5 volts.

38. Sketch the impedance curve of a quartz crystal as a function of frequency.

39. Compare the merits and demerits of CMOS integrated circuit vis a vis those of bipolar

integrated circuits.

40. A transistor is connected in common emitter configuration as an amplifier. The parameters of the

transistor specified are:

= 25 A,

= 100 nA, beta = 100

Find its

and alpha, where symbols have their usual meaning.

41. Draw a neat circuit diagram of a voltage time base generator using a negative resistance switch.

Explain its operation in free running mode. Derive an expression for its frequency of oscillation.

42. A simple full wave bridge rectifier circuit has an input voltage of 240 V a.c r.m.s. Assume the

diodes to be ideal. Find the output d.c. current, d.c. voltage, r.m.s. values of output currents and

voltages and the peak inverse voltage that appears across the non conducting diode. Assume

load resistance to be 10 k.

43. In the circuit of Fig. 43 all the transistors are matched Si transistors. Symbols carry their usual

meaning.

(i) Find the expression of the current I in terms of

(ii) Calculate the value of I if

= 5 V,

= 6 V and R = 2.2 k. Take

= 0.7 V

and = 100.

(iii) What can be the maximum value of I? If

is varied between 1 k and 4 k give the range

of variation of I.

44. For the amplifier circuit shown in Fig. 44, Find the mid-band gain using small signal equivalent

circuit. Take early voltage of NPN transistor 95 V and that of PNP transistors as 76 V. forward

resistance of the diode is negligible and thermal equivalent voltage,

= 0.025 V, is large.

R I

Fig. 43

5 V

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

10

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

45. (i) Explain why bias stabilization is done in a bipolar junction transistor amplifier circuit.

(ii) Draw a fixed bias circuit and a self bias circuit using a BJT and mention typical component

values and supply voltages for your circuit.

(iii) Briefly explain the principle of operation of fixed bias and self bias circuits using BJT.

(iv) Compare the relative merits and demerits of fixed bias and self bias circuits using BJT from

the application point of view. Choose, with suitable reasons, the one which you would

recommend for cascaded amplifier operation.

46. Assume three identical non interacting amplifier stages are connected in cascade having an

overall upper cut off frequency of 10 kHz and lower cut off frequency of 10 Hz.

(i) Calculate the lower and upper cut off frequency of individual stages.

(ii) Derive the equations used in solving part (i) of this question.

47. Derive the transfer function of the circuit shown below and identify the function of the circuit.

48. Discuss the classification of amplifiers based on function, frequency, conduction angle, type of

coupling and load.

49. Draw the circuit of an astable multivibrator using p-n-p transistors, whose output is a square wave

with steep edges. Also draw the labeled waveforms at the collectors and bases of the two

transistors. Determine the frequency of the output waveform. Discuss its application as a voltage

to frequency converter.

50. In a R-C coupled amplifier, shown below, the BJT has

= 50. All bypass and coupling

capacitors are assumed to have zero reactance at the signal frequency find the quiescent

conditions and draw the small signal equivalent circuit, neglecting

and

R

C

Output

Input

4 k

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

11

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

51. Find the value of

in the amplifier circuit shown below such that the quiescent drain to ground

voltage becomes 10 V.

52. For the

amplifier shown below determine :

(i)

, where

(ii)

and

(iii)

,

Assume

= 0

= 100

= 1 k

= 0

53. For the circuit shown find

, the damping factor and the cut off frequency.

10 K

= 1 k

100 K

1 m

56 m

+ 24 V

3 m

= 2 mA

= 1V

=

2

.

2

k

24 V

50 k

1

0

k

1

0

k

= 3.8 k

= 1 k

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

12

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

54. The differential input operational amplifier shown below consists of a base amplifier of infinite

gain. Derive an expression for its output voltage,

.

55. A class C transistor amplifier is operating at 150 kHz. The transistor is conducting for 1 s in each

cycle. The saturation values for the transistor are :

= 100 mA;

0.2 V.

Assuming ideal pulse approximations and the output swinging over the entire load, find the

average power dissipation.

56. Explain the distinguishing features of astable, monostable and bistable multivibrator and give the

operational details of any one of them.

57. Consider silicon npn transistors for the following circuit.

If

is +1 V, what is the value of

? If

is changed to +3 V, what is the value of

?

What is the output voltage compliance (maximum voltage range that the output can swing when

the input is varied) of the circuit?

58. What is the class-D operation of power amplifier? Draw the circuit diagram of transistorized

class-D amplifier and explain its working

59. Consider the following circuit :

100

1 K

2 K

+ 12

1

2

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

13

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

The transistors have = 100. Determine input differential resistance

, overall voltage gain

and the worst case common mode rejection ratio if the two collector resistances are accurate

to within 1%.

60. Draw the circuit diagram of a Colpitts oscillator using transistor. Derive an expression for its

frequency of oscillations. Deduce the starting condition for this oscillator.

61. Consider the following circuit assume ideal op amps

and

.

If the load resistance is 500 what is the load voltage? If the load resistance is reduced to zero

what is the load current ?

62. A bipolar transistor has two junctions either one of which may be forward or reverse-biased.

Therefore, we have four modes of operations normal, cut-off, saturation and inverse region.

With the help of Ebers-Moll equations model the transistor circuit with a single set of equations

describing these four regions.

63. It is desired to operate the JFET shown in fig. below at

1.0 V,

= 4.0 V and

= 1

mA. Determine the value

and

.

1 K 1 K

1 K

+ 10 V

2

3

3

2

4

4

6

6

7

7

= 5 V

10 V

+ 10 V

+ 10 V

10 V

741

741

+

+

= 1000

= 1000

(Load)

10 K

150 K

10 K

150

200 K

R

1 = 1 mA

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

14

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

64. Determine the voltage gain

for the amplifier circuit shown below.

is the input voltage

between the gate terminal and ground. Neglect all capacitances.

65. Find the gains of the OP-AMP circuit for the two states of the gain-select input. The bilateral

switch in the ON state has negligible resistance.

66. Two identical silicon transistors with

= 50,

= 0.7 V at T = 25C

= 20.7 V,

and

are used in the circuit shown.

(1) Find the currents

at T = 25C

(2) Find

at T = 175C when = 98 and

= 0.22 V

= 100 k

74HC 4016

GAIN

SELECT

100 k

S

OUT

IN

= 100 k

47 k

33 k

10 k

R

= 30

5 k

10 V

500 k

S

G

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

15

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

67. Explain the operation of the circuit shown below :

What type of signal does it produce ? Determine the frequency of the output signal. How can we

change the frequency of the signal to 10 kHZ?

68. An amplifier with an open loop voltage gain of 500 delivers 10 W of output power at 5% second

harmonic distortion when the input signal is 5 mV. If 20 dB negative voltage is to remain 10 W,

determine

(i) The required input signal strength, and

(ii) The percent second harmonic distortion.

69. For the circuits shown in Fig. 69.1 and Fig. 69.2, sketch and explain the output waveforms.

Assume the diodes to be ideal.

70. What do you understand by thermal resistance of a BJT? Explain its significance. To ensure

thermal stability of a BJT, it is necessary that

. Justify by drawing the load line and

the constant power curves of the BJT.

71. The amplifier given in Fig. 71 uses an OPAMP. Assume its input impedance to be infinity,

output impedance to be zero and finite differential gain

(i) Obtain the expression for the feedback gain,

(ii) Calculate

, if A .

Fig. 69.1

R

D

2V

5 sin

t

V

V

t

T

o

Fig. 69.2

C

D

R

T/2

OPAMP 1

56 K

18 K

22 K

0.022 F

OPAMP 2

C

Assume

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

16

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

72. Determine the input power, output power and efficiency resulting in a class-B push-pull amplifier

providing a signal of 20 V peak to a 16 load, using a single supply of

= 30 V.

73. Explain the principle of operation of the short-circuit overload protection circuit shown in Fig. 73.

Find the limiting current

and the current that will flow under the short circuit condition in the

load. Assume

= 0.

Assuming

and

to be silicon diodes with

= 0.7 volt and

to be a silicon

transistor having

= 0.7 V, calculate the values of

and maximum load current, if

=

10 ,

= 15 volts and

= 100 .

74. What are the effects of negative voltage series feedback on the characteristics of an amplifier?

Derive an expression for input resistance of such an amplifier with feedback in terms of input

resistance without feedback and feedback factor.

75. For the bias circuit shown in Fig. 75, determine the value of

to yield an operating point at

=

5 mA. Assume

= 60,

= 0.7 V,

= 500 ,

= 100 and

V.

What is one advantage and one limitation of this type of biasing?

76. The circuit shown simulates the relation

. Determine the value of R.

Fig. 75

from amplifier

1

2

R

mR

Fig. 71

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

17

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

77. Minimum 3 identical RC high-pass sections connected in cascade are required in a phase-shift

oscillator. Justify. One such phase-shift oscillator is shown below. Why is R of one section

connected to virtual ground instead of actual ground?

Determine the value of

What should be the next higher number of high-pass sections connected in cascade? Draw the

corresponding circuit of the oscillator. Component values are not required.

78. Give pin numbers for the Trigger and Threshold of the timer 555.

In the circuit shown, assume

= 12 V and 0 as the possible outputs for

.

Draw the waveforms for the voltage

and

.

Determine the frequency of

waveform and the duty cycle.

79. In the circuit shown, the two transistors are matched. Find an expression for

in terms of

and

.

Assume

= 0.6 V and to be very large, calculate

and

.

Calculate

, when = 20.

10 k 1.5 k

1.4 k 0.3 k

6 V

6 V

R

C

1

6

2

4

8

3

5

7

555

R

C C C

R R

R

6 k

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

18

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

80. Draw the circuit of a passive band pass filter. Find its Transfer function and give the expressions

for its central frequency and bandwidth.

81. Draw the circuit of an inverting integrator using ideal OP Amp. Calculate the output voltage after

(i) .5 m sec (ii) 5 m sec of the application of an step input voltage of 50 mV. Take R = 50 , C =

0.1 F and the supply voltage of the op-amp is 15 V.

82. For the circuit shown the input voltage is given as

= 2 sin wt.

(i) Explain the operation of the circuit.

(ii) Draw the output waveshapc showing peak values for the cycles of the input when

, Take

0V.

(iii) Repeat part (ii) when

= 1 k .

83. Modify the circuit of part (a) so that it works as an all pass filter. Explain its working and obtain

the transfer function.

84. Draw the low-frequency small signal models of FET and bipolar junction transistor and compare

the two models. Justify the statement that FET is a much more idea simplifier than the bipolar

transistor at low frequencies.

85. For the circuit shown in Fig. 85, assume

= 100. Find if the transistor is in cutoff,

saturation or in the active region.

86. Describe how an FET can be used as a Voltage Variable Resistor (VVR).

87. The input and output of a causal LTI system is related by the differential equation

(i) Find the impulse response of the system.

(ii) What is the response of this system, if x(t) =

?

500

7 K

3 K

10 V

3 V

Fig.85

20 k

10 k

100 k

33 k

Institute Of Engineering Studies (IES,Bangalore)

Analog Electronics Old IES questions from Electronics & Telecom Department

For FREE Online tests logon to www.gateiespsu.com

19

Leading Institute for GATE/IES/JTO/PSUs in Bangalore (Branches@ Jayanagar & Malleshwaram)

Class room coaching | Online tests | Postal coaching | Discussion forums | Counselling

Join@ www.facebook.com/onlineies http://groups.google.com/group/onlineies

Contact: 99003 99699 E-mail: onlineies.com@gmail.com Site: www.onlineies.com

88. For a fullwave rectifier with a capacitor filter, show that the ripple voltage

is inversely

proportional to the capacitor C and is proportional to the load current

. Calculate the value of

when C = 100 F and

= 10 mA. The a.c. input voltage to the rectifier is given by v =

sin 314t.

89. Design a self bias circuit for a CE amplifier using an npn transistor with = 100. The other details

are :

= 12 V,

= 6 V,

= 4 mA.

90. Design an op-amp waveform generating circuit to produce the waveform given in Fig. 90. Explain

the circuit operation with other relevant waveform.

91. Design a Schmitt trigger circuit using an op-amp which has a maximum output voltage of 10V.

The hysteresis

should be = 0.4 V. Explain the working of the circuit with the transfer

characteristics. Use a reference voltage

= 2 V.

T =

1 ms

0.5

ms

+ 10 V

t

10 V

Fig. 90

You might also like

- Mock Gate III (Eee 2012)Document13 pagesMock Gate III (Eee 2012)Sree EesavoinaNo ratings yet

- Files Old GATE MOCKGATE Mock GATE-II (ECE-2012)Document14 pagesFiles Old GATE MOCKGATE Mock GATE-II (ECE-2012)Aniket BhowmikNo ratings yet

- Elect Machine Total 2012Document22 pagesElect Machine Total 2012NGOUNENo ratings yet

- ElectricalDocument10 pagesElectricalsivaeinfoNo ratings yet

- Electrical & Electronics: Institute of Engineering Studies Mock Test - I (EEE)Document10 pagesElectrical & Electronics: Institute of Engineering Studies Mock Test - I (EEE)Institute of Engineering Studies (IES)No ratings yet

- EEE3100S 2022 Tutorial 10 Memo - Power System Protection - KOADocument8 pagesEEE3100S 2022 Tutorial 10 Memo - Power System Protection - KOAStalin KosterNo ratings yet

- OutputDocument130 pagesOutput18131A0230 GEDDU TARUN KUMARNo ratings yet

- Modeling of Extra High Voltage 500 KV Transmission LinesDocument4 pagesModeling of Extra High Voltage 500 KV Transmission LineslgaungNo ratings yet

- ENEL2EEH1 - Electrical & Electronic EngineeringDocument7 pagesENEL2EEH1 - Electrical & Electronic EngineeringqanaqNo ratings yet

- Ge2151 Basic Electrical and Electronics EngineeringDocument4 pagesGe2151 Basic Electrical and Electronics EngineeringNithin PurandharNo ratings yet

- r05211002 Electrical TechnologyDocument7 pagesr05211002 Electrical TechnologySRINIVASA RAO GANTANo ratings yet

- Question Paper Code:: Reg. No.Document6 pagesQuestion Paper Code:: Reg. No.SindhujaSindhuNo ratings yet

- Endsem QN PaperDocument2 pagesEndsem QN Paper20EEE1004anjali yadavNo ratings yet

- BetDocument16 pagesBetShivendra SangwanNo ratings yet

- Electrical Meas May 2012Document8 pagesElectrical Meas May 2012Rama raoNo ratings yet

- Question Paper Code: 22115: B.E./B.Tech - Degree Examinations, April/May 2011 Regulations 2008Document5 pagesQuestion Paper Code: 22115: B.E./B.Tech - Degree Examinations, April/May 2011 Regulations 2008Vinodh GanesanNo ratings yet

- Electronics & Communication: Institute of Engineering Studies Mock Test-IDocument13 pagesElectronics & Communication: Institute of Engineering Studies Mock Test-IInstitute of Engineering Studies (IES)No ratings yet

- 209 Power System - 3Document4 pages209 Power System - 3sukirajNo ratings yet

- Bee Worksheet No-2 (2018-19)Document5 pagesBee Worksheet No-2 (2018-19)vikhli sallagargiNo ratings yet

- EE211 Exam S1-09Document8 pagesEE211 Exam S1-09abadialshry_53No ratings yet

- New Generalized Multilevel Current-Source PWM Inverter With No-Isolated Switching DevicesDocument6 pagesNew Generalized Multilevel Current-Source PWM Inverter With No-Isolated Switching DevicesHugo LeónNo ratings yet

- Power Systems-I PDFDocument4 pagesPower Systems-I PDFpadmajasivaNo ratings yet

- Applied Analogue Electronics QuestionsDocument5 pagesApplied Analogue Electronics QuestionsKerera DeograciousNo ratings yet

- Rr210303-Electrical-Engineering Feb 2007Document8 pagesRr210303-Electrical-Engineering Feb 2007devineni100% (1)

- 2 Cse Ece It Ec2151Document2 pages2 Cse Ece It Ec2151BIBIN CHIDAMBARANATHANNo ratings yet

- Rr220402 Electrical TechnologyDocument8 pagesRr220402 Electrical TechnologySrinivasa Rao GNo ratings yet

- School of Electrical & Computer Engineering, Oklahoma State University, Stillwater OK, 74078Document4 pagesSchool of Electrical & Computer Engineering, Oklahoma State University, Stillwater OK, 74078Centuro VinNo ratings yet

- GATE Analog Circuits BookDocument12 pagesGATE Analog Circuits BookFaniAli100% (1)

- Universiti Teknologi Mara Final Examination: Confidential EE/APR 2007/KJK559Document5 pagesUniversiti Teknologi Mara Final Examination: Confidential EE/APR 2007/KJK559Moso IINo ratings yet

- HAL Placement Paper Question Paper 20197Document12 pagesHAL Placement Paper Question Paper 20197Mukesh KumarNo ratings yet

- 9a02308 Electrical Mechines IDocument4 pages9a02308 Electrical Mechines IsivabharathamurthyNo ratings yet

- Faculty of Environment & Technology: DR H Nouri UFME7M-15-M Modern Power SystemsDocument5 pagesFaculty of Environment & Technology: DR H Nouri UFME7M-15-M Modern Power SystemsLibraryNo ratings yet

- ENEL2ELH1 - Electrical EngineeringDocument10 pagesENEL2ELH1 - Electrical EngineeringqanaqNo ratings yet

- King Fahd University of Petroleum & Minerals: Exam I MajorDocument4 pagesKing Fahd University of Petroleum & Minerals: Exam I MajorMd.Arifur RahmanNo ratings yet

- Tutorial 7 DC Machines IIDocument2 pagesTutorial 7 DC Machines IIAkshat SharmaNo ratings yet

- CBPSDDocument55 pagesCBPSDNimisha GoyalNo ratings yet

- Power Electronics Question BankDocument120 pagesPower Electronics Question BankAnonymous gud2po56% (18)

- R07aec13 - Electrical TechnologyDocument5 pagesR07aec13 - Electrical TechnologymdabdulhaqNo ratings yet

- Evaluation of Radiated Emissions From Printed CircDocument29 pagesEvaluation of Radiated Emissions From Printed CircMoin BiswasNo ratings yet

- Eee Sem 7 Ee2404lmDocument36 pagesEee Sem 7 Ee2404lmAnonymous gAVMpR0aNo ratings yet

- ExercisesDocument2 pagesExercisesAnalyn ZuluetaNo ratings yet

- ECA Exams Term 1Document2 pagesECA Exams Term 1Fred RotichNo ratings yet

- University of Moratuwa, Sri Lanka: B. Sc. Engineering Degree Course Final Part III Examination 1996/97Document3 pagesUniversity of Moratuwa, Sri Lanka: B. Sc. Engineering Degree Course Final Part III Examination 1996/97Sarinda JayasingheNo ratings yet

- Current of Electricity Tutorial 2011 SolutionDocument10 pagesCurrent of Electricity Tutorial 2011 SolutionbandagecookieNo ratings yet

- Power Systems and Smart Grids Exam QuestionsDocument10 pagesPower Systems and Smart Grids Exam QuestionsNDA BandNo ratings yet

- 3-2 Analysis of A Power System in Per Unit: StepsDocument9 pages3-2 Analysis of A Power System in Per Unit: Stepsحسن علي جاسمNo ratings yet

- Ec I Model QPDocument3 pagesEc I Model QPNoddy SenNo ratings yet

- Power Systems Computer Methods DocumentDocument7 pagesPower Systems Computer Methods DocumentsuhrudkumarNo ratings yet

- 07a40202 Electrical Machines - IIDocument8 pages07a40202 Electrical Machines - IISRINIVASA RAO GANTANo ratings yet

- UEE403 Feb2004Document3 pagesUEE403 Feb2004sliit2008No ratings yet

- BIS Scientist B Electrical Sample Question Paper Bureau of Indian StandardsDocument17 pagesBIS Scientist B Electrical Sample Question Paper Bureau of Indian StandardsRakesh SahNo ratings yet

- Faculty of Environment & Technology: Hassan Nouri UFME7M-15-M Modern Power SystemsDocument5 pagesFaculty of Environment & Technology: Hassan Nouri UFME7M-15-M Modern Power SystemsLibraryNo ratings yet

- Merged DocumentDocument25 pagesMerged DocumentAshokAbiNo ratings yet

- U20EE201 - CT - Model QPDocument4 pagesU20EE201 - CT - Model QPvinothkumarNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- LTE Evolution: Feedback Equalization & V-BLASTDocument1 pageLTE Evolution: Feedback Equalization & V-BLASTMirishkar S GaneshNo ratings yet

- Hostel For Phd&m.tech.Document8 pagesHostel For Phd&m.tech.Mirishkar S GaneshNo ratings yet

- MATLAB Implementation of Yagi-Uda Antenna Using Circuit Theory ApproachDocument5 pagesMATLAB Implementation of Yagi-Uda Antenna Using Circuit Theory Approachkinny1974No ratings yet

- Template Styles GuideDocument1 pageTemplate Styles GuideMirishkar S GaneshNo ratings yet

- Text or Image Watermarking For Real Time Copy Right ProtectionDocument1 pageText or Image Watermarking For Real Time Copy Right ProtectionMirishkar S GaneshNo ratings yet

- Deepak - CV RESUME Template - Files - DeepakPalDocument2 pagesDeepak - CV RESUME Template - Files - DeepakPalSathyamoorthy VenkateshNo ratings yet

- Deepak - CV RESUME Template - Files - DeepakPalDocument2 pagesDeepak - CV RESUME Template - Files - DeepakPalSathyamoorthy VenkateshNo ratings yet

- Ijea 108000083 20131205 195220Document8 pagesIjea 108000083 20131205 195220Mirishkar S GaneshNo ratings yet

- MATLAB Implementation of Yagi-Uda Antenna Using Circuit Theory ApproachDocument5 pagesMATLAB Implementation of Yagi-Uda Antenna Using Circuit Theory Approachkinny1974No ratings yet

- Rsytjvkjblkn, HCGJHVM NKJ CJHKJJHKJ GJGKGGJK FJHHGKJHLKHJ KJKJ' FJHKJKJDocument1 pageRsytjvkjblkn, HCGJHVM NKJ CJHKJJHKJ GJGKGGJK FJHHGKJHLKHJ KJKJ' FJHKJKJMirishkar S GaneshNo ratings yet

- GisDocument1 pageGisMirishkar S GaneshNo ratings yet

- Class Xii - Differntiation & Integration Formulae.Document1 pageClass Xii - Differntiation & Integration Formulae.Mandeep Singh Plaha59% (22)

- 44-0430 - PHD - ECEDocument3 pages44-0430 - PHD - ECEMirishkar S GaneshNo ratings yet

- 44-0430 - PHD - ECEDocument3 pages44-0430 - PHD - ECEMirishkar S GaneshNo ratings yet

- PSoC Portrait Browef LRESDocument12 pagesPSoC Portrait Browef LRESMirishkar S GaneshNo ratings yet

- Broacher Majestic Vistas, Attapur.Document8 pagesBroacher Majestic Vistas, Attapur.Mirishkar S GaneshNo ratings yet

- Andhra Bank PO Solved Paper 2009Document30 pagesAndhra Bank PO Solved Paper 2009Shashvat VashishthaNo ratings yet

- Integration Formulas: 1. Common IntegralsDocument5 pagesIntegration Formulas: 1. Common IntegralssiegherrNo ratings yet

- IBPS PO Solved Paper 2012Document39 pagesIBPS PO Solved Paper 2012Rohit ShivnaniNo ratings yet

- Digital Signal Processing: Lab ManualDocument147 pagesDigital Signal Processing: Lab ManualFaa MahveenNo ratings yet

- 2006-13 Duetal PaperDocument5 pages2006-13 Duetal PaperTiền Hoàng VănNo ratings yet

- Multilevel InvertersDocument13 pagesMultilevel Inverterssyfullahnel100% (1)

- Chapter 2: Operating-System Structures!Document53 pagesChapter 2: Operating-System Structures!managementNo ratings yet

- FSK - Signals and DemodulationDocument8 pagesFSK - Signals and DemodulationMatthew CarterNo ratings yet

- Two-Element Plasma Antenna Array SimulationDocument6 pagesTwo-Element Plasma Antenna Array SimulationMirishkar S GaneshNo ratings yet

- B.tech B.pharm 4-2 Exams Revised ScheduleDocument2 pagesB.tech B.pharm 4-2 Exams Revised ScheduleMirishkar S GaneshNo ratings yet

- Govt. of India Centre For Electronics Test Engineering: HyderabadDocument1 pageGovt. of India Centre For Electronics Test Engineering: HyderabadMirishkar S GaneshNo ratings yet

- Touch-Tone Dialing: Dual Tone Multi-Frequency (DTMF) System EE2013 ProjectDocument10 pagesTouch-Tone Dialing: Dual Tone Multi-Frequency (DTMF) System EE2013 ProjectMirishkar S GaneshNo ratings yet

- 4-2 - R09 Eee JntuhDocument4 pages4-2 - R09 Eee JntuhSatishKumarNo ratings yet

- Korg D-Series RecordersDocument17 pagesKorg D-Series RecordersapkoumnasNo ratings yet

- SR489 Setting FileDocument9 pagesSR489 Setting FileVarun SharmaNo ratings yet

- RichAuto Motion Control System ManualDocument89 pagesRichAuto Motion Control System ManualSebastian Almaraz UnzuetaNo ratings yet

- RRU Installation GuideDocument19 pagesRRU Installation GuideLuckyNo ratings yet

- SIRIUS Innovations Selection Guide - Pwsa-A880m-0411 - Switching - Devicesr PDFDocument4 pagesSIRIUS Innovations Selection Guide - Pwsa-A880m-0411 - Switching - Devicesr PDFEscape ExistNo ratings yet

- NetBSD peripheral-side USB support frameworkDocument7 pagesNetBSD peripheral-side USB support frameworkgrumpykissNo ratings yet

- CHS Exam Final LubethDocument3 pagesCHS Exam Final LubethLubeth CabatuNo ratings yet

- PHYS 122 Lecture 4 (Revised)Document18 pagesPHYS 122 Lecture 4 (Revised)BENJAMIN MALUWAZINo ratings yet

- EET455 - M2 Ktunotes - inDocument62 pagesEET455 - M2 Ktunotes - inrajkumarNo ratings yet

- Icm7555 56Document13 pagesIcm7555 56she rifNo ratings yet

- WI-LST-HSE-003-01 CLYDE CRANE - CHECK LIST PRIOR HEAVY LIFT OPERATIONS ElectricalDocument2 pagesWI-LST-HSE-003-01 CLYDE CRANE - CHECK LIST PRIOR HEAVY LIFT OPERATIONS ElectricalCiprian MihailaNo ratings yet

- Yamaha DSP Ax1 RX v1Document103 pagesYamaha DSP Ax1 RX v1Ken SewallNo ratings yet

- DR Beck Insulating VarnishDocument6 pagesDR Beck Insulating VarnishAnonymous HtYWpEtXGzNo ratings yet

- VLT Micro SeriesDocument88 pagesVLT Micro SeriesEdwinNo ratings yet

- 2017-10-01 Siltech Retail Pricelist Met BTW - 0 PDFDocument13 pages2017-10-01 Siltech Retail Pricelist Met BTW - 0 PDFانس الكردي0% (1)

- Space MouseDocument16 pagesSpace MousePranoy RajNo ratings yet

- Department of ECE Module Iv Finite Word Length EffectsDocument28 pagesDepartment of ECE Module Iv Finite Word Length EffectsSuraaj Sakthi KumarNo ratings yet

- Sepura Terminals InsightDocument20 pagesSepura Terminals InsightDyego FelixNo ratings yet

- ESAD Data Sheet 38999 Det Output 5jun2017Document1 pageESAD Data Sheet 38999 Det Output 5jun2017Nasr PooyaNo ratings yet

- Address ConstantDocument2 pagesAddress ConstantGirish KumarNo ratings yet

- Method Statement GIS HV TestDocument28 pagesMethod Statement GIS HV Testnayagammailbox75% (4)

- TDS - Tassel Neo FloodDocument1 pageTDS - Tassel Neo Floodmurugan.ragulNo ratings yet

- Ordem de Graduação RELÉ SEL 351-6: Relay Identifier Terminal IdDocument14 pagesOrdem de Graduação RELÉ SEL 351-6: Relay Identifier Terminal IdReinan AssisNo ratings yet

- 74HC32 74HCT32: 1. General DescriptionDocument17 pages74HC32 74HCT32: 1. General Descriptionvik_mdNo ratings yet

- SKYAIRDocument23 pagesSKYAIRTatiana DiazNo ratings yet

- Product Link / Machine: Product Link PL631 and PL641 PLE601, PLE631 and PLE641Document2 pagesProduct Link / Machine: Product Link PL631 and PL641 PLE601, PLE631 and PLE641Daniel Pacheco LLantoyNo ratings yet

- Denison Hydraulics Pressure Controls - Flanged Type: Series R5with 2 PortsDocument15 pagesDenison Hydraulics Pressure Controls - Flanged Type: Series R5with 2 PortsMario SouzaNo ratings yet

- Advantages of Automatic Switching System Over The Manual ExchangesDocument9 pagesAdvantages of Automatic Switching System Over The Manual ExchangesWodari HelenaNo ratings yet

- PGCIL GIS Rev-5A PDFDocument105 pagesPGCIL GIS Rev-5A PDFPeyush JainNo ratings yet

- PLUS+1® Compliant: OX024-x10 Function BlockDocument16 pagesPLUS+1® Compliant: OX024-x10 Function BlockGuima_df100% (1)