Professional Documents

Culture Documents

Automatic Code Generation

Uploaded by

Bharggav Shorthand Classes0 ratings0% found this document useful (0 votes)

46 views13 pages1. Adjustment of the simulation-tested controller model which is in its purest form (and thus can be represented by operations in floating point arithmetic) into an implementation model whose system of arithmetic matches with that of the specified target processor (for example, 16 bit fixed point). And the adjustment should be such that any imprecision arising out of the use of the different types of arithmetic is kept to the minimum.

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Document1. Adjustment of the simulation-tested controller model which is in its purest form (and thus can be represented by operations in floating point arithmetic) into an implementation model whose system of arithmetic matches with that of the specified target processor (for example, 16 bit fixed point). And the adjustment should be such that any imprecision arising out of the use of the different types of arithmetic is kept to the minimum.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

46 views13 pagesAutomatic Code Generation

Uploaded by

Bharggav Shorthand Classes1. Adjustment of the simulation-tested controller model which is in its purest form (and thus can be represented by operations in floating point arithmetic) into an implementation model whose system of arithmetic matches with that of the specified target processor (for example, 16 bit fixed point). And the adjustment should be such that any imprecision arising out of the use of the different types of arithmetic is kept to the minimum.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 13

CHAPTER 4

AUTOMATIC CODE GENERATION

4.1 Introduction

4.1.1 Model-based design

Model-based design is a mathematical and visual method for complex control system design. The

main steps in model-based design approach are:

1. Plant modelling: It is the creation of an executable mathematical model based on either first

principles that underlie the specified plants dynamics, or by processing sample raw data obtained from

the specified plant through mathematical algorithms.

2. Controller analysis and synthesis for the executable plant model.

3. Simulation studies: The estimation of the worth of the designed controller by integrating it into

the plant model and studying the supposed system models response to complex, time-varying inputs.

Its most important use lies in allowing modelling errors to be found at early stages of design effort.

4. Deployment: It is the practical implementation phase of the simulation-tested controller model

on an embedded processor by either manual coding taking help from the various blocks of the created

model regarding dataflow and signal flow or by autocoding (automatic generation of code) for the

processor from the model based design environment itself with the help of a compiler. It then involves

an iterative debugging process by analysing results on the actual target and updating the controller

model.

4.1.2 Model-based automatic code generation

As can be seen above, the possibility of automatic code generation for specified target processors

directly from the design environment is a feature that stands as one of the most important benefits of

model based design. This is accomplished in the following way.

1. Adjustment of the simulation-tested controller model which is in its purest form (and thus can

be represented by operations in floating point arithmetic) into an implementation model whose system

of arithmetic matches with that of the specified target processor (for example, 16 bit fixed point). And

the adjustment should be such that any imprecision arising out of the use of the different types of

arithmetic is kept to the minimum.

2. The prepared implementation model which essentially exists in its bare form in the design

environment as a graphical modelling language code is then translated into a high level programming

language such as C, using a compiler that is termed the automatic code generation tool or autocode tool.

3. The generated C code is then compiled and linked to get the machine code before loading it to

the target processor from the host PC.

Also, owing to the limited resources of the embedded processors, the machine code generated has to

be efficient with respect to aspects such as execution speed. This code optimisation can be achieved by

the classical compiler that translates source code into embedded code. However, the autocode compiler

itself can perform some optimisation techniques on the implementation model that cannot be done

using the source code compiler, again rendering the model based design approach highly beneficial.

The best example is an interblockoptimisation which is a combination of different Simulink portions,

that is not possible with classical source code optimisation.

4.2 Texas Instruments Support from Embedded Coder

MATLAB Coder, Simulink Coder, and Embedded Coder

generate C/C++ code that can be

compiled using Texas Instruments Code Composer Studio

integrated development environment and

executed on TI processors. Embedded coder is a Mathworks proprietary autocode tool for embedded

processors. Embedded Coder helps to easily configure the code generated

from MATLAB

and Simulink

algorithms to control software interfaces, optimize execution

performance, and minimize memory consumption.

Embedded Coder provides additional support packages for various TI processors, IDEs, and Real Time

Operating Systems. The features vary within each support package and may include automated build

and execution, processor-optimized code, the ability to perform processor-in-the-loop (PIL) tests

with execution profiling, block libraries for on-chip and on-board peripherals, and deployment support

using bare-board or Real Time Operating Systems.

The TI processor families compatible with Embedded Coder C-code generation include

microcontrollers like MSP430, ARM based processors like Stellaris

Cortex-M3, Sitara, and

Digital Signal Processors like the C2000 family, C5000 family, etc.

In the case of the DSPs of C2000 family (whose member, the TMS320F2812 is used in the current

project for induction motor control), the block libraries for on-chip and on-board peripherals such as

ADC, digital I/O, PWM, etc. are provided by the Embedded Coder support package.

Figure 4.1 Simulink block library for C281x processors

For CCS v3.3, Embedded Coder also supports IDE automation and project generation.

4.3 System requirements

1. MATLAB

2. Simulink

3. Embedded Coder with support package for TI C2000 processors

4. MATLAB Coder

5. Simulink Coder

6. TI Code Composer Studio IDE

7. Visual C++ with license for dotnet

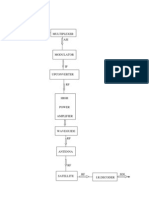

4.4 Work Flow

The outline of the basic work flow employed during this project for C-code generation and testing

using Embedded Coder is as follows:

1. Create a Simulink model employing the blocks from the Embedded Coder support package and

other necessary Simulink blocks so as to represent the functionality the DSP is intended to achieve.

2. Set the configuration parameters of the model in an appropriate manner.

3. Build the model to establish a link between MATLAB and CCS, generate the required code and

test it on the processor.

Each of these steps is now explained in detail.

4.4.1 Creating a Simulink model

1. A Simulink model is created using PWM, ADC and other required blocks.

2. One can also set test points for different signals with suitable identifiers to facilitate the creation

of variables in the generated code with the same names as the given identifiers in the CCS IDE for easy

debugging. This can be done by right-clicking on the line the intended signal flows through, and

enabling a test point in the dialog box that appears.

4.4.2 Setting the configuration parameters

1. Click on the Configuration parameters in the Simulation tab of the saved Simulink model.

2. Click on the Solver on the top of the parameters listed on the left side and set the simulation

start and stop times to 0 and inf respectively.

3. The solver type must be specified as fixed-step discrete with a discrete solver (one with no

continuous states) for CCS support from MATLAB to be possible, for digital signal processors which

essentially can process data only in discrete intervals. The fixed-step size or fundamental sample time

can be specified as a suitable value or can be left auto.

Figure 4.2 Configuration Parameters/Solver: Set discrete fixed step solver and sample time

4. Now click on the Hardware Implementation option, and specify the details such as Device

vendor, Device type, Emulation Hardware, etc.

5. Click on the Code Generation. The system target file that should be selected from a list of files

there is idelink.ert.tlc. (ert refers to embedded real time, .tlc, idelink )

6. Finally, as part of the most important step in preparing the Simulink model for code generation,

click on the CoderTarget under Simulation Target. Ensure that a JTAG emulator is connected to the

host PC at this end and a powered DSP board at the other, as no CoderTarget option appears otherwise

and consequently, Embedded Coder fails to build the model.

Figure 4.3 Configuration Parameters/Code Generation: Set System target file and language

7. The board properties, memory sections and the properties of the peripherals can be set under the

target hardware resources. Two configurations of board usage are worked with, in this project. During

the testing phase when intense debugging is required, the code is run in RAM locations, enabling the

CCS to exchange information with the board through the JTAG and updating watch variables

dynamically as in DSP. In the second configuration, the code is flashed into the board at the end for

field testing and running of the induction motor.

8. For RAM programming, the board type must be selected as C2000 Custom. The processor is

then selected (C2812). For flash programming, SD F2812 boot from flash is selected as board type.

Figure 4.4 Code Generation/Coder Target/Target Hardware Resources: Settings for RAM and flash

9. In the case of flash programming, the flash programmer enable in the flash loader section of

peripherals must be set to Erase, Program, Verify mode. It should also be verified that two new

memory banks appear in the memory section.

Figure 4.5 ZONE6P and ZONE6D-two new memory banks shown for flash

Figure 4.6 CoderTarget/Target hardware resources/Peripherals: Flash programmer mode in the case

of RAM execution

Figure 4.7 CoderTarget/Target hardware resources/Peripherals: Flash programmer mode in the case of

flash execution

4.4.3 Building the model

1. Once the parameters are set, click on the build option in the main Simulink model.

2. Depending on the parameters selected in the Configuration parameters window, this activates

the CCS for generating code and testing it by executing it in either RAM locations of the DSP or

flashed into the DSP for field testing.

3. In all the cases where the code is being executed in RAM locations of the DSP, we can debug it

normally, by employing various features of the CCS, such as watching variables in the watch window.

Figures 4.8

Variables inside watch window

4.5 Simulink Block Diagram for Code Generation

The Simulink block diagram for code generation for PWM pulses of open loop V/f control is shown

next.

In the figure, the Target frequency subsystem, takes the scaled target frequency (50Hz corresponds to

10V and 5Hz to 1V) as input from ADC B3. The frequency rampup subsystem generates a frequency

value ramping up from 5Hz to the target frequency in a period of 20 seconds. The modulating index is

also varied proportional to the frequency, thus helping to keep V/f ratio constant as required for open

loop V/f control. The Modulating Waves subsystem generates sine waves/ space vector based

modulating waves to the PWM block.

A speed estimation mechanism is also incorporated taking the sensed stator currents and the input

voltage to induction motor (proportional to modulating waves) as the inputs and various parameters

like rotor flux, rotor flux position, and eventually rotor speed and the synchronous speed are estimated.

Figure 4.9 Simulink model created for code generation

4.6 Description of Some Important Blocks

4.6.1 PWM block

The PWM block in the C281x library of the Embedded Coder support package for TI C2000

processors depicts the event manager modules compare units, counter units, the output logic

required for pulse generation (active high/low) and the necessary control registers thereof. It can

be used as either PWM 1 through 6 (Event manager A), or as PWM 7 through 12 (Event

manager B) by setting the parameters associated with the block.

The input ports to the block acquire the values of modulating signals (sinusoidal or space vector

based) applied and continually update the compare registers. The counter registers (whose

values represent carrier waves) run continuously in the processor according to the parameters

set such as waveform period, counting mode, dead band intended, active high/low specification,

etc. Comparison takes place inside the processor to give required PWM signals as the output.

The start of conversion signal that needs to be sent to ADC can be specified to be at counter

underflow, period match or compare match.

Formulae used

Wave form period in clock cycles = HSPCLK / Intended Carrier wave frequency

For deadband, the parameters dead band period and prescaler should be set such that

Deadband period *Deadbandprescaler = deadband time (in seconds) * HSPCLK

Figure 4.10.1 Configuration of PWM block

Figure 4.10.2Configuration of PWM block

4.6.2 ADC block

The C281x ADC blocks configure to perform analog- to-digital conversion to the selected ADC

input pins. The ADC block represents the on-chip ADC of TMS320F2812. The ADC block

outputs digital values representing the analog input signal and stores the converted values in

result register of digital signal processor. It has fields to set important parameters like the event

manager to trigger Start of Conversion, operating module (A or B), conversion mode

(sequential or simultaneous), sample time, etc.

Figure 4.11 Configuration of ADC block

4.6.3 Target Frequency block

The Target frequency block attains input from ADC block. The input port and the constant with

a value of 2048 are subtracted to achieve required output. The output is multiplied with a value of

10/2048 such that it indicates the initial position of motor. The output of product is connected to the

minimum frequency of motor.

4.6.4 Frequency Rampup

The Frequency rampup contains three inputs viz..output of Target frequency,time ramp,variable

integer delay. The minimum delay time is given by variable interger delay.

4.6.5 Modulating Waves

The output of frequency rampup is the input for sine block. The block diagram for moduating

wave is shown below.

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Important Sections and Orders of Civil Procedure CodeDocument10 pagesImportant Sections and Orders of Civil Procedure CodeBharggav Shorthand ClassesNo ratings yet

- 11 - What Is The Difference Between International Court of Justice and Permanent Court of Arbitration?Document7 pages11 - What Is The Difference Between International Court of Justice and Permanent Court of Arbitration?Bharggav Shorthand ClassesNo ratings yet

- Imp. Definitions Contd.... 3Document2 pagesImp. Definitions Contd.... 3Bharggav Shorthand ClassesNo ratings yet

- Imp. Definitions Contd.... 4Document4 pagesImp. Definitions Contd.... 4Bharggav Shorthand ClassesNo ratings yet

- Pil 7-10Document7 pagesPil 7-10Bharggav Shorthand ClassesNo ratings yet

- About SG 2Document1 pageAbout SG 2Bharggav Shorthand ClassesNo ratings yet

- VowelsDocument1 pageVowelsBharggav Shorthand ClassesNo ratings yet

- Law Relating To WomenDocument7 pagesLaw Relating To WomenBharggav Shorthand ClassesNo ratings yet

- D 10Document1 pageD 10Bharggav Shorthand ClassesNo ratings yet

- Whyus?Document1 pageWhyus?Bharggav Shorthand ClassesNo ratings yet

- Criminal CaseDocument2 pagesCriminal CaseBharggav Shorthand ClassesNo ratings yet

- Pil - 4-6Document5 pagesPil - 4-6Bharggav Shorthand ClassesNo ratings yet

- Moot ProblemDocument1 pageMoot ProblemBharggav Shorthand ClassesNo ratings yet

- CCDocument2 pagesCCBharggav Shorthand ClassesNo ratings yet

- Pil Strategy in Advancing The RightsDocument14 pagesPil Strategy in Advancing The RightsBharggav Shorthand ClassesNo ratings yet

- Bhaskar Law CollegeDocument8 pagesBhaskar Law CollegeBharggav Shorthand ClassesNo ratings yet

- Bona Vacantia - Legal Maxim: Literal MeaningDocument2 pagesBona Vacantia - Legal Maxim: Literal MeaningBharggav Shorthand ClassesNo ratings yet

- Suryam Years,: One OneDocument2 pagesSuryam Years,: One OneBharggav Shorthand ClassesNo ratings yet

- Bharggav Institute of Typing & Shorthand: Plot No.78, Jayanagar Colony, Kukatpally, Hyderabad-500072Document1 pageBharggav Institute of Typing & Shorthand: Plot No.78, Jayanagar Colony, Kukatpally, Hyderabad-500072Bharggav Shorthand ClassesNo ratings yet

- Alt. Forms PassageDocument1 pageAlt. Forms PassageBharggav Shorthand ClassesNo ratings yet

- Payment of CompensationDocument6 pagesPayment of CompensationBharggav Shorthand ClassesNo ratings yet

- 72nd Republic DayDocument3 pages72nd Republic DayBharggav Shorthand ClassesNo ratings yet

- Land ReformsDocument5 pagesLand ReformsBharggav Shorthand ClassesNo ratings yet

- Bharggav Institute of Typing & Shorthand: Plot No.78, Jayanagar Colony, Kukatpally, Hyderabad-500072Document1 pageBharggav Institute of Typing & Shorthand: Plot No.78, Jayanagar Colony, Kukatpally, Hyderabad-500072Bharggav Shorthand ClassesNo ratings yet

- Bharggav Shorthand ClassesDocument241 pagesBharggav Shorthand ClassesBharggav Shorthand ClassesNo ratings yet

- DM SpeechDocument2 pagesDM SpeechBharggav Shorthand ClassesNo ratings yet

- Muslim Law - SnippetsDocument15 pagesMuslim Law - SnippetsBharggav Shorthand ClassesNo ratings yet

- Bharagav Shorthand Classes - Stenography TrainingDocument4 pagesBharagav Shorthand Classes - Stenography TrainingBharggav Shorthand ClassesNo ratings yet

- Total: Estimation For Expansion & Repairs of Watchman RoomDocument2 pagesTotal: Estimation For Expansion & Repairs of Watchman RoomBharggav Shorthand ClassesNo ratings yet

- Document No:1 (Memorandum of Association)Document7 pagesDocument No:1 (Memorandum of Association)Bharggav Shorthand ClassesNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Line Fs PN Sap PN Description Priority Need Qty: PSU+SV 10003637 SF10000040881 Inductor Assy Coupled 5 / 2-6 286 #1Document6 pagesLine Fs PN Sap PN Description Priority Need Qty: PSU+SV 10003637 SF10000040881 Inductor Assy Coupled 5 / 2-6 286 #1huynh thi y viNo ratings yet

- Lesson 6 PID Control of Heat Exchanger Temp PDFDocument2 pagesLesson 6 PID Control of Heat Exchanger Temp PDFJenny GoNo ratings yet

- Lecture 6Document7 pagesLecture 6Milind BhatiaNo ratings yet

- Application of PiezoelectricityDocument30 pagesApplication of PiezoelectricityMohammad Mostofa Kamal KowshikNo ratings yet

- CMOS Inverter LayoutDocument2 pagesCMOS Inverter LayoutRen ValerosoNo ratings yet

- SystemResponse ResonanceDocument23 pagesSystemResponse ResonanceEyad A. FeilatNo ratings yet

- Philips Fwm998Document29 pagesPhilips Fwm998boroda2410No ratings yet

- VITRA Ophthalmic Photodisruptor Service ManualDocument71 pagesVITRA Ophthalmic Photodisruptor Service ManualMatteo MassiNo ratings yet

- Ablerex MSII and MSII RT User ManualDocument24 pagesAblerex MSII and MSII RT User ManualRosiinNo ratings yet

- GEA Cassette-Geko DF KSDocument64 pagesGEA Cassette-Geko DF KSCatalin FrincuNo ratings yet

- CompalDocument71 pagesCompalPaulo RochaNo ratings yet

- Syllabus Applied Electronics PDFDocument34 pagesSyllabus Applied Electronics PDFSelvam PdsNo ratings yet

- PR ChargedEV Wire Bonding 2016 SDocument5 pagesPR ChargedEV Wire Bonding 2016 STHEJA G CNo ratings yet

- BHELDocument39 pagesBHELKirtesh HiraouNo ratings yet

- Motoman Mh5L: General Purpose and Handling With The MH-seriesDocument2 pagesMotoman Mh5L: General Purpose and Handling With The MH-seriesFrancisco HermidaNo ratings yet

- SDI ASI Encoder MultiplexerDocument41 pagesSDI ASI Encoder MultiplexerChristie MillerNo ratings yet

- Institute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringDocument23 pagesInstitute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringMano HarNo ratings yet

- Pulsar2 User Manual - ENDocument83 pagesPulsar2 User Manual - ENJanette SouzaNo ratings yet

- Ntu Eee LetterheadDocument2 pagesNtu Eee LetterheadFresh Prince Of NigeriaNo ratings yet

- Safety Contactors: Product SelectionDocument4 pagesSafety Contactors: Product SelectionAlan OgataNo ratings yet

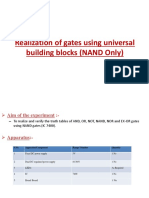

- Realization of Gates Using Universal Building Blocks (NAND Only)Document8 pagesRealization of Gates Using Universal Building Blocks (NAND Only)kishorebabNo ratings yet

- GSM Vs Cdma PresentationDocument39 pagesGSM Vs Cdma Presentationaaki_2005No ratings yet

- EABH (X) - D6V (9W), EAVH (X) - D6V (9W) - 4PEN556072-1A - 2019 - 12 - Field Settings Table - EnglishDocument10 pagesEABH (X) - D6V (9W), EAVH (X) - D6V (9W) - 4PEN556072-1A - 2019 - 12 - Field Settings Table - EnglishClaudia GradNo ratings yet

- Sekolah Menengah Kebangsaan Laki-Laki Methodist Kuala LumpurDocument4 pagesSekolah Menengah Kebangsaan Laki-Laki Methodist Kuala LumpurkriizNo ratings yet

- InverterDocument52 pagesInverterD'ivy M Chico100% (3)

- 1 Product Category SpecialDocument16 pages1 Product Category SpecialOmar SaeedNo ratings yet

- Downloadable Version - Electronic H&S IdenitfierDocument13 pagesDownloadable Version - Electronic H&S IdenitfierasadiqbalansariNo ratings yet

- 6578 ProtectionSystem MT 20121022Document12 pages6578 ProtectionSystem MT 20121022thyago_hcNo ratings yet

- Chapter 5: Control Unit: Micro OperationsDocument20 pagesChapter 5: Control Unit: Micro OperationsLui PascherNo ratings yet