Professional Documents

Culture Documents

Microprocessor Basic Programming

Uploaded by

ersimohitOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microprocessor Basic Programming

Uploaded by

ersimohitCopyright:

Available Formats

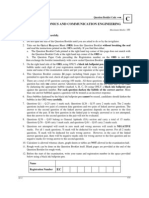

Unit I

1. Evolution of Microprocessors

2. History of computers

3. Timing and control

4. Semiconductor memory organization, Category of memory

5. 8-bit Microprocessor (8085),

6. Architecture

7. Instruction set

8. Addressing modes

9. Assembly Language Programming

Unit II

1. 8086 Architecture

2. Physical address

3. Segmentation

4. Memory organization

5. Bus cycle

6. Addressing modes

7. Difference between 8086 and 8088

8. Introduction to 80186 and 80286

9. Assembly Language Programming of 8086/8088

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Unit III

1. Introduction & Types of transmission 8257 (DMA)

2. 8255 (PPI)

3. Serial Data transfer (USART 8251)

4. Keyboard-display controller (8279)

5. Programmable Priority Controller (8259)

Unit IV

1. Programmable Interval Timer/ Counter (8253/8254)

2. Introduction, modes & Interfacing of 8253

3. Introduction to ADC and DAC

4. DAC methods

5. ADC converters

6. Types of ADC, ADC IC (0808/0809)

7. DAC and ADC Interfacing and Applications.

Unit V

1. Introduction to 32-bit and 64-bit microprocessors

2. PowerPC

3. Microcontroller (8051), Introduction, Architecture, Instruction set

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Reference Books:

S. Gaunkar: Microprocessor Architecture, Programming and

Applications with 8085/8080, Penram Publication

B.Ram: Microprocessor Architecture, Programming and

Applications, PHI Publication

R. Singh and B. P. Singh : Microprocessor Interfacing and

Application, New Age Publishers, 2nd Edition.

B.P. Singh and R. Singh : Advanced Microprocessor and

Microcontrollers, New Age Publishers, 2nd Edition.

D.V Hall : Microprocessors Interfacing, TMH (2nd Edition).

Y.C. Liu and G.A. Gibson : Microcomputer Systems: The

8086/8088 Architecture Programming, PHI 2nd Edition,

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Harvard & Von Neumann (Princeton)

Architecture

HARVARD & PRINCETON ARE THE UNIVERSITIES OF UNITED STATE.

VON NEUMANN IS THE SCIENTIST NAME IN PRINCETON UNIVERSITY.

Harvard Architecture: -

Program & data memory are separate.

Can fetch the next instruction when current

Instruction is in execution.

Von Neumann (Princeton) Architecture: -

Memory interface unit is responsible for access

of memory space between reading & passing

data between register.

Memory interface unit is the bottle neck unit.

Adv: -

1. Simplify to design the processor.

2. Content of memory can be used for variable

Storage &programstorage.

Praveen Kr. Malik, Sr. Lecturer

RGEC, Meerut Ph. 9719437711

RISC & CISC Architecture

RISC: REDUCED INSTRUCTION SET COMPUTERS.

In RISC instruction are bare as minimum possible to allow the user to

design its own application. (We can say that 8085 is RISC processor)

Ex: - MOV B,A

LDA 2000 H

MUL B (First transfer the data from B to A, then

Multiply)

CISC: COMPLEX INSTRUCTION SET COMPUTERS.

In CISC processor there tends to be large number of instructions, each

carrying out a different permutation of the same operations. (We can

say that 8085 is CISC processor)

Ex: - MUL AX, BX (Direct Multiplication can take place)

In general it is observed that RISC are faster then CISC. But, there are

some CISC processor which are faster then RISC. i.e. we cannot say always

that this one is faster.

Praveen Kr. Malik, Sr. Lecturer

RGEC, Meerut Ph. 9719437711

Real Time Operating System (RTOS): -

RTOS is a background program that control the execution of a number of

application and facilitates communication between the subtasks/task.

*. If more then one task is running at one time the operating system is known as

multitasking operating system. Each task is given small time slice of the

processor.

*. In simple PC operating system, console I/O, command interpreter and file

system processes are loaded with the kernel & everything is optimized to run in

PC environment.

*. In RTOS, the actual application task are loaded in with the kernel with priority

given to the task that are critical to the desired application.

Praveen Kr. Malik, Sr. Lecturer

RGEC, Meerut Ph. 9719437711

Introduction to Microprocessor

The CPU is a unit that fetches and processes a set of general-purpose instructions.

The CPU instruction set includes instructions for data transfer, ALU operations, stack

operations, input and output operations and program control, sequencing and

supervising operations

A microprocessor is a single VLSI chip that has a CPU and may also have other units

(e.g. caches, floating point processing arithmetic unit, pipelining and super-scaling

units) that are additionally present and result in faster processing of instructions.

A system designer need not be concerned about the design of the microprocessor,

only needs to understand the architecture related to the programming of the processor's

memory to carry out the required functionality i.e. implement the software

Examples: Intel 8085, Intel x86 processors, Motorola 68HCxxx, Sun Sparc, IBM

PowerPC etc.

Time-to-market and NRE costs are lower when systems are designed with

microprocessors

as the designer must only write a program. Flexibility is also high.

Unit cost may be low in small quantities compared with designing a dedicated chip.

Performance varies by application, unit cost may be high for larger volumes, size and

power might be higher due to unnecessary processor hardware

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Introduction to Microcontroller

A microcontroller is a single chip unit which, though having limited computational

capabilities, possesses enhanced input-output capabilities and a number of on-chip

functional units. Particularly suited for use in embedded systems for real-time control

applications. with on-chip program memory and devices. Common peripherals include

serial communication devices, timers, counters, pulse width

modulators, analog-to-digital and digital-to-analog converters. Enables single-chip system

implementation and hence smaller and lower-cost products. Examples: Motorola

68HC11xx, HC12xx, HC16xx, Intel 8051, 80251, PIC 16F84, PIC18, ARM9, ARM7, Atmel

AVR etc.

8085: (1977)

8-bit microprocessor - upgraded version of the 8080, 64KB main memory, 1.3

microseconds clock cycle time; 769,230, instructions/sec, 246 instructions, Intel sold 100

million copies of this 8-bit microprocessor.

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

80x86 Evolution

In this course we focus on the Intel x86 architecture, associated peripherals and assembly

language programming. However, concepts covered apply to other logic families.

4004:

4-bit microprocessor. 4KB main memory.

45 instructions. PMOS technology. 50 KIPS

8008: (1971)

8-bit version of 4004. 16KB main memory.

48 instructions. NMOS technology.

8080: (1973)

8-bit microprocessor. 64KB main memory.

2 microseconds clock cycle time; 500,000 instructions/sec. 10X faster than 8008.

8086: (1978) 8088 (1979)

16-bit microprocessor, 1MB main memory, 2.5 MIPS (400 ns).

4- or 6-byte instruction cache, Other improvements included more registers and additional

instructions.

80286: (1983)

16-bit microprocessor very similar in instruction set to the 8086.

16MB main memory, 4.0 MIPS (250 ns/8MHz).

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

80386: (1986)

32-bit microprocessor. 4GB main memory. 12-33MHz.

Memory management unit added.

Variations: DX, EX, SL, SLC (cache) and SX.

80386SX: 16MB through a 16-bit data bus and 24 bit address bus.

80486: (1989)

32-bit microprocessor, 32-bit data bus and 32-bit address bus.

4GB main memory. 20-50MHz. Later at 66 and 100MHz

Incorporated an 80386-like microprocessor, 80387-like floating point

coprocessor and an 8K byte cache on one package.

About half of the instructions executed in 1 clock instead of 2 on the

386.

Variations: SX, DX2, DX4.

DX2: Double clocked version:

66MHz clock cycle time with memory transfers at 33MHz.

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Accumulator Flags

B C

D E

H L

Program Counter

Stack Pointer

Data Address 8 16

GENERAL DESCRIPTION OF 8085 MICROPROCESSOR

The Intel 8085 microprocessor is an 8-bit device.

16 address bits provide access to 65,536 bytes of 8 bits data.

8 bi-directional data lines provide access to a data bus.

Control is provided by a variety of lines which support memory and I/O interfacing,

Requiring only a 5 volt supply.

The 8085 comes in two models, the 8085A and the 8085A-2. The 8085A expects clock

frequency of 3 MHz, while the 8085A-2 expects clock frequency of 5 MHz. This clock is

generated by a crystal externally.

The 8085 make use of multiplexing of the lower 8 bits of the address with the data bits on

the same 8 pins. This requires that the external circuitry be able to catch and hold the A0-

A7 lines for later use.

The upper 8 bits of the address have their own pins, however.

The General Purpose Register Array contains the B, C, D, E, H, and L registers, each 8 bits

wide. The B and C, D and E, and H and L registers may be grouped into 16-bit register

pairs. The H & L register pair may be used to store indirect addresses.

An address generation system consisting of the Program Counter, Stack Pointer, address

latches, and incremented / decremented.

The array also contains the Program Counter (PC) and Stack Pointer (SP). These 16-bit

registers contain the address of the next instruction part to be fetched, and the address of

the top of the stack, respectively.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

A mathematical and logical subsystem composed of the Arithmetic Logic Unit (ALU) and

associated registers, which handle the math and logic functions of the machine.

An Instruction Register and decoder system which interpret the programmers

instructions

A timing and control package which provides the bodily functions of power and clock

circuits, and handles the wait, interrupt, and hold functions of the system

An 8-bit internal data bus, which provides the data path between functional elements, and

to the outside world via the Address/Data Buffer.

Two serial data lines, Serial Input Data and Serial Output Data, which feed the internal

data bus directly

ADDRESS LINES A8 - A15: These tristate lines are outbound only. They provide the

upper 8 bits of the 16-bit-wide address which identifies one unique 8-bit byte within the

MPs address space, or the 8-bit address of an I/O device. Sixteen address lines provide

an address space of 65,536 locations.

ADDRESS-DATA LINES AD0 - AD7: These tristate lines may by either inbound or

outbound. They provide a multiplexing between the lower 8 bits of the 16-bit-wide

address early in a machine cycle and 8 data bits later in the cycle. When containing

addresses.

ADDRESS LATCH ENABLE (ALE): This signal appears outbound early in a machine

cycle to advise the external circuitry that the AD0 - AD7 lines contain the lower 8 bits of a

memory address

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

STATUS LINES so, S1, & I-O/M: These three status lines serve to indicate the

general status of the processor with respect to what function the MP will perform

during the machine cycle

READ & WRITE (/RD & /WR): These lines indicate which direction the MP expects to

pass data between itself and the external data bus.

READY: This is an input line which may be used as a signal from external RAM that a

wait state is needed.

HOLD & HOLD ACKNOWLEDGE (HOLD & HLDA): These lines provide the 8085 with

a DMA capability by allowing another processor on the same system buses to request

control of the buses.

INTERRUPT & INTERRUPT ACKNOWLEDGE (INTR & INTA): These lines provide a

vectored interrupt capability to the 8085. Upon receipt of INTR, the 85 will complete

the instruction in process, then generate INTA as it enters the next machine cycle.

RST 5.5, 6.5, 7.5: These three lines are additional interrupt lines which generate an

automatic Restart.

RESET IN & RESET OUT: These lines provide for both MP and systemreset.

X1 & X2: These two pins provide connection for an external frequency determining

circuit to feed the 8085s clock. This is normally a crystal.

CLOCK (CLK): This line provides a system clock signal to external circuits which need

to be in synchronization with the MP.

Vcc & Vss: These are the power connections for +5 volts and ground, respectively.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

STATUS FLAG REGISTER

The Status Flags of the 8085 indicate the logical conditions that existed as a

result of the execution of the instruction just completed.

S Z x A C x P x C

ZERO FLAG: This flag is set to a 1 by the instruction just ending if the A Register

contains a result of all 0s.Otherwise 0.

SIGN FLAG: This flag is set to a 1 by the instruction just ending if the leftmost,

bit of the A Register is set to a 1. Otherwise 0.

PARITY FLAG: This flag is set to a 1 by the instruction if the A Register is left

with an even number of bits set on, i.e., in even parity. Otherwise 0.

CARRY FLAG: This flag is set to a 1 by the instruction just ending if a carry out

of the leftmost bit occurred during the execution of the instruction. Otherwise 0.

AUXILIARY CARRY FLAG: This flag is set to a 1 by the instruction just ending if

a carry occurred from bit 3 to bit 4 of the A Register. Otherwise 0.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Instruction of 8085: -

DATA TRANSFER: -

1. MOV r1, r2 Move contents of register (A, B, C, D, E, H, L) r2 to r1.

Eg. MOV A, BMove the contents of B to A

2. MVI r, data Move the data to the specify register

Eg. MVI C, F0H Move the data F0 to the reg C

3. LDA 2000H Load the contents of memory location 2000 to Accu. A

4. LXIH 2000H Load the 20 to H Load the 00 to L

5. MOV A, M Load the value of data from memlocation 2000 to A.

6. MOV M, A Load the value of A to the memory pointed by HL pair.

7. MVI M, F0H Load F0 to the memory pointed by HL pair.

8. STA 2000H Store the data of Accu. A to the memory 2000H

9. LHLD 2000H Data of 2000 to L, Data of 2001 to H

10. SHLD 2000H Store the value of L to 2000 & H to 2001

11. LDAX D If DE=2000H, then load the value of 2000 to Accu. A

12. STAX D if DE=3000H, Store the value of A to the 3000H

13. XCHG Exchange the value of DE with HL pair.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

ARITHMETIC: -

1. ADD C A+C=A

2. ADD M A+[H-L]=A

3. ADI F0H A+F0=A

4. ADC C A+C+[CF]=A

5. ADC M A+[H-L]+[CF]=A

6. ACI F0H A+F0+[CF]=A

7. DAD D H-L+D-E=H-L

8. SUB B A-B=A

9. SUB M A-[H-L]=A

10. SUI F0H A-F0=A

11. SBB B A-B-[CF]=A

12. SBB M A-[H-L]-[CF]=A

13. SBI F0H A-[F0]-[CF]=A

14. INR D Increment the content of D by one

15 INX D Increment the content of DE pair by one

16. DCR L Decrement the content of L by one.

17. DCR H Decrement the content of HL pair by one.

1. DAA It is used just after the addition instruction. And it

Convert the result in decimal system.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

LOGICAL GROUP: -

1. ANA D Logical AND Between the contents of A and D

2. AND M Logical AND Between the contents of A and [H-L]

3. ANI F0 H Logical AND Between the contents of A and F0 H

4. ORA C Logical OR Between the contents of A and C

5. ORA M Logical OR Between the contents of A and [H-L]

6. ORI F0 H Logical OR Between the contents of A and F0 H

7. XRA C Logical XOR Between the contents of A and C

8. XRA M Logical XOR Between the contents of A and [H-L]

9. XRI 0F H Logical XOR Between the contents of A and 0F H

10. CMA Complement the contents of A only.

11. CMC Complement the carry status.

12. STC Set the carry flag.

13. CMP D Compare the contents of A and D. i.e. A-D. But the contents of A and D

are not changed.

14. CMP M Compare the contents of A and [H-L]. i.e. A-[HL]. But the contents of A

and [HL] are not changed.

15. CPI F0 H Compare the contents of A and F0. i.e. A-F0. But the contents of A and

F0 are not changed.

16. RLC Rotate Accu. Left.

17. RRC Rotate Accu. Right

18. RAL Rotate Accu. Left through carry.

RAR Rotate Accu. right through carry.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

BRANCH GROUP: -

Unconditional

1. J MP 2000 J ump to the location 2000

2. CALL 2000 J ump to the location 2000

Conditional

1. J Z 2000 J ump to the location 2000 if there is zero in result i.e. in Accu.

2. J NZ 2000 J ump to the location 2000 if there is non zero in result i.e. in Accu.

3. J C 2000 J ump to the location 2000 if there is carry in result i.e. in Accu.

4. J NC 2000 J ump to the location 2000 if there is no carry in result i.e. in Accu.

5. J P 2000 J ump to the location 2000 if result is positive in Accu.

6. J M 2000 J ump to the location 2000 if result is negative in Accu.

7. J PE 2000 J ump to the location 2000 if result contain even parity in Accu.

8. J PO 2000 J ump to the location 2000 if result contain odd parity in Accu.

9. RET Return from the subroutine.

10. PUSH C Push the contents of C reg. into stack.

11. POP D Retrieve the contents of stack top into reg C.

12. HLT End of the program.

13. NOP No operation.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

OPCODE FORMAT

Registered code Register pair code

B 000 BC 00

C 001 DE 01

D 010 HL 10

E 011

H 100

L 101

M 110

A 111

ADDRESSING MODES

THE VARIOUS WAY OF SPECIFYING THE DATA TO BE OPERATED ON ARE CALLED AS ADDRESSING

MODES. 8085 PROVIDE THE FOLLOWING ADDRESSING MODES.

IMMEDIATE ADDRESSING MODE:-

THE DATA TO BE USED IS GIVEN IN THE INSTRUCTION ITSELF. IMMEDIATE ADDRESSING

MODEINSTRUCTION ARE EITHER 2 BYTE OR 3 BYTE LONG.

EX. MVI A, 20H ADI 30H LXI H, C200H

REGISTER ADDRESSING MODE

THIS MODE OF ADDRESSING SPECIFY THE REGISTER OR REGISTER PAIR THAT CONTAIN THE DATA.

EX. MOV A, B ADD B

DIRECT ADDRESSING MODE

IN THIS MODE THE OPERAND IS GIVEN BY A DIRECT ADDRESS WHERE THE DATA IS PRESENT. THE

DIRECT ADDRESSING MODE INSTRUCTION IS A 3 BYTE INST.

EX. LDA 2000H STA 2000H

INDIRECT ADDRESSING MODE

HERE INST. DOES NOT HAVE ADDRESS OF THE DATA. BUT THE INSTRUCTION POINT WHERE THE

ADDRESS IS STORED

EX. MOV A, M MOV M, A

IMPLIED OR INHERENT ADDRESSING MODE

THIS MODE DOES NOT REQUIRED ANY OPERAND. THE DATA IS SPECIFIED WITHIN THE OPCODE

ITSELF.

EX. RAL RAR

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

INSTRUCTION TYPE

The first part of the instruction is called opcode and the second part is called operand. The operand may be either

8 bit data or memory location. Depending upon the number of bytes required to specify an operation the

instruction are of 3 bytes.

ONE BYTE INSTRUCTION:-

A 1 byte instruction include the opcode and the operand in the 8 bits only i.e. One byte

MOV A, B 01 111 000 =78H

MOV A, C 01 111 001 =79H

ADD B 1000 0 000 =80H

TWO BYTE INSTRUCTION:-

The 2 byte instruction uses first byte to specify the operation and second byte to specify the operand.

MVI A, 20 0011 1110 0010 0000

MVI B, 30 0000 0110 0011 0000

THREE BYTE INSTRUCTION:-

The 3 byte instruction uses first byte to specify the operation, second and third bytes are used to specify the

operand. Generally those instruction are used to specify memory address.

LDA ADDRESS

LDA 2000H 0011 1010 0010 0000 0000 0000

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

INSTRUCTION SET

They are classified in to following group.

DATA TRANSFER OPERATION

This group of instruction copies data from source to destination

MOV A, B MOV A, M MVI R, DATA LDA 2000H LXI H 2000H

LHLD 2000H LDAX 2000

ARITHEMATIC OPERATION

This group of instruction perform arithematic operation like addition subtraction

. ADD R ADD M ADC D ADC M ADI F0

DAD R INR R INX H DCR R DCX H

LOGICAL OPERATION

This group of instruction perform logical operation such as and, or, not etc

ANA R ANA M ANI DATA ORA R

XRA R CMA CMP R RAL

BRANCH OPERATION

This group of instruction change the path of program execution or sequence.

a) CONDITIONAL b) UNCONDITIONAL

J C ADD. J NC ADD. CALL ADDRESS

J Z ADD. J NZ ADD J MP ADDRESS

STACK AND MACHINE OPERATION

This group of instruction perform stack and machine control function.

PUSH R POP R NOP HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

IO DATA TRANSFER TECHNIQUE

THE I/O MODULE IS USED TO TRANSFER DATA BETWEEN MICROPROCESSOR AND

EXTERNAL DEVICE. ALL DEVICES SHOULD BE COMPATIABLE IN SPEED TO THAT OF

MICROPROCESSOR. BUT ALL DEVICE ARE NOT SPEED COMPATIABLE. TO SOLVE THE

PROBLEM OF SPEED MISMATCH THE FOLLOWING DATA TRANSFER TECHNIQUE ARE TO

BE USED.

MICROPROCESSOR CONTROLED:-

HERE DATA IS TRANSFERRED BY MICROPROCESSOR, TO TRANSFER ONE BYTE OF DATA

BETWEEN MEMORY AND IO, IT IS REQUIERD TO EXECUTE SEVERAL INST. THIS TYPE OF

TRANSFER WILL BE USED WHEN THE SPEED OF IO IS LESS THAN OR EQUAL TO THA M.P.

PROGRAMMED I/O:-

HERE I/O TRANSFER IS DONE COMPLETELY UNDER THE CONTROL OF THE PROGRAM.

THE M.P EXECUTE I/O OR MEMORY BASED INST. TO ACCESS THE I/O DEVICE.

INTERRUPT I/O

THE PROGRAMMED I/O TECH. WASTE THE MAX. TIME OF M.P. TO OVER COME THE DRAW

BACK, IN INTERRUPT I/O M.P DOES NOT CHECK STATUS OF I/O DEVICE BUT THE I/O

DEVICE SENDS REQUEST TO THE M.P WHENEVER IT IS READY TO ACCEPT DATA OR TO

TRANSFER DATA.

DMA CONTROLLED

THIS TRANSFER WILL BE USED WHEN SPEED OF I/O IS MORE THAN THE SPEED OF M.P.

HERE DATA IS TRANSFERRED BETWEEN MEMORY AND I/O DIRECTLY. THIS TYPE OF

TECH. IS USED WHEN THE LARGE AMOUNT OF DATA IS PRESENT.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

I/O mapped I/O: -

In this data transfer technique 8085 uses IO/M signal to distinguish

between I/O and memory operation. IN instruction is used to read the data

from specified port address to the accumulator only. OUT instruction is

used to transfer the data from accumulator to specified port address only.

When 8085 execute any IN or OUT instruction it place device address (Port

number) on the de multiplexed low order address bus as well as the high

order address bus. The address or port number can be any of the 256 i.e. from 00 to FF.

In this method I/O address is 8 bit (IN F0 H). IOW & IOR signals are used to control read

& write operation. Instructions are only IN & OUT. Data transfer is between any

accumulator and I/O device. Maximum numbers of I/O devices are 256.

Memory mapped I/O: -

In this data transfer technique 8085 assigned any identified 16-bit address.

The memory related instruction transfer the data between I/O devices. In

this method every instruction that refer to a memory location can control

I/O also. In this method device address is 16 bit. Thus A0 to A 15 lines are

used to generate device address. MEMR & MEMW control the read &

write operation. Instruction LDA, STA, LDAX Rp, STAX Rp, MOV r, M, MOV M, r. are the

Data transfer is between any register and I/O device. Maximum numbers of I/O devices are

65,536.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

To find the addition

of two eight bit

numbers sum is 8

bits.

LXIH 2501 H

MOV A,M

INX H

ADD M

STA 2503 H

HLT

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

ADDITION OF TWO 8-BIT NUMBER,

SUM 16 BITS

LXI H,2501H

MVI C,00

MOV A,M

INX H

ADD M

J NC HEAD

INR C

HEAD STA 2503H

MOV A,C

STA 2504H

HLT

To find the subtraction

of two eight bit

numbers

LXIH 2501 H

MOV A,M

INX H

SUB M

INX H

MOV M,A

HLT

DECIMAL ADDITION OF TWO 8-

BIT NUMBER ; SUM 16-BITS

LXI H,2501H

MVI C,00

MOV A,M

INX H

ADD M

DAA

J NC AHEAD

INR C

AHEAD STA 2503H

MOV A,C

STA 2504H

HLT

Decimal substraction of two 8-bit

number

LXI H,2501H

MVI C,00

MOV A,M

INX H

SUB M

DAA

J NC AHEAD

INR C

AHEAD STA 2503H

MOV A,C

STA 2504H

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

To shift an 8-bit number to

left by two bits

LXIH 2501 H

MOV B,M

MOV A,M

ADD B

ADD B

STA 2502 H

HLT

To shift an 16 bit number left

by two bit

LHLD 2501

DAD H

DAD H

SHLD 2503

HLT

ADDITION OF 2 16 BIT

NUMBER. SUM IS 16 BIT OR

MORE.

LHLD 2501 H

XCHG

LHLD 2503 H

MVI C, 00 H

DAD D

J NC HEAD

INR C

HEAD SHLD 2505 H

MOV A, C

STA 2507

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

To mask off 4 LSB's of

8 bit number

LDA 2501 H

ANI F0 H

STA 2502 H

HLT

To mask off 4 MSB's of

8 bit number

LDA 2501 H

ANI 0F H

STA 2502 H

HLT

To mask ON 4 LSB's

of 8 bit number

LDA 2501 H

ORI 0F H

STA 2502 H

HLT

To mask ON 4 MSB's

of 8 bit number

LDA 2501 H

ORI F0 H

STA 2502 H

HLT

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

To find square from look up table

2600 00 LDA 2500 H

2601 01 MOV L, A

2602 04 MVI H, 26

2603 09 MOV A, M

2604 16 STA 2501 H

2605 25 HLT

2606 36

2607 49

2608 64

2609 81

To find the largest of two numbers

LXIH 2500

MOV A, M

INX H

CMP M

J NC HEAD

MOV A, M

HEAD STA 2502

HLT

To find the smallest of two numbers

LXIH 2500

MOV A, M

INX H

CMP M

J C HEAD

MOV A, M

HEAD STA 2502

HLT

WAP in 8085 to add 16 bit data

1234H & 4321H.

MVI B, 12 H

MVI C, 34 H

MVI D, 43 H

MVI E, 21 H

MOV A, E

ADD C

MOV L, A

MOV A, D

ADC B

MOV H, A

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

To find the largest number in data array

LXIH 2500 H

MOV C,M

INX H

MOV A,M

DCR C

BACK INX H

CMP M

J NC LOOP

MOV A,M

LOOP DCR C

J NZ BACK

STA 2450 H

HLT

To find the smallest number in data array

LXIH 2500 H

MOV C,M

INX H

MOV A,M

DCR C

BACK INX H

CMP M

J C LOOP

MOV A,M

LOOP DCR C

J NZ BACK

STA 2450 H

HLT

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

To find the smallest number in data array from 2501 to 2509.

Total no. are 8. and the count is stored in 2500.

LXIH 2500 H

MOV C,M

INX H

MOV A,M

DCR C

BACK INX H

CMP M

J C LOOP

MOV A,M

LOOP DCR C

J NZ BACK

STA 2450 H

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Sum of series of 8 bits numbers, sum is 16 bits

LXI H 2500 H

MOV C, M

MVI A, 00 H

MOV B, A

Loop INX H

ADD M

JNC Head

INR B

Head DCR C

JNZ Loop

STA 2450 H

MOV A, B

STA 2451 H

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

To arrange the array in descending order. Data is stored from 2500 onwards.

Count is in the location 2500. Store the result on 2601 location.

LXI D, 2601 H To store result

LXI H, 2500 H Count address

MOV B, M

Start CALL 2200 H

To find largest number STAX D

2200 LXIH 2500 CALL 2050 H

MOV C, M INX D

MVI A, 00 H DCR B

LOOP INX H JNZ Start To replace A with 00 H

CMP M HLT 2050 LXI 2500 H

JNC HEAD MOV C, M

MOV A, M Back INX H

HEAD DCR C CMP M

JNZ Loop JZ Go

RET DCR C

JNZ Back

Go MVI A, 00 H

MOV M, A

RET

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

TO ARRANGE THE ARRAY IN ASCENDING ORDER

LXI D, 2601 H To store result

LXI H, 2500 H Count address

MOV B, M

Start CALL 2200 H

To find smallest number STAX D

2000 LXIH 2500 CALL 2050 H

MOV C, M INX D

MVI A, FF H DCR B

Loop INX H JNZ Start To replace A with FF H

CMP M HLT 2050 LXI 2500 H

JC HEAD MOV C, M

MOV A, M Back INX H

HEAD DCR C CMP M

JNZ Loop JZ Go

RET DCR C

JNZ Back

Go MVI A, FF H

MOV M, A

RET Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Register B=75 H is interpreted as packed BCD. Unpack the BCD digit

and save them in D & E REGISTER.

PACKED BCD = XY UNPACKED BCD1 = 0X, BCD2 = 0Y

MVI B, 75 H

MOV A, B

ANI F0 H

RRC

RRC

RRC

RRC

MOV D, A

MOV A, B

ANI 0F

MOV E, A

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

MULTI BYTE ADDITION MULTI BYTE SUBTRACTION

3A9C8A67 3A9C8A67

+9B476C8B -9B476C8B

LXI H 2500 H LXI H 2500 H

MOV C, M MOV C, M

INX H INX H

LXI D 2601 H LXI D 2601 H

ORA A // To set carry flag to 0 ORA A // To set carry flag to 0

Loop LDAX D Loop LDAX D

ADC M SBB M

MOV M, A MOV M, A

INX H INX H

INX D INX D

DCR C DCR C

J NZ Loop J NZ Loop

HLT HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Multi byte decimal addition Multi byte decimal subtraction

3A9C8A67 3A9C8A67

+9B476C8B -9B476C8B

LXI H 2500 H LXI H 2500 H

MOV C, M MOV C, M

INX H INX H

LXI D 2601 H LXI D 2601 H

ORA A ORA A

Loop LDAX D Loop LDAX D

ADC M SBB M

DAA DAA

MOV M, A MOV M, A

INX H INX H

INX D INX D

DCR C DCR C

J NZ Loop J NZ Loop

HLT HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

MOVE A BLOCK OF DATA FROM ONE SECTION OF MEMORY

TO ANOTHER SECTION OF MEMORY.

Alternate Method

LXI H 2000 H LXI 2000 H

MOV C, M LDAX D

INX H MOV C, A

LXI D 2201 INX D

Loop MOV A, M LXI H 2201H

XCHG Loop LDAX D

MOV M ,A MOV M ,A

XCHG INX H

INX H INX D

INX D DCR C

DCR C J NZ Loop

J NZ Loop HLT

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

ONE'S COMPLEMENT OF TWO'S COMPLEMENT OF

A 16 BIT NUMBER A 16 BIT NUMBER

LXI H 2501 H LXI H 2501 H

MOV A, M MVI B, 00 H

CMA MOV A, M

STA 2503 H CMA

INX H ADI 01

MOV A , M STA 2503 H

CMA J NC GO

STA 2504 INR B

HLT GO INX H

MOV A, M

CMA

ADD B

STA 2504 H

HLT

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Looping for large data

MVI D, FF H

LOOP MVI C, FF H

BACK DCR C

J NZ BACK

DCR D

J NZ LOOP

HLT

Find the negative numbers in a block of data.

LDA 2200 H

MOV C, A Count in C

MVI B, 00 H

LXI H, 2201 H First data

BACK MOV A, M

ANI 80 H Check MSB is 1

J Z LOOP

INR B

LOOP INX H

DCR C

J NZ BACK

MOV A,B

STA 2300 H

HLT

FIND THE POSITIVE NUMBERS IN A BLOCK

OF DATA.

LDA 2200 H

MOV C, A Count in C

MVI B, 00 H

LXI H, 2201 H First data

BACK MOV A, M

ANI 80 H Check MSB is 1

J NZ LOOP

INR B

LOOP INX H

DCR C

J NZ BACK

MOV A,B

STA 2300 H

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

TO COUNT NUMBERS OF 1S IN A DATA

MVI D, 0A H Given data

MVI B, 00 H

MVI C, 08 H Total bit count

BACK RAR

J NC LOOP

INR B

LOOP DCR C

J NZ BACK

HLT

TO COUNT NUMBERS OF 0S IN A DATA

MVI D, 0A H Given data

MVI B, 00 H

MVI C, 08 H Total bit count

BACK RAR

J NC LOOP

INR B

LOOP DCR C

J NZ BACK

SBI A, 08 H

HLT

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

CALCULATE THE SUM OF SERIES OF EVEN NUMBERS

LDA 2200 H

MOV C, A Count in C

MVI B, 00 H

LXI H, 2201 H First data

BACK MOV A, M

ANI 01 H

J NZ LOOP

MOV A, B Initially first making A = 00 H

ADD M

MOV B, A

LOOP INX H

DCR C

J NZ BACK

STA 2210 H

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Separate even numbers from a given numbers

LXI H, 2200 H // To retrieve data

LXI D, 2300 H // To store the data

MVI C, 32 H // From 50 numbers

BACK MOV A, M

ANI 01 H // Check LSB = 1

J NZ LOOP

MOV A, M

STAX D // Store A in DE Location

INX D

LOOP INX H

DCR C

J NZ BACK

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

MULTIPLICATION OF TWO NUMBERS: -

LHLD 2501 H // Get Multiplicand

XCHG // Multiplicand In HL

LDA 2503 H //Multiplier in Accu.

LXI H, 0000 H // Initial product = 00 H

MVI C, 08 H // Eight times

LOOP DAD H // Shift product by 1 bit

RAL // Rotate multiplier left by one bit. Is MSB = 1?

J NC HEAD

DAD D // Product =product+multiplicendHEAD

DCR C

J NZ LOOP

SHLD 2504 H

HLT

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

PIN DIAGRAM / BLOCK DIAGRAM 8086

8086 is a 16-bit microprocessor with a 16-bit data bus & 20 bit Address bus.

AD15-AD0 Multiplexed address(ALE=1)/data bus(ALE=0).

A19/S6-A16/S3 (multiplexed)

High order 4 bits of the 20-bit address OR status bits S6-S3.

M/IO Indicates if address is a Memory or IO address.

RD When 0, data bus is driven by memory or an I/O device.

WR If 0, Microprocessor is driving data bus to memory or an I/O device.

ALE (Address latch enable)

When 1, address data bus contains a memory or I/O address.

DT/R (Data Transmit/Receive) Data bus is transmitting/receiving

DEN (Data bus Enable) Activates external data bus buffers.

S5: Indicates condition of IF flag bits.

INTR When 1 and IF=1, microprocessor prepares to service interrupt. INTA

becomes active after current instruction completes.

INTA Interrupt Acknowledge generated by the microprocessor in response

to INTR. Causes the interrupt vector to be put onto the data bus.

NMI Non-maskable interrupt. Similar to INTR except IF flag bit is not consulted and

interrupt is vector

MN/ MX Select minimum (5V) or maximum mode (0V) of operation.

BHE Bus High Enable. Enables the most significant data bus bits (D 15 -D 8 )

during a read or write operation.

READY Used to insert wait states (controlled by memory and IO for reads/writes) into

the microprocessor.

RESET Microprocessor resets if this pin is held high for 4 clock periods.

TEST An input that is tested by the WAIT instruction.

HOLD Requests a direct memory access (DMA). When 1, microprocessor stops and

places address, data and control to the DMA.

HLDA Indicates that the microprocessor has entered the hold state.

R0/GT1 & R0/GT0 Request/grant pins request/grant direct memory accesses (DMA)

during maximum mode operation.

LOCK Lock output is used to lock peripherals off the system. Activated by using the

LOCK: prefix on any instruction.

QS1 and QS0 The queue status bits show status of internal instruction queue. Provided for

access by the numeric coprocessor (8087).

8086 INTERNAL ARCHITECTURE

Its internal register r 16 bit wide and its data bus, 16 bit wide and can perform arithmetic

operation on 16 bit numbers. It uses 16 bit instructions. The m.p can read or write a 16 bit data

from or to memory. It can also read or write 16 bit data from or to i/o device. The address bus is

20 bit wide i.e. It can access 1 Mb of memory location.it consist of two independent parts,

execution unit (EU) & bus interface unit (BIU).

The EU contain an instruction decoder, a 16 arithmetic and logic unit, a 16 bit flag register, 8

eight bit GPR, two pointer register and two index register.

The BIU have FIFO based register of size 6 bytes in length called queue. The BIU pre fetch the

instruction from memory and store them in queue. The EU get the next instruction from queue.

This tech. Is called pipelining.

It uses only 9 bits, in flag register, six of which are known as conditional and remaining three

are known as general flags.

OV OVERFLOW FLAG DF - DIRECTION FLAG

IF - INTERRUPT FLAG TF - TRAP FLAG

SF - SIGN FLAG ZF - ZERO FLAG

AF - AUX. CARRY FLAG

CF - CARRY FLAG PF - PARITY FLAG

|---------------- 8086 FLAGS REGISTER (16-BITS) ----------------|

-- -- -- -- OF DF IF TF SF ZF -- AF -- PF -- CF

8086 REGISTERS

GENERAL PURPOSE REGISTERS

AX - 16-BIT ACCUMULATOR, CONTAINS AH AND AL

BX - BASE G.P. REGISTER, CONTAINS BH AND BL SUBREGISTERS.

CX - 16-BIT COUNTER REGISTER, CONTAINS CH AND CL

DX - DATA REGISTERR, CONTAINS DH AND DL SUBREGISTERS.

POINTER REGISTERS

IP - THE INSTRUCTION POINTER REGISTER.

SP - THE STACK POINTER REGISTER.

BASE REGISTERS

BX - BASE G.P. REGISTER (ALSO A GENERAL PURPOSE REGISTER).

BP - BASE POINTER REGISTER.

INDEX REGISTERS

SI - SOURCE INDEX REGISTER.

DI - DESTINATION INDEX REGISTER.

SEGMENT REGISTERS

CS - CODE SEGMENT REGISTER.

SS - STACK SEGMENT REGISTER.

DS - DATA SEGMENT REGISTER - DEFAULT FOR DATA ACCESS.

ES - EXTRA SEGMENT REGISTER.

COMMON SEGMENT/OFFSET PAIRS

SS:SP - THE STACK POINTER.

CS:IP - THE PROGRAM COUNTER.

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Memory Segmentation of 8086: -

Q.1 FIND THE PHYSICAL ADDRES OF FIRST AND LAST LOCATION OF AS

SEGMENT. SEGMENT BASE IS 1000H.

PHYSICAL ADDRESS OF FIRST LOCATION IS 1000:0000H i.e.

1000H X 10H + 0000H = 10000H

PHYSICAL ADDRESS OF LAST LOCATION IS 1000:FFFFH i.e.

1000H X 10H + FFFFH = 1FFFFH

Q.2 FIND THE PHYSICAL ADDRES OF FIRST LOCATION OF SEGMENTS

BASE 1000H AND 1001H.

1000H X 10H + 0000H = 10000H

1001H X 10H + 0000H = 10010H

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Instruction of 8086: -

DATA TRANSFER: -

MOV AX, CX Move the contents of reg CX to AX.

MOV DH, CL Move the contents of reg DH to CL.

MOV DL, 08 H Move the data 08 H to DL reg.

MOV CX, 0AFF H Move the data 0AFF H to the reg CX.

MOV DX, [08 H] Move the data from the PA calculated from 0008

+ DS to reg DX. Eg. DS=2000. Then PA =20008. i.e.

20008 to DH and 20009 to DL.

MOV AX, [09FA H] Move the data from the PA calculated from 09FA

+ DS to reg AX.

MOV CX, [BX] if BX=2000. Then 2000 + [DS]=PA

MOV AX, [SI] if SI=2000. Then 2000 + [DS]=PA

MOV AX, [BX+0008H] i.e. EA/offset=0008+value of BX. Then added

with DS to obtain PA.

MOV CX, [SI+0A2H]

MOV DX, [BX+SI+0AH]

PUSH CX Decrement SP by 2, copy CX to stack.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

PUSH 2000 [BX] Decrement SP by 2, copy a word from Data segment

(PA =EA+ DS, EA=2000+[BX]) to stack.

POP CX Copy word from stack to CX, increment the SP by 2

POP 2000 [BX] Copy a word from stack to memory in DS.

(PA=EA+DS) EA=2000+[BX]

XCHG AL, CL Exchange byte with AL and CL

XCHG AX, BX Exchange bytes with AX and BX

XCHG AL, 2000[BX] Exchange byte with AL (PA=EA+DS,

EA=2000+[BX])

LEA CX, 2100 H Load CX with offset of 2100 H in DS

LEA AX, [BX][DI] Load AX with EA=[BX]+[DI] in DS

LDS CX, [391A H] Copy contents from offset 391A & 391B to CX & then

copy contents at offset 391C & 391D in DS

LES CX, [391A H] Copy data from offset 391A & 391B to CX & then copy

content at offset 391C & 391D in DS to ES register.

IN AL, 95 H Copy a byte from port 95 to AL.

IN AX, 95 H Copy a word from port 95 H to AX.

OUT F8 H, AL Copy contents of AL to 8 it port address F8 H

OUT F8 H, AX Copy contents of AX to 16 it port address F8 H

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

ARITHMETIC INSTRUCTION: -

ADD AL, F0 H Add the data of AL with F0 H data. AL+F0=AL

ADD AX, 2000[BX] Add the contents of AX with EA=2000+Contents of BX. PA

=EA+DS.

ADD DL, CL DL+CL=DL.

ADD AX, CX AX+CX=AX.

INC CL CL=CL+1 INC CX CX=CX+1

DEC DL DL=DL-1 DEC DXDX=DX-1

DAA Decimal adjustment after addition takes place.

ADC AL, CL ADC AX, CX ADC BX, 2000[BX]

SUB AL, F0 H AL=AL-F0 H

SUB AX, CX AX=AX-CX

SUB AX, 2000[BX] AX=AX-(PA(EA=2000+[BX]))

SBB AL, CL SBB AX, CX SBB BX, 2000[BX]

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

CMP AL, 01 Compare AL with data 01.

CMP AX, CX AX-CX, But contents of AX & CX are not changed.

Only status flag is set accordingly.

CMP CX, 2000 H PA=EA+(2000+[DS])

DAS Decimal adjustment after subtraction.

MUL BL AX = AL x BL (unsigned)

MUL BX AX x BX = high word in DX low word in AX (unsigned)

IMUL BL AX = AL x BL (signed)

IMUL BX AX x BX = high word in DX low word in AX (signed)

DIV CL AX/CL = Quotient in AL, reminder in AH

DIV CX (DX + AX)/CX Quotient in AX, reminder in DX

LOOP 2050 Decrement the contents of reg. CX by one & jump to

2050. If CX if not zero.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

LOGICAL INSTRUCTION: -

NEG AL NEG AX Takes 2s complement of given data in register.

NOT AL NOT CX Takes 1s complement of given data in register.

AND BL, CL AND CX, DX AND AX, [000F H]

OR CL, BL OR DX, CX OR CX, [FFF0 H]

ROL CX, 01H Rotate value of register left with specifies count.

MOV CL, 03 H

ROL BL, CL

ROR CX, 01H Rotate value of register right with specify count.

MOV CL, 03 H

ROR BL, CL

RCL CX, 01H Rotate value of register left with specifies count

with carry.

MOV CL, 03 H

RCL BL, CL

RCR CX, 01H Rotate value of register right with specify count

with carry.

MOV CL, 03 H

RCR BL, CL

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

8086 Program Example

NAME MAIN PROGRAM

DATA SEGMENT

DATA ENDS

CODE SEGMENT

ASSUME CS: 2000

ASSUME DS: 3000

MOV SI, 1100 H

MOV AX, [SI]

MOV BX, []

HLT

CODE ENDS

END

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

ADDITION OF TWO 16 BIT DATA. RESULT IS 16 BIT OR MORE.

NAME MAIN PROGRAM

DATA SEGMENT

ORG 1000 H

SUM DW 00H

CARRY DB 00H

DATA ENDS

CODE SEGMENT

ASSUME CS: 2000

ASSUME DS: 3000

ORG 1000 H

MOV AX, 20FF H

MOV BX, 40FF H

MOV CL, 00 H

ADD AX, BX

MOV SUM, AX

J NC LOOP

INC CL

LOOP MOV CARRY, CL

HLT

CODE ENDS

END

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

LARGEST 16 BIT NUMBER IN DATA ARRAY: -

DS=1000H, SI=0200H Count at 10200H =0A H

MOV AX, 0000 H // Initially Ax = 0000 H

MOV SI, 0200 H

MOV CX, [SI] // Count in reg Cx

BACK INC SI

INC SI // Point next data of 16 bit

CMP AX, [SI]

J NC GO

MOV AX, [SI]

GO LOOP BACK // Decrement Cx & J ump to back

MOV [0300], AX

HLT

SMALLEST 16 BIT NUMBER IN DATA ARRAY: -

DS=1000H, SI=0200H Count at 10200H =0A H

MOV AX, 0000 H

MOV SI, 0200 H

MOV CX, [SI]

BACK INC SI

INC SI

CMP AX, [SI]

J C GO

MOV AX, [SI]

GO LOOP BACK

MOV [0300], AX

HLT

LARGEST 8 BIT NUMBER IN 8 BIT DATA ARRAY:

DS=1000H, SI=0200H Count at 10200H =0A H

MOV AL, 00 H

MOV SI, 0200 H

MOV CX, [SI]

INC SI

BACK INC SI

CMP AL, [SI]

J NC GO

MOV AL, [SI]

GO LOOP BACK

MOV [0250], AL

HLT

SMALLEST 8 BIT NUMBER IN 8 BIT DATA ARRAY:

DS=1000H, SI=0200H Count at 10200H =0A H

MOV AL, 00 H

MOV SI, 0200 H

MOV CX, [SI]

INC SI

BACK INC SI

CMP AL, [SI]

J C GO

MOV AL, [SI]

GO LOOP BACK

MOV [0250], AL

HLT

Sum of series of 16 bit numbers sum is 16 bit: -

MOV AX, 0000 H

MOV SI, 0200 H

MOV CX, [SI]

BACK INC SI

INC SI

ADD AX, [SI]

LOOP BACK

MOV [0300], AX

HLT

Sum of series of 16 bit numbers sum is 32 bit: -

MOV AX, 0000 H

MOV BX, 0000 H

MOV SI, 0200 H

MOV CX, [SI]

BACK INC SI

INC SI

ADD AX, [SI]

J NC GO

INC BX

GO LOOP BACK

MOV [0300], AX

MOV [0400], BX

HLT

MOVE A BLOCK OF DATA (BYTES) FROM ONE LOCATION TO OTHER

DS=1000 H ES = 2000H

MOV SI, 0200 H

MOV DI, 0302 H

MOV CX, [SI]

INC SI

INC SI

BACK MOV SB // Interchange byte from SI & DI

INC SI

INC DI

LOOP BACK

HLT

MOVE A BLOCK OF DATA (WORDS) FROM ONE LOCATION TO OTHER

DS=1000 H ES = 2000H

MOV SI, 0200 H

MOV DI, 0300 H

MOV CX, [SI]

INC SI

INC SI

BACK MOV SW // Interchange word from SI & DI

INC SI INC SI

INC DI INC DI

LOOP BACK

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

ADD TWO 16 BIT NUMBER SUM IS 16 BIT OR MORE: -

DS=1000H, SI=0200H

MOV CH, 00 H // Initially carry is 0

MOV SI, 0200 H

MOV AX, [SI] // First data in AX

INC SI

INC SI

MOV CX, [SI] // Second data in CX

ADD AX, CX

INC SI

INC SI // To store result

J NC GO

INC CH // Increment carry

GO MOV [SI], AX // Store result

INC SI

MOV [SI], CH // Store carry

HLT

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

ONES COMPLEMENT OF A 8 BIT NUMBER: -

MOV AH, [SI]

NOT AH

INC SI

MOV [SI], AH

HLT

ONES COMPLEMENT OF A 16 BIT NUMBER: -

MOV AX, [SI]

NOT AX

INC SI

INC SI

MOV [SI], AX

HLT

SHIFT AN 8 BIT NUMBER LEFT BY TWO BITS: -

MOV AL, [SI]

ADD AL, AL

ADD, AL, AL

INC SI

MOV [SI], AL

HLT

SHIFT AN 16 BIT NUMBER LEFT BY TWO BITS: -

MOV AX, [SI]

ADD AX, AX

ADD, AX, AX

INC SI

INCSI

MOV [SI], AX

HLT

TWOS COMPLEMENT OF A 8 BIT NUMBER: -

DS=1000H, SI=0200H

MOV AH, [SI]

NEG AH

INC SI

MOV [SI], AH

HLT

TWOS COMPLEMENT OF A 16 BIT NUMBER: -

DS=1000H, SI=0200H

MOV AX, [SI]

NEG AX

INC SI

INC SI

MOV [SI], AX

HLT

MASK ON 8 LSBS OF A 16 BIT NUMBER: -

DS=1000H, SI=0200H

MOV AX, [SI]

OR AX, 00FF H

INC SI

INC SI

MOV [SI], AX

HLT

MASK ON 8 MSBS OF A 16 BIT NUMBER: -

DS=1000H, SI=0200H

MOV AX, [SI]

OR AX, FF00 H

INC SI

INC SI

MOV [SI], AX

HLT

MASK OFF 8 LSBS OF A 16 BIT NUMBER: -

DS=1000H, SI=0200H

MOV AX, [SI]

AND AX, FF00 H

INC SI

INC SI

MOV [SI], AX

HLT

MASK OFF 8 MSBS OF A 16 BIT NUMBER: -

DS=1000H, SI=0200H

MOV AX, [SI]

AND AX, 00FF H

INC SI

INC SI

MOV [SI], AX

HLT

Difference between 8086 & 8088 M.P

8088 8086

1. It has only 8 data lines 1. It has 16 data lines

2. It has 4 byte instruction Q. 2. It has 6 byte instruction Q.

3. Its pin 34 is SS0 bar. 3. Its pin 34 is BHE bar.

4. In min mode pin 28 is IO/M bar 4. In min mode pin 28 is M/IO bar

5. It does not have BHE bar. 5. It has BHE bar for higher order

address bus.

Introduction to 80186: -

1. 80186 is a 16 bit M.P.

2. It is a 68 pin IC with +5 V supply.

3. It consist of 2 8086 CPU.

4. It has 20 bit address bus.

5. It can operate on two different clock speed i.e. 8

MHz & 6 MHz.

6. It has 10 new instruction compared with 8086.

7. It has on chip timer, interrupt controller, DMA &

clock generator.

8. It has all the register same with 8086.

9. It has same address modes, instruction as of 8086.

Introduction to 80286: -

1. It is a 16 bit microprocessor.

2. Especially designed for multitasking & multiuser.

3. It can access upto16 MByteof memory.

4. It can operate from 8 MHz to 12.5 MHz.

5. It is a 68 pin DIP IC.

6. It has 24 address lines & 16 bit data lines.

7. It has same address modes, instruction as of 8086.

8. It consist of 4 units (Execution unit, bus unit, Instruction unit, address unit)

9. In protected mode of operation it can access upto1 gigabyte of memory.

Power PC

It is a RISC microprocessor designed to meet a standard which was jointly designed

by Motorola, IBM, and Apple Computer. The PowerPC standard specifies a

common instruction set architecture (ISA), allowing anyone to design and fabricate

Power PC processors. The PowerPC architecture is based on the IBM POWER

architecture used in IBM's workstations. Currently IBM and Motorola are working

on PowerPC chips. The PowerPC standard specifies both 32-bit and 64-bit data

paths. Early implementations were 32-bit (e.g. PowerPC 601); later higher-

performance implementations were 64-bit (e.g. PowerPC 620). A PowerPC has 32

integer registers (32- or 64 bit). The POWER CPU chip and PowerPC have a (large)

common core, but both have instructions that the other doesn't.

The PowerPC offers the following features that POWER does not:

The real time clock (upper and lower) was replaced with the timebase registers

(upper and lower)

64-bit instruction operands, registers, etc. (in 64 bit processors).

Introduction to 80386: -

1. It is 32 bit & improved version of 8086,80186 & 80286 M.P

2. Its register & ALU is 32 bit. As well its address & data bus is 32 bit.

3. Instruction, data read & write operation are two times faster then 80286.

4. Maximum size of physical memory is 64 MB.

5. It is available in two version: - 80386 DX & 80386 SX.

6. 80386 DX has 32 bit address & data bus.

7. 80386 SX has 16 bit data bus & 24 bit address bus.

8. It consist of timer, counter, interrupt, DMA on chip.

9. It can work in three modes: -

a) Real addressing modes

b) Protected virtual address modes

c) Virtual 8086 modes.

10. Internal architecture is same as of 80286.

Introduction to 80486: -

1. It is a 32 bit M.P with higher performance then 80386.

2. It consist of 1.2 million transistor & works three times faster

then 80386.

3. It has five stages of pipelining.

4. It has 30 bit address bus & 32 bit data bus.

5. It consist of timers, counters, DMA, interrupt controller on chip.

6. It can operate on 100 MHz.

7. It is software compatible with 80386.

8051 Microcontroller & Embedded System: -

What is Embedded System?

Embedded System is a collection of pure electronics

hardware & software to perform few dedicated task on

real time fashion.

Major components of Embedded System:-

1. Microcontroller (8051, AVR, PIC, ARM)

2. ADC/DAC/RTC

3. Motor(AC/DC/Stepper)

4. Sensor (Light/IR/Finger/Voice)

8051 is a general purpose 8 bit micro controller. 8 bit means its data bus & CPU is 8 bit wide.

Intel 8051 micro controller was designed by the company Intel. But is rarely available & costly

also. Therefore most of the company are using Atmel 89C51/89C52/89S51/89S52 micro

controller, which is having 100 % same configuration as of Intel 8051.

Major companies manufacturing the 8051 series micro controller : -

1. Intel / Atmel / Philips / Motorola / Dallas

Main features of 8051 series micro controller: -

1. 40 pin IC package DIP (Dual in line package)

2. 4K byte of flash memory (EEPROM) 000 H to FFF H

3. 128 byte of RAM 00H to 07 F

4. 4 Port, P0, P1, P2, P3 Each port of 8 bits, like P10, P11,P12, P13, P14, P15, P16 &

P17

P30, P31, P32..P37.

1. 2 Timers T0, T1

2. 2 Counters

3. 1 Serial Communication (UART)

Atmel 89C51 4K, 128, 2 Timer (4K Means 000H to FFFH)

Atmel 89C52 8K, 256, 3 Timer (8K Means 0000H to 1FFFH)

Atmel 89S51 4K, 128, 2 Timer, 1 Watch dog timer

Atmel 89S52 8K, 256, 3 Timer, 1 Watch dog timer

RAM ORGANISATION OF 8051

The 8051 has a bank of 128 bytes of Internal RAM. This Internal RAM is found on-chip

on the 8051 so it is the fastest RAM available, and it is also the most flexible in terms of

reading, writing, and modifying its contents.

The 128 bytes of internal ram is subdivided as shown on the memory map. The first 8

bytes (00h - 07h) are "register bank 0". Bit Memory also lives and is part of internal RAM.

Bit memory actually resides in internal RAM, from addresses 20h through 2Fh.

The 80 bytes remaining of Internal RAM, from addresses 30h through 7Fh, may be used

by user variables that need to be accessed frequently or at high-speed. This area is also

utilized by the microcontroller as a storage area for the operating stack.

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

The 8051 is a flexible microcontroller with a relatively large number of modes of

operations. Your program may inspect and/or change the operating mode of the 8051 by

manipulating the values of the 8051's Special Function Registers.

SFRs are accessed as if they were normal Internal RAM. The only difference is that

Internal RAM is from address 00h through 7Fh whereas SFR registers exist in the address

range of 80h through FFh.

Each SFR has an address (80h through FFh) and a name. The following chart provides a

graphical presentation of the 8051's SFRs, their names, and their address.

Program status (PSW) word of 8051

Cy Ac F0 RS1 RS0 OV x P

Cy Carry

Ac Auxiliary carry

P Parity

RS1 RS0

0 0 bank 0

0 1 bank 1

1 0 bank 2

1 1 bank 3

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

SFR OF 8051 MICROCONTROLLER

The Accumulator The Accumulator, as its name suggests, is used as a

general register to accumulate the results of a large number of instructions. It

can hold an 8-bit (1-byte) value and is the most versatile register

The " R" registers The "R" registers are a set of eight registers that are

named R0, R1, etc. up to and including R7.

The " B" Register The "B" register is very similar to the Accumulator in

the sense that it may hold an 8-bit (1-byte) value.

The Program Counter (PC) The Program Counter (PC) is a 2-byte

address which tells the 8051 where the next instruction to execute is found in

memory

M

i

c

r

o

p

r

o

c

e

s

s

o

r

/

M

i

c

r

o

c

o

n

t

r

o

l

l

e

r

&

E

m

b

e

d

d

e

d

S

y

s

t

e

m

P

r

a

v

e

e

n

K

r

.

M

a

l

i

k

,

R

G

E

C

E

n

g

.

C

o

l

l

e

g

e

,

M

e

e

r

u

t

+

9

1

-

9

7

1

9

4

3

7

7

1

1

ADDRESSING MODES: -

An "addressing mode" refers to how you are addressing a given memory location. In

summary, the addressing modes are as follows, with an example of each:

Immediate Addressing

MOV A,#20H MOV R4,#64H MOV B,40H

Direct Addressing

MOV A,30H MOV 56,A MOV B,04H

Indirect Addressing

MOV A,@R0 MOV @R1,B

Register Addressing

MOV A,R0 MOV R2,A ADD A,R7

STACK Addressing

Push 05 = Push R5 Pop 02 = Pop R2

ADC & DAC

A ADC, inputs an analog voltage or current and output the binary signal. In block diagram

form, it looks like this:

A DAC, on the other hand, inputs a binary number and outputs an analog voltage or

current signal. In block diagram form, it looks like this:

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Together, they are often used in digital systems to provide complete interface

with analog sensors and output devices for control systems such as those used

in automotive engine controls:

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Flash ADC

Also called the parallel A/D converter, this circuit is the simplest to understand. It is formed of a

series of comparators, each one comparing the input signal to a unique reference voltage. The

comparator outputs connect to the inputs of a priority encoder circuit, which then produces a binary

output. The following illustration shows a 3-bit flash ADC circuit. Vref is a stable reference voltage

provided by a precision voltage regulator as part of the converter circuit, not shown in the

schematic. As the analog input voltage exceeds the reference voltage at each comparator, the

comparator outputs will sequentially saturate to a high state. The priority encoder generates a

binary number based on the highest-order active input, ignoring all other active inputs.

Microprocessor / Microcontroller & Embedded System

Praveen Kr. Malik, RGEC Eng. College, Meerut +91-9719437711

Digital ramp ADC

Also known as the stairstep-ramp, or simply counter A/D converter. The basic idea is to

connect the output of a free-running binary counter to the input of a DAC, then compare

the analog output of the DAC with the analog input signal to be digitized and use the