Professional Documents

Culture Documents

Sequential Risc

Uploaded by

kb_lu232Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sequential Risc

Uploaded by

kb_lu232Copyright:

Available Formats

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

The RiSC-16 Instruction-Set Architecture

ENEE 646: Digital Computer Design, Fall 2002

Prof. Bruce Jacob

This paper describes a sequential implementation of the 16-bit Ridiculously Simple Computer

(RiSC-16), a teaching ISA that is based on the Little Computer (LC-896) developed by Peter Chen

at the University of Michigan.

1.

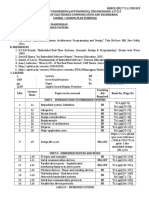

RiSC-16 Instruction Set

The RiSC-16 is an 8-register, 16-bit computer. All addresses are shortword-addresses (i.e. address

0 corresponds to the first two bytes of main memory, address 1 corresponds to the second two

bytes of main memory, etc.). Like the MIPS instruction-set architecture, by hardware convention,

register 0 will always contain the value 0. The machine enforces this: reads to register 0 always

return 0, irrespective of what has been written there. The RiSC-16 is very simple, but it is general

enough to solve complex problems. There are three machine-code instruction formats and a total

of 8 instructions. The instruction-set is given in the following table.

Assembly-Code Format

Meaning

add

regA, regB, regC

R[regA] <- R[regB] + R[regC]

addi

regA, regB, immed

R[regA] <- R[regB] + immed

nand

regA, regB, regC

R[regA] <- ~(R[regB] & R[regC])

lui

regA, immed

R[regA] <- immed & 0xffc0

sw

regA, regB, immed

R[regA] -> Mem[ R[regB] + immed ]

lw

regA, regB, immed

R[regA] <- Mem[ R[regB] + immed ]

bne

regA, regB, immed

if ( R[regA] != R[regB] ) {

PC <- PC + 1 + immed

(if label, PC <- label)

}

jalr

regA, regB

PC <- R[regB], R[regA] <- PC + 1

PSEUDO-INSTRUCTIONS:

nop

do nothing

halt

stop machine & print state

lli

regA, immed

R[regA] <- R[regA] + (immed & 0x3f)

movi

regA, immed

R[regA] <- immed

.fill

immed

initialized data with value immed

.space immed

zero-filled data array of size immed

The instruction-set is described in more detail (including machine-code formats) in The RiSC-16

Instruction-Set Architecture.

1

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

2.

RiSC-16 Instruction Control and Dataflow

The following figures illustrate the flow of information for each of the instruction types for a simple sequential implementationa scaled-down version of which has been done in discrete logic

(i.e. 4-bit TTL parts) . A final figure will put all of the instructions together into one framework.

Shaded boxes represent registers. Thick lines represent 16-bit buses.

ADD

Program Counter

+1

INSTRUCTION

MEMORY

ADD: 000 rA rB 0000 rC

TGT

SRC1

REGISTER FILE

SRC2

SRC2

SRC1

WE

CONTROL

ADD

SRC2

SRC1

This figure illustrates the flow-of-control for the ADD instruction. All three ports of the register

file are used, and the write-enable bit (WE) is set for the register file. The ALU control signal is a

simple ADD function.

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

ADDI

Program Counter

+1

INSTRUCTION

MEMORY

ADDI: 001 rA rB

simm-7

TGT

SRC1

REGISTER FILE

Sign-Extend-7

SRC1

WE

SRC2

ADD

CONTROL

SRC1

This figure illustrates the flow-of-control for the ADD IMMEDIATE instruction. Only two ports

of the register file are used; the second source operand comes directly from the instruction word.

The write-enable bit is set for the register file. The ALU control signal is a simple ADD function.

The Sign-Extend-7 logic extends the sign of the immediate value (as opposed to simply adding

zeroes at the top) and in so doing produces a twos complement number. The logic looks like this:

Bit:

15

ADDI:

14

13

12

001

11

10

reg A

reg B

simm-7 (-64 to 63)

SRC2 OPERAND:

Bit:

15

14

13

12

11

10

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

NAND

Program Counter

+1

INSTRUCTION

MEMORY

NAND: 010 rA rB 0000 rC

TGT

SRC1

REGISTER FILE

SRC2

SRC2

SRC1

WE

CONTROL

NAND

SRC2

SRC1

This figure illustrates the flow-of-control for the BITWISE NAND instruction. All three ports of

the register file are used, and the write-enable bit is set for the register file. The ALU control signal

is a BITWISE NAND function.

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

LUI

Program Counter

+1

INSTRUCTION

MEMORY

LLI: 011 rA

imm-10

TGT

REGISTER FILE

Left-Shift-6

WE

SRC2

PASS1

CONTROL

SRC1

This figure illustrates the flow-of-control for the LOAD UPPER IMMEDIATE instruction. This

instruction replaces the top ten bits of an instruction with ten bits found in the instruction word

and zeroes out the bottom six bits. Only one port of the register file is usedthe write portas all

of the bits destined for the register file are zero or come directly from the instruction word. The

write-enable bit is set for the register file.

Compared to ADDI, the immediate-manipulation logic for LUI is slightly different; the logic for

Left-Shift-6 looks like this:

Bit:

15

LUI:

14

13

12

011

11

10

reg A

imm-10 (0 to 1023)

ZERO

SRC1 OPERAND:

Bit:

15

14

13

12

11

10

The second argument to the ALU (SRC2) is ignored; this is accomplished by setting the ALU

control to be PASS1, which sends through the first argument unchanged. This same ALU control

will be used for the JALR instruction as well. One could alternatively zero-extend the immediate

value and use a SHIFT input to the ALU while inputting the value 6 at the other ALU-input.

However, the illustrated mechanism seems slightly less complicated.

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

SW

Program Counter

+1

INSTRUCTION

MEMORY

SW: 100 rA rB

simm-7

SRC1

REGISTER FILE

DATA

MEMORY

SRC2

DATA

SRC2

Sign-Extend-7

ADDR

SRC1

WE=0

WE

SRC2

ADD

CONTROL

SRC1

This figure illustrates the flow-of-control for the STORE DATA WORD instruction. Only two

ports of the register file are used; the register files write port (TGT) is not used. The SRC2 output

port does not feed the ALU (as it normally does), but rather the DATA input of data memory. This

is the value to be written to memory. The second ALU input is an immediate value that comes

directly from the instruction word.

The write-enable bit is set for data memory but not for the register file. The ALU control signal is

a simple ADD function. The result of the ALU ADD goes to the ADDR port of data memory,

which responds by latching the data word at the specified address.

Note that the rA field of the instruction, which is normally tied to the register files TGT specifier,

is instead tied to the SRC2 specifier.

The Sign-Extend-7 logic extends the sign of the immediate value (as opposed to simply adding

zeroes at the top) and in so doing produces a twos complement number. The logic looks like this:

Bit:

15

SW:

14

13

12

101

11

10

reg A

reg B

simm-7 (-64 to 63)

SRC2 OPERAND:

Bit:

15

14

13

12

11

10

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

LW

Program Counter

+1

INSTRUCTION

MEMORY

LW: 101 rA rB

simm-7

TGT

SRC1

DATA

MEMORY

REGISTER FILE

Sign-Extend-7

ADDR

SRC1

WE

WE=0

SRC2

ADD

CONTROL

SRC1

This figure illustrates the flow-of-control for the LOAD DATA WORD instruction. Only two ports

of the register file are used; the second source operand comes directly from the instruction word.

The write-enable bit is set for the register file but not for data memory. The ALU control signal is

a simple ADD function. The result of the ALU ADD does not go to the register file but rather to

the ADDR port of data memory, which responds by reading out the corresponding data word. This

value is stored in the register file.

As in SW, the Sign-Extend-7 logic extends the sign of the immediate value (as opposed to simply

adding zeroes at the top) and in so doing produces a twos complement number.

Bit:

15

LW:

14

13

12

100

11

10

reg A

reg B

simm-7 (-64 to 63)

SRC2 OPERAND:

Bit:

15

14

13

12

11

10

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

BNE

Program Counter

+1

INSTRUCTION

MEMORY

BNE: 110 rA rB

ADD

Sign-Ext-7

simm-7

SRC1

REGISTER FILE

SRC2

SRC2

SRC1

WE=0

BR

CONTROL

EQ?

SRC2

SRC1

EQ!

This figure illustrates the flow-of-control for the BRANCH-IF-NOT-EQUAL instruction. Like

STORE DATA WORD instruction, it does not write a result to the register file. Two values are

read from the register file and compared. The ALU control signal is a request for a test of equality

(labeled EQ? in the diagram). If the ALU does not support an equality test, a SUBTRACT signal

can be used, as most ALUs do have a 1-bit output signal that indicates a zero-value result: the two

combined produce the same results as an EQ signal.

The result of the comparison determines which of two values are to be placed into the program

counter. If the two values in the register file are equal, the value to be latched in the program

counter is the sum

PC + 1

(which is the normal program counter update value). If the two values read from the register file

are NOT equal, the value to be latched in the program counter is the sum

PC + 1 + (sign-extended immediate value)

(note that the sign extension is just like in LW and SW). We have shown a small portion of the

CONTROL module: that portion controlling the PC mux. The choice between PC+1 and

PC+1+IMM is represented by an AND of the negated EQ! output of the ALU and a signal that

represents CONDITIONAL BRANCH (i.e. the 3-bit opcode is BNE:110). Thus, if the opcode is a

conditional branch and the two values are not equal, choose PC+1+IMM, otherwise choose

PC+1.

Note that the rA field of the instruction, which is normally tied to the register files TGT specifier,

is instead tied to the SRC2 specifier.

8

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

JALR

Program Counter

+1

INSTRUCTION

MEMORY

JALR: 111 rA rB 0000000

TGT

SRC1

REGISTER FILE

SRC1

WE

CONTROL

PASS1

SRC2

SRC1

This figure illustrates the flow-of-control for the JUMP-AND-LINK-THROUGH-REGISTER

instruction. This function uses two of the register files three ports. A value is read from the register file and placed directly into the program counter, and the sum

PC + 1

(which is normally latched into the program counter) is written to a specified register in the register file.

The ALU signal is a PASS signal for the SRC1 operandthe ALU is instructed to perform no

function, only pass the SRC1 operand directly through. This value is written into the program

counter.

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

Putting it All Together

Program Counter

+1

ADD

INSTRUCTION

MEMORY

Sign-Ext-7

MUXtgt

OP rA rB

rC

TGT

DATA OUT

REGISTER FILE

DATA

MEMORY

TGT

SRC1

SRC2

SRC2

MUXrf

SRC1

DATA IN

ADDR

WErf

Left-Shift-6

Sign-Extend-7

WEdmem

MUXalu2

MUXalu1

MUXpc

CONTROL

FUNCalu

SRC2

SRC1

EQ!

This diagram combines all of the previous data and control paths into one complete framework.

To accommodate all control and data paths, there are a number of muxes that choose the direction

of data flow. These muxes are operated by the CONTROL module, which depends on only two

inputs:

1. the 3-bit OPCODE of the instruction; and

2. the 1-bit EQ! signal from the ALU (which, for the BNE instruction, indicates that the two

operands are equalfor all other instructions this signal is ignored).

The CONTROL module is essentially a decoder. It takes these input signals in and sets a number

of outgoing signals that control the ALU, a host of multiplexers, and the write functions of the

register file and data memory. At the beginning of every cycle, a new program counter value is

latched, which causes a new instruction word to be read out and a new opcode to be sent to the

10

ENEE 646: Digital Computer Design The RiSC-16 Instruction-Set Architecture

CONTROL module. The CONTROL module simply sets the control lines as appropriate for the

instruction, and all of the control and data paths are set up: after delays through the register file,

the ALU, the data memory, and the corresponding muxes, all of the signals stabilize. At this point,

the newly produced values are latched (in the register file, the data memory and/or the program

counter), and the new program counter causes a new instruction to be read from the instruction

memory.

These are the signals that the CONTROL module exports:

FUNCalu This signal instructs the ALU to perform a given function.

MUXalu1

This 1-bit signal controls the mux connected to the SRC1 input of the ALU. The

mux chooses between the SRC1 output of the register file and the left-shifted immediate value (to be used for LUI instructions).

MUXalu2

This 1-bit signal controls the mux connected to the SRC2 input of the ALU. The

mux chooses between the SRC2 output of the register file and sign-extended immediate value (to be used for ADDI, LW, and SW instructions).

MUXpc

This 2-bit signal controls the mux connected the program counter. The mux chooses

between the output of the ALU, the output of the +1 adder that produces the sum

PC+1 on every cycle

MUXrf

This 1-bit signal controls the mux connected to the register files SRC2 operand

specifier, a 3-bit signal that determines which of the registers will be read out onto

the 16-bit SRC2 data output port. The mux chooses between the rA and rC fields of

the instruction word.

MUXtgt

This 2-bit signal controls the mux connected to the register files 16-bit TGT data

input port, which carries the data to be written to the register file (provided the writeenable bit of the register file is set). The mux chooses between the output of the

ALU, the output of the data memory, and the output of the +1 adder tied to the program counter.

WErf

This 1-bit signal enables or disables the write port of the register file. If the signal is

high, the register file can write a result. If it is low, writing is blocked.

WEdmem This 1-bit signal enables or disables the write port of the data memory. If the signal

is high, the data memory can write a result. If it is low, writing is blocked.

11

You might also like

- RISC-16 Processor ISADocument4 pagesRISC-16 Processor ISAkb_lu232No ratings yet

- The Pipelined RiSC-16 ComputerDocument9 pagesThe Pipelined RiSC-16 Computerkb_lu232No ratings yet

- Kenny Lu ResumeDocument1 pageKenny Lu Resumekb_lu232No ratings yet

- T 20 FDocument4 pagesT 20 Fkb_lu232No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Digital Planet: Tomorrow's Technology and You: Hardware BasicsDocument20 pagesDigital Planet: Tomorrow's Technology and You: Hardware BasicsHannah Esey Aquino PaquinNo ratings yet

- QCC300x I S: User GuideDocument27 pagesQCC300x I S: User GuideСерхио Димитрио100% (1)

- F5883M enDocument4 pagesF5883M enPassenger MedeamNo ratings yet

- Synchronous and Asynchronous TransmissionDocument3 pagesSynchronous and Asynchronous Transmissionpthepronab0% (1)

- SEMICONDUCTOR TECHNICAL DATA FOR MC145026/D ENCODER AND DECODERSDocument20 pagesSEMICONDUCTOR TECHNICAL DATA FOR MC145026/D ENCODER AND DECODERSMilojko DrzevljaninNo ratings yet

- EE200 Exp 09Document4 pagesEE200 Exp 09pilim32No ratings yet

- SV InterfaceDocument84 pagesSV InterfaceAbhishek SrivastavaNo ratings yet

- 8085 Programs UpdatedDocument1 page8085 Programs Updatedsandeepshrestha77407No ratings yet

- Interoperability Definition For IEC 870-5-101 ProtocolDocument20 pagesInteroperability Definition For IEC 870-5-101 ProtocolArun KumarNo ratings yet

- L5 Arithmetic Logic and Shift InstrDocument13 pagesL5 Arithmetic Logic and Shift InstrCristi DanNo ratings yet

- Digital Logic Lab 7Document3 pagesDigital Logic Lab 7Dinesh PudasainiNo ratings yet

- IT Short CourceDocument16 pagesIT Short CourceAdmin CvmrmptNo ratings yet

- Unit 3 ADocument39 pagesUnit 3 AMohammed Fakhruddin Hasan NizamiNo ratings yet

- Question BankDocument4 pagesQuestion BankChetan GowdaNo ratings yet

- LESSON 7 - Logic InstructionsDocument9 pagesLESSON 7 - Logic Instructionsamae marshallNo ratings yet

- Computer Applications in Pharmacy Data ProcessingDocument15 pagesComputer Applications in Pharmacy Data Processingharoon shahzadNo ratings yet

- 1 - Basic Computer OrganizationDocument88 pages1 - Basic Computer OrganizationshabanaNo ratings yet

- SDM230 Smart Meter Modbus Protocol Implementation GuideDocument12 pagesSDM230 Smart Meter Modbus Protocol Implementation GuideJun AballeNo ratings yet

- 03.embedded System - Question BankDocument31 pages03.embedded System - Question BankK.MATHAN HICET STAFF EEENo ratings yet

- Bowman - Rice ITERA 2007 Dark RoomDocument13 pagesBowman - Rice ITERA 2007 Dark Roomsbojja1No ratings yet

- TLE4997/98 Evaluation Kit Software GuideDocument26 pagesTLE4997/98 Evaluation Kit Software GuideKhangLeNo ratings yet

- S5 FCS FunctionsDocument45 pagesS5 FCS Functionsplim5ollNo ratings yet

- 0-9 Words per Letter Electronics AcronymsDocument4 pages0-9 Words per Letter Electronics AcronymsMalvin Roix OrenseNo ratings yet

- Digital-Output Relative Humidity & Temperature Sensor/module DHT22 (DHT22 Also Named As AM2302)Document10 pagesDigital-Output Relative Humidity & Temperature Sensor/module DHT22 (DHT22 Also Named As AM2302)Novan SyarohmatNo ratings yet

- MQTT V3.1 Protocol SpecificationDocument41 pagesMQTT V3.1 Protocol SpecificationGiuseppe OnorevoliNo ratings yet

- Interchange™ Comm Control Module, MX5 Series: Installation and Operations ManualDocument20 pagesInterchange™ Comm Control Module, MX5 Series: Installation and Operations ManualNicolii RamonNo ratings yet

- TX1100 TcSystemManager ENDocument469 pagesTX1100 TcSystemManager ENDriss MohamedNo ratings yet

- MAIT TutorialDocument54 pagesMAIT TutorialMadhav LohchabNo ratings yet

- Profibus ApplicomDocument116 pagesProfibus ApplicomzinouNo ratings yet

- Contadores STEP7Document14 pagesContadores STEP7Rodrigo SudarioNo ratings yet