Professional Documents

Culture Documents

Application Note 5336: Gate Drive Optocoupler Basic Design For IGBT / MOSFET Applicable To All Gate Drive Optocouplers

Uploaded by

elecompinnOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Application Note 5336: Gate Drive Optocoupler Basic Design For IGBT / MOSFET Applicable To All Gate Drive Optocouplers

Uploaded by

elecompinnCopyright:

Available Formats

Gate Drive Optocoupler Basic Design for IGBT / MOSFET

Applicable to All Gate Drive Optocouplers

Application Note 5336

Introduction

IGBT/MOSFET Gate Resistor

This application note covers the topic of calculating gate

driver power and thermal dissipation of the gate drive

optocoupler IC. Gate drive optocouplers are used to

drive, turning-on and off, power semiconductor switches,

MOSFETs / IGBTs. The gate drive power calculation can be

divided into three parts; power consumed or lost in the

internal circuitry of the driver, power sent to the power

semiconductor switches (IGBT/MOSFET) and power lost

at the external component between the driver IC and the

power semiconductor switch, e.g. across external gate

resistor. In the following example, we will discuss an IGBT

gate driver design using the Avago ACPL-332J (2.5nApeak

intelligent gate driver). This design guide is applicable for

MOSFET gate drivers also.

When choosing the value of RG, it is important to look

from the point from both gate driver IC and the power

semiconductor switches, MOSFET/IGBT. For the gate

driver IC, we choose an RG that is within the IC maximum

allowable power disippation rating while sourcing/

sinking the highest possible driver current. From the IGBT

or MOSFET point of view, the gate resistor influences the

voltage change dVCE/dt and current change diC/dt during

the turn on and turn off period.

So it is important when a designer chooses an IGBT or

MOSFET, the appropriate gate driver optocoupler is also

chosen as the current and power rating of this driver

determine how fast the IGBT or MOSFETcan turn on or

turn off.

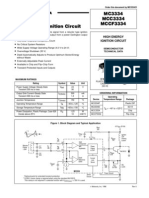

13

VCC2

UVLO

ANODE

CATHODE

6, 7

D

R

I

V

E

R

5, 8

LED1

11

14

DESAT

9, 12

SHIELD

VOUT

DESAT

VEE

VCLAMP

VCC1

FAULT

VS

2

3

10

LED2

16

1, 4

15

SHIELD

Figure 1. Block Diagram of ACPL-332J

VCLAMP

VE

VLED

Gate Drive Power Operation within IC Maximum Allowable

Power Ratings

The power dissipation of the gate drive optocoupler is a

combination of output-side power to the IGBT/MOSFET,

red circle, and the input-side power due to input LED

power dissipation, blue circle. The power dissipation for

the second LED used for fault feedback is neglected as

the current to drive the open-collector transistor is small.

The calculation steps are:

1. Calculate the minimum desired RG according to the

maximum peak gate current

2. Calculate total power dissipation

3. Compare the input and output power dissipation

calculated in step #2 to the maximum recommended

dissipation for the IC. (If the maximum recommended

level has been exceeded, it may be necessary to raise

the value of RG to lower the switching power and

repeat step #2.)

In this example, the total input and output power dissipation of the ACPL-332J is calculated given the following

conditions:

Rg = (VCC2 VEE VOL)/ IOL = (18 V - (-5 V) - 6.3)/ 2.5 A

= 6.68 (approximately 6.8 )

Note: The value of the gate resistance has a significant

impact on the dynamic performance of IGBTs/MOSFETs.

A smaller gate resistor charges and discharges the power

transistor input capacitance faster, reducing switching

times and switching losses. The trade off is that this could

lead to higher voltage oscillations. In the MOSFET and

IGBT datasheet, there is usually a recommended gate

resistor which is used for the datasheet characterization.

However, a designer should be cautious not to over-drive

the gate drive IC by using the recommended gate resistance from the IGBT or MOSFET datasheet.

Step II: Calculate total power dissipation in the gate driver:

The total power dissipation (PT ) is equal to the sum of the

input-side power (PI) and output-side power (PO) dissipation:

PT = PI + PO

IG = ION, MAX ~ 2.5 A

PI = IF(ON) ,max * VF,max

VCC2 = 18 V

where,

VEE = -5 V, (Note: VEE = 0 V if negative voltage supply is

not required in application)

fSWITCH = 15 kHz

IF(ON),max = 12 mA

VF,max = 1.95 V

The IF(ON) can be found in the recommended operting

conditions and VF can be found in the ACPL-332J datasheet, Table 5 of the electrical specifications.

Ambient Temperature = 70 C

Step I: Calculate RG minimum from IOL peak specification:

To find the peak charging lOL assume that the gate is

initially charged to the steady-state value VCC. For the

ACPL-332J, the voltage drop is linearly approximated as

6.3 V for 2.5 A output at 70 C (Fig 2: VOL vs IOL). Therefore

apply the following relationship:

Electrical Specification

Input Forward Voltage, VF

Min

Typ

Max

Units

1.2

1.6

1.95

PO = PO(BIAS) + PO(SWTICH)

VOL - LOW OUTPUT VOLTAGE DROP - V

= ICC2.MAX * (VCC2VEE ) + VGE * QG * fSWITCH

8

where,

_ _ _ _ 100 o C

______ 25 o C

--------- -40 o C

7

6

PO(BIAS)

PO(SWITCH) = Driver power for charging and discharging

of device gate capacitances.

5

4

ICC2.MAX = Supply current to power internal circuity

3

2

1

0

0.5

1.5

IoL - OUTPUT LOW CURRENT - A

Figure 2. VOL vs IOL

= Steady-state power in the driver due to

biasing the device.

VGE

= VCC2 + |VEE|

QG

= Total gate charge of the IGBT or MOSFET

as described in the manufacturer specification (Illustrated in Figure 3) = 240 nC

(approximation for a 100 A IGBT)

fSWITCH

= Switching frequency of application

2.5

Using the above information, we calculate both PI and PO

below:

The output detector junction temperature is given by:

PI = 12 mA * 1.95 V = 23.4 mW

Using the qJ-P = q9-12 = 30 C/W (ACPL-332J Table 7,

Package Characteristic) and a TA of 70 C and assuming

the thermal resistance from pin to ambient, qP-A is

50 C/W:

PO = PO(BIAS) + PO(SWITCH)

= 5.0 mA * (18 V (5 V)) + (18 V + 5 V) * 240nC * 15 kHz

= 115 mW + 82.8 mW

TJ = PD *( qJ-P + qP-A) + TA

TJ = 197.8*(30+50) + 70 C = 85.8 C

= 197.8 mW

If the juntion temperature is higher than the maximum

junction temperature rating (in this case 125 C), the

desired specification must be derated according.

VGE(V)

+VGE (VCC2)

Designers should note that the thermal resistance

between pin to ambient is also the PCB heatsink thermal

resistance. This thermal resistance is then dependent on

the area on the PCB and the free air-flow.

Further Topics:

QG(C)

-VGE (VEE)

QG

Figure 3. Typical IGBT Gate Charge Curve

Step III: Compare the calculated power dissipation with the

absolute maximum values in the IC:

For the ACPL-332J, the maximum power dissipation can

be found in Table 3 of the ACPL-332J data sheet. Also, it

requires a derating of 10 mW/C if the operating temperature is above 90 C (Note. 2 ACPL-332J datasheet).

Absolute Maximum Rating

Min

Max

Units

Output IC Power Dissipataion, Po

600

mW

Input IC Power Dissipation, PI

150

PI = 23.4 mW < 150 mW (abs. max.) )

OK

PO = 197.8 mW < 600 mW (abs. max.) ) OK

Therefore, the power dissipation absolute maximum

rating has not been exceeded for the above example.

Note: Heat dissipation for different packages require derating when

the operating temperature exceed a certain level. For ACPL-332J,

as operating temperature is below 90 C, derating is not necessary.

Operating temperature is different for different products

Another method to check if the device is within the

maximum limits is to calculate the junction temperature

of the device. We continue to use the example provided

earlier.

Power dissipation, PD = 23.4 + 197.8 = 221.2 mW

Higher Output Current Using an External Current Buffer:

To increase the IGBT gate drive current, a non-inverting

current buffer (such as the NPN/PNP buffer shown in

Figure 75 of HCPL-316J data sheet) may be used. Inverting

types are not compatible with the desatura-tion fault

protection circuitry and should be avoided. To preserve

the slow IGBT turn-off feature during a fault condition,

a 10 nF capacitor should be connected from the buffer

input to VEE and a 10 resistor inserted between the

output and the common NPN/PNP base. The MJD44H11/

MJD45H11 pair is appropriate for currents up to 8 A

maximum. The D44VH10/ D45VH10 pair is appropriate

for currents up to 15 A maximum.

Thermal Model

Most of the steady state thermal models for gate drive

optocouplers can be found in AN1087. The thermal resistance values given in this model can be used to calculate

the temperatures at each node for a given operating

condition.

HCPL-316J

VE

16

VLED2+

15

DESAT

14

VCC2

13

VC

12

VOUT

11

VEE

10

VEE

100 pF

MJD44H11 or

D44VH10

4.5

10

2.5

10 nF

MJD45H11 or

D45VH10

15 V

-5 V

Figure 4. Current Buffer for Increased Drive Current

3

Printed Circuit Board Layout Considerations

Adequate spacing should always be maintained between

the high voltage isolated circuitry and any input referenced circuitry. Care must be taken to provide the same

minimum spacing between two adjacent high-side

isolated regions of the printed circuit board. Insufficient

spacing will reduce the effective isolation and increase

parasitic coupling that will degrade CMR performance.

The placement and routing of supply bypass capacitors

requires special attention. During switching transients,

the majority of the gate charge is supplied by the bypass

capacitors. Maintaining short bypass capacitor trace

lengths will ensure low supply ripple and clean switching

waveforms.

Figure 5 below shows an example PCB layout using the

HCPL-316J gate driver optocoupler. Ground Plane con-

nections are necessary for pin 4 (GND1) and pins 9 and

10 (VEE) in order to achieve maximum power dissipation

as the HCPL-316J is designed to dissipate the majority

of heat generated through these pins. This is also applicable for the ACPL-332J. For this case, the ground plane

connections are pin 1, pin 4 (VSS) and pin 4 (VSS), pin 9

and 12 (VEE). Actual power dissipation will depend on

the application environment (PCB layout, air flow, part

placement, etc.) See Application Note 1087 or details on

how to estimate junction temperature.

The layout examples in Figure 5 have good supply

bypassing and thermal properties, exhibit small PCB footprints, and have easily connected signal and supply lines.

The four examples cover single sided and double sided

component placement, as well as minimal and improved

performance circuits.

Figure 5. Recommended layout(s)

For product information and a complete list of distributors, please go to our web site:

www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries.

Data subject to change. Copyright 2005-2014 Avago Technologies. All rights reserved.

AV02-0421EN - February 25, 2014

You might also like

- Application Note 9017 Manufacturing Technology of A Small Capacity Inverter Using A Fairchild IGBTDocument28 pagesApplication Note 9017 Manufacturing Technology of A Small Capacity Inverter Using A Fairchild IGBTRajesh VyasNo ratings yet

- Application Note 1335: Main Applications and Selection of Gate Driver OptocouplersDocument8 pagesApplication Note 1335: Main Applications and Selection of Gate Driver OptocouplerselecompinnNo ratings yet

- Drive IGBTs up to 400 A & 1200 VDocument9 pagesDrive IGBTs up to 400 A & 1200 VKaveh DadkhahNo ratings yet

- Forward Design 300W STmicroelectronics App NoteDocument10 pagesForward Design 300W STmicroelectronics App Notecristi7521No ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- Dual Output Voltage Regulator With Power Saving: BA44W12SATDocument10 pagesDual Output Voltage Regulator With Power Saving: BA44W12SATBeatris Medellin MendozaNo ratings yet

- AN5004Document5 pagesAN5004rdc02271No ratings yet

- Feature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerDocument11 pagesFeature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerEnéas BaroneNo ratings yet

- Trickle-Charge IC For Two-Cell, Lithium-Ion BatteriesDocument8 pagesTrickle-Charge IC For Two-Cell, Lithium-Ion BatteriesDary CalaçaNo ratings yet

- L6565Document18 pagesL6565Sergio Daniel BarretoNo ratings yet

- An 4160Document8 pagesAn 4160aurumstar2000No ratings yet

- Stgp7Nc60Hd Stgf7Nc60Hd - Stgb7Nc60Hd: N-Channel 14A - 600V - To-220/To-220Fp/D Pak Very Fast Powermesh™ IgbtDocument15 pagesStgp7Nc60Hd Stgf7Nc60Hd - Stgb7Nc60Hd: N-Channel 14A - 600V - To-220/To-220Fp/D Pak Very Fast Powermesh™ IgbtMikaNo ratings yet

- Skhi 23 12Document11 pagesSkhi 23 12Shaun Dwyer Van HeerdenNo ratings yet

- Oz9938 PDFDocument12 pagesOz9938 PDFCarlosNo ratings yet

- Hardware Used - Power Supply and MicrocontrollerDocument46 pagesHardware Used - Power Supply and MicrocontrollerRocky SinghNo ratings yet

- Datasheet NECDocument20 pagesDatasheet NECPham Trung KienNo ratings yet

- Application Note: Power Card For Motor DriveDocument13 pagesApplication Note: Power Card For Motor DriveHamid BassourNo ratings yet

- UDx2916 DatasheetDocument10 pagesUDx2916 DatasheetBruno NascimentoNo ratings yet

- 5101 Motor DriverDocument11 pages5101 Motor DriverMoise CristinaNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Document15 pagesObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)teomondoNo ratings yet

- La4628 PDFDocument8 pagesLa4628 PDFRICHIHOTS2No ratings yet

- PD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Document5 pagesPD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Osama YaseenNo ratings yet

- Single Synchronous Buck PWM DC-DC ControllerDocument16 pagesSingle Synchronous Buck PWM DC-DC Controllerbachet56No ratings yet

- VIPower: 10W POWER SMPS USING VIPer22A FOR AIR-CONDITIONER APPLICATIONDocument8 pagesVIPower: 10W POWER SMPS USING VIPer22A FOR AIR-CONDITIONER APPLICATIONLullaby summerNo ratings yet

- Reversible Motor Driver IC GuideDocument8 pagesReversible Motor Driver IC Guideeldel81No ratings yet

- 20 W 2-Channel BTL AF Power Amplifier For Car Stereos: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersDocument9 pages20 W 2-Channel BTL AF Power Amplifier For Car Stereos: SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquartersfernandes66No ratings yet

- U26 U27 U28 U29 Ap1538 PDFDocument13 pagesU26 U27 U28 U29 Ap1538 PDFMichel SomersNo ratings yet

- An 9742Document12 pagesAn 9742Alejandra SeguraNo ratings yet

- WIRE LESS Land Mine Detection Robo-VehicleDocument35 pagesWIRE LESS Land Mine Detection Robo-VehicleDebashish BeheraNo ratings yet

- Green-Mode PWM Controller: General Description FeaturesDocument10 pagesGreen-Mode PWM Controller: General Description FeaturesLuis Luis GarciaNo ratings yet

- An 9742Document12 pagesAn 9742EmersonMagnoMoraesNo ratings yet

- SG 6841 TDocument14 pagesSG 6841 TBayron Salazar SaborioNo ratings yet

- REH984b 06aDocument16 pagesREH984b 06achetan_harsha_1No ratings yet

- Linkcv Family DatasheetDocument18 pagesLinkcv Family DatasheetaisanasNo ratings yet

- Data Sheet: MGA-425P8Document15 pagesData Sheet: MGA-425P8Aparna BhardwajNo ratings yet

- BD9848Document5 pagesBD9848Henry CastandNo ratings yet

- 161 20551 0 FS7M0880Document16 pages161 20551 0 FS7M0880Edwin Vitovis TorresNo ratings yet

- Uc 3854Document12 pagesUc 3854Leandro CoradiNo ratings yet

- Uc3842 Monitor Power Supply Regulator IcDocument7 pagesUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaNo ratings yet

- LA4628Document9 pagesLA4628jgpbNo ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFDhiran NishantNo ratings yet

- 700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolDocument6 pages700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolNathan WilliamsNo ratings yet

- HS8108Document8 pagesHS8108Miloš ZorićNo ratings yet

- An 1599Document20 pagesAn 1599nisha770No ratings yet

- LA4555 Monolithic Linear ICDocument11 pagesLA4555 Monolithic Linear ICMiloud ChouguiNo ratings yet

- Data Sheet STK672Document21 pagesData Sheet STK672Mario Karma LeivaNo ratings yet

- UDN2916Document10 pagesUDN2916ejoaomelchiorsNo ratings yet

- Datasheet MC3334Document6 pagesDatasheet MC3334odipasNo ratings yet

- AN1895 - L6562 375W Step by StepDocument16 pagesAN1895 - L6562 375W Step by Stepbetodias30No ratings yet

- IRF7807VD2: Fetky™ Mosfet / Schottky DiodeDocument9 pagesIRF7807VD2: Fetky™ Mosfet / Schottky DiodeMartin TorresNo ratings yet

- LD7552 DS 00Document10 pagesLD7552 DS 00BRIGHT_SPARKNo ratings yet

- Mach Cong Suat Cau H - Lmd18200Document14 pagesMach Cong Suat Cau H - Lmd18200hieuhuech1No ratings yet

- Design of Fast Switching Igbt Gate Driver For High Rated ModulesDocument5 pagesDesign of Fast Switching Igbt Gate Driver For High Rated ModulesGarima GuptaNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- SD4840 4841 4842 4843 4844Document11 pagesSD4840 4841 4842 4843 4844sontuyet82No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 1S9H27 20-6-08 AGyEV34-en PDFDocument212 pages1S9H27 20-6-08 AGyEV34-en PDFelecompinnNo ratings yet

- Lekemi GPS Tracker User ManualDocument72 pagesLekemi GPS Tracker User ManualelecompinnNo ratings yet

- 1S9H27 20-6-08 AGyEV34-en PDFDocument212 pages1S9H27 20-6-08 AGyEV34-en PDFelecompinnNo ratings yet

- 2000C RangeDocument1 page2000C RangeelecompinnNo ratings yet

- Industry: Position and Solid State Sensing: Magnetoresistive SensorsDocument3 pagesIndustry: Position and Solid State Sensing: Magnetoresistive SensorselecompinnNo ratings yet

- LWS ManulwsalDocument26 pagesLWS ManulwsalelecompinnNo ratings yet

- 1S9H27 20-6-08 AGyEV34-en PDFDocument212 pages1S9H27 20-6-08 AGyEV34-en PDFelecompinnNo ratings yet

- An 9020Document25 pagesAn 9020Reshmi Parikal RaghavanNo ratings yet

- 2SB764/2SD863: Voltage Regulator, Relay Lamp Driver Electrical Equipment ApplicationsDocument4 pages2SB764/2SD863: Voltage Regulator, Relay Lamp Driver Electrical Equipment ApplicationsrobertjosepNo ratings yet

- Hcpleed 7840Document12 pagesHcpleed 7840elecompinnNo ratings yet

- 2SC4429Document5 pages2SC4429Marilou Lopez ValenzuelaNo ratings yet

- PNP Silicon AF Transistors: V V V I I I I P T TDocument5 pagesPNP Silicon AF Transistors: V V V I I I I P T TelecompinnNo ratings yet

- TLP 3022Document6 pagesTLP 3022elecompinnNo ratings yet

- NPN Silicon AF Power Transistor: BDP951 ... BDP955Document5 pagesNPN Silicon AF Power Transistor: BDP951 ... BDP955elecompinnNo ratings yet

- S3esk Rotary Encoder InterfaceDocument10 pagesS3esk Rotary Encoder InterfaceelecompinnNo ratings yet

- PDF ResolverDocument2 pagesPDF ResolverelecompinnNo ratings yet

- 85774Document3 pages85774elecompinnNo ratings yet

- Brake Control Bs3: Liftequip GMBH Elevator ComponentsDocument1 pageBrake Control Bs3: Liftequip GMBH Elevator ComponentselecompinnNo ratings yet

- Braking Unit Yaskawa - CDBR - 4045BDocument54 pagesBraking Unit Yaskawa - CDBR - 4045BAnoop KumarNo ratings yet

- Intelligent elevator rescue device controller user's manualDocument5 pagesIntelligent elevator rescue device controller user's manualelecompinnNo ratings yet

- Traction in ElevatorsDocument3 pagesTraction in ElevatorsПавле Крстевски100% (1)

- PG MRL Chain 950Document16 pagesPG MRL Chain 950elecompinnNo ratings yet

- EEEAAWEL650Document239 pagesEEEAAWEL650elecompinnNo ratings yet

- 1S9BREN - 11 1 13 - ADL200 SYN FP - enDocument126 pages1S9BREN - 11 1 13 - ADL200 SYN FP - enelecompinnNo ratings yet

- 2 - en 81 Standards Overviwe Philippe CasteleynDocument20 pages2 - en 81 Standards Overviwe Philippe Casteleynelecompinn100% (2)

- 2mbi450u4e 120Document13 pages2mbi450u4e 120elecompinnNo ratings yet

- Encoder S Short FormDocument2 pagesEncoder S Short FormelecompinnNo ratings yet

- PG MRL Chain 950Document16 pagesPG MRL Chain 950elecompinnNo ratings yet

- Functional Spec in SapDocument3 pagesFunctional Spec in Sapdeepu4200% (1)

- Open Source NetworkingDocument226 pagesOpen Source NetworkingyemenlinuxNo ratings yet

- PHP & OracleDocument23 pagesPHP & OraclebalaranjithNo ratings yet

- UM Assignment AC-DC ConversionDocument2 pagesUM Assignment AC-DC ConversionIndira KarimovaNo ratings yet

- Anti Textbook PyDocument74 pagesAnti Textbook PyStanciulescu CristianNo ratings yet

- Leveraging SAP On Azure For IT Transformation: A ZureDocument21 pagesLeveraging SAP On Azure For IT Transformation: A Zurehelder da costaNo ratings yet

- VITO Average Temperature TroubleshootingDocument5 pagesVITO Average Temperature TroubleshootingRobert RdzNo ratings yet

- AssessmentDocument1 pageAssessmentDipin Preet SinghNo ratings yet

- Development of an 89C51 Microcontroller BoardDocument13 pagesDevelopment of an 89C51 Microcontroller BoardSHAROON SARDAR GHULAMNo ratings yet

- Buffering DataDocument4 pagesBuffering DataLeonard-Tiberiu SandorNo ratings yet

- TraceDocument55 pagesTraceHafid EnnejjarNo ratings yet

- NE5532 - Nte778aDocument3 pagesNE5532 - Nte778adaneloNo ratings yet

- Positioning in 5G NR: A Look at The Technology and Related Test AspectsDocument72 pagesPositioning in 5G NR: A Look at The Technology and Related Test AspectsArindam ChakrabortyNo ratings yet

- PLCDocument23 pagesPLCNarendra ChaurasiaNo ratings yet

- The Intel 4004 Microprocessor: What Constituted Invention?: William AsprayDocument12 pagesThe Intel 4004 Microprocessor: What Constituted Invention?: William AsprayKokipro KokiproNo ratings yet

- Understanding PPTDocument6 pagesUnderstanding PPTAnkur KumarNo ratings yet

- 34 Atmel Atmega32a PDFDocument352 pages34 Atmel Atmega32a PDFMuhammad UsmanNo ratings yet

- LTE Understanding the Evolution to LTEDocument45 pagesLTE Understanding the Evolution to LTEsonuvikas775No ratings yet

- Presentation 2Document36 pagesPresentation 2sakshi singhalNo ratings yet

- Batlabs Motorola Programming PrimerDocument2 pagesBatlabs Motorola Programming Primerhjhelen1No ratings yet

- Capstone Project FormatDocument19 pagesCapstone Project FormatJerome EliosesNo ratings yet

- Parker Installationsanleitung PCM Modul Ep2 Ep3 MSG30 2902 INST EN 2019Document66 pagesParker Installationsanleitung PCM Modul Ep2 Ep3 MSG30 2902 INST EN 2019nime fuziNo ratings yet

- Mode Chassi TVDocument78 pagesMode Chassi TVkimos38100% (1)

- Logix 5000 Controllers Major, Minor, and I/O Faults: Programming ManualDocument55 pagesLogix 5000 Controllers Major, Minor, and I/O Faults: Programming ManualRicardoNo ratings yet

- LET410 HandoutsDocument286 pagesLET410 HandoutsYoussouf mNo ratings yet

- 4.tutorial 4 TransientDocument3 pages4.tutorial 4 TransientJaishuu ChoudharyNo ratings yet

- Circuit Cellar 354 2020-01Document84 pagesCircuit Cellar 354 2020-01romanNo ratings yet

- Lab4 Asd SadasDocument3 pagesLab4 Asd Sadas....No ratings yet

- Troy Landers - ResumeDocument2 pagesTroy Landers - ResumeJena RichterNo ratings yet

- McKinsey Cloud MattersDocument34 pagesMcKinsey Cloud Mattersjamieroad100% (3)