Professional Documents

Culture Documents

Practica 03

Uploaded by

Jesus Roca FernandezCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Practica 03

Uploaded by

Jesus Roca FernandezCopyright:

Available Formats

Grado en Ingeniera informtica Modalidad Virtual

FUNDAMENTOS DE COMPUTADORES

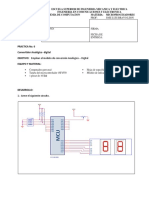

PRCTICA 3

PROGRAMACIN EN LENGUAJE ENSAMBLADOR (I)

OBJETIVOS:

Programacin en lenguaje ensamblador.

Instrucciones de transferencia y aritmticas

CONTENIDO:

1.

INTRODUCCIN

2.

ENUNCIADO.

3.

INFORME.

4.

ANEXO

PRCTICAS:

1.

PROGRAMA PARA EL ENTRENADOR.

1

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

REA DE TECNOLOGA ELECTRNICA

E.P.S. BURGOS

Grado en informtica

2

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

REA. TECNOLOGIA ELECTRNICA

E.P.S. BURGOS

Grado en Ingeniera informtica Modalidad Virtual

INTRODUCCIN:

En esta prctica se utilizarn Instrucciones de transferencia e Instrucciones

aritmticas del microprocesador 8085.

REGISTROS DEL 8085

REGISTRO A (ACUMULADOR).

Tiene 8 bits. Su salida est conectada a una de las

entradas a la ALU, y actua como uno de los

operandos en las operaciones de la misma.

REGISTROS B,C,D,E,H,L.

Estos seis registro de 8 bits se utilizan en

operaciones internas de la CPU. Pueden emparejarse

dos en dos formando registros de 16 bits: B (B-C),

D (D-E) Y M (H-L). Este ltimo par se utiliza sobre

todo para direccionar posiciones de memoria en las

instrucciones con referencia a memoria.

CONTADOR DE PROGRAMA (PC - PROGRAM COUNTER).

Registro de 16 bits. Contiene en todo momento la

direccin de la prxima instruccin a ejecutarse.

Se incrementa de forma secuencial excepto en las

instrucciones de salto.

PUNTERO DE PILA ( SP - STACK POINTER).

Registro de 16 bits que contiene la direccin de la

cima de la pila ( zona de memoria ). La pila se

gestiona como LIFO ( Last Input, First Output ).

REGISTRO DE ESTADO.

Registro de 8 bits. Se utilizan 5 de esos bits,

tambin llamados flags, para indicar la condicin

del resultado obtenido en la ALU.

FLAG

S: En operaciones con signo indica el signo del

resultado ( 0-positivo, 1-negativo )

Z: Flag 0. Si el resultado es 0, Z=1. En caso

contrario Z=0.

AC: Acarreo auxiliar. AC=1 cuando se

acarreo en los cuatro bits de menos peso.

produce

P: Flag de paridad. Indica la paridad

resultado. P=1 paridad par, P=0 paridad impar.

del

CY: Flag de acarreo o carry. CY=1 cuando se produce

acarreo en la operacin de la ALU con los bits de

mayor peso de cada operando.

3

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

REA DE TECNOLOGA ELECTRNICA

E.P.S. BURGOS

Grado en informtica

Las instrucciones de trasferencia se utilizan para mover los contenidos de la

memoria a los registros de la UCP, de los registros de la UCP a memoria y

entre los propios registros. No estn permitidas las trasferencias directas entre

dos posiciones de memoria.

Son:

MOV

MVI

LXI

LDA

STA

LHLD

SHLD

LDAX

STAX

XCHG

Las isntrucciones aritmticas son:

ADD

ADI

ADC

ACI

SUB

SUI

SBB

SBI

INR

DCR

INX

DCX

DAD

DAA

(Ver anexo)

Disponemos de la informacin sobre las instrucciones en las ayudas de los

distintos simuladores.

ENUNCIADO

Realizar un programa ensamblador que partiendo de dos

nmeros de 8 bits cada uno devuelva el primer dato en la

posicin 1200H, el segundo dato en 1201H, y en 1202H el

resultado de la suma ajustada en BCD.

4

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

REA. TECNOLOGIA ELECTRNICA

E.P.S. BURGOS

Grado en Ingeniera informtica Modalidad Virtual

Nota:

Introducir nmeros que no produzcan desbordamientos en hexadecimal.

2. INFORME

El informe de la prctica deber incluir los siguientes puntos:

Listado del Programa en ensamblador.

Organigrama.

Comentarios al programa.

5

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

REA DE TECNOLOGA ELECTRNICA

E.P.S. BURGOS

Grado en informtica

ANEXOS:

Tipo de

instruccin

Lectura /

escritura

de perifrico

Lectura

de memoria

Escritura

de memoria

Transferencia

de datos

Operaciones

aritmticas

Incremento

y

decremento

Salto

Instruccin

IN

OUT

puerto

puerto

LDA

LHLD

dir

dir

LDAX

MOV

POP

rp

r, M

rp

STA

SHLD

dir

dir

STAX

MOV

MVI

dato8

PUSH

rp

M, r

M,

rp

A +

A +

A +

A +

A +

A +

A BCD

A A A A A A HL +

JMP

CALL

RET

C

R

RST

vector

NINGUNO

BC, DE

A, B, C, D, E,

F, H, L

PSW, BC, DE, HL

BC, DE

A, B, C, D, E,

H, L

CY

Z

S

P

PC

=

=

=

=

NINGUNO

A, B, C, D, E,

H, L

A, B, C, D, E,

H, L

BC, DE, HL, SP

A, B, C, D, E, H, L

A, B, C, D, E, H, L

A, B, C, D, E,

H, L

BC, DE, HL ,SP

A, B, C, D, E,

H, L

BC, DE, HL, SP

BC, DE, HL, SP

/

/

/

/

TODOS

A, B, C, D, E, H, L

A, B, C, D, E,

H, L

1

1

0

1

NINGUNO

0

0

1

0

Z,

Z,

Z,

Z,

CY

S,. P, AC

S, P, AC

S, P, AC

S, P, AC

ninguno

ninguno

NINGUNO

3

3

1

1

1

1

1

2

1

REA. TECNOLOGIA ELECTRNICA

1

2

3

1

1

1

1

1

1

1

2

2

1

1

1

1

1

2

2

1

1

1

1

1

1

1

1

3

3

1

1

6

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

2

2

PSW, BC, DE, HL

M(HL) A

r

A

CY + M(HL) A

CY +

r

A

dato A

CY + dato A

A

M(HL) A

r

A

CY - M(HL) A

CY r

A

dato A

CY - dato A

rp HL

C

/ NC

Z

/ NZ

P

/ M

PE

/ PO

vector * 8

NINGUNO

salvo

para

POP PSW

Bytes

3

3

M(HL) + 1 M(HL)

r + 1 r

M(HL) - 1 M(HL)

r - 1 r

rp + 1 rp

rp - 1 rp

M

r

M

r

rp

rp

Indicadores

afectados

(puerto) A

A puerto

M(dir)

A

M(dir)

L

M(dir + 1)

H

M(rp)

A

M(HL)

r

M(SP)

rp L

M(SP+1)

rp H

SP+2

SP

A

M(dir)

L

M(dir)

H

M(dir + 1)

A

M(rp)

r

M(HL)

dato

M(HL)

M(SP-1)

rp H

M(SP-2)

rp L

SP-2

SP

r2

r1

dato r

dato rp

HL

PC

HL

SP

HL

DE

L

M(SP)

H

M(SP+1)

MOV

r1, r2

MVI

r,

dato8

LXI

rp,

dato16

PCHL

SPHL

XCHG

XTHL

ADD

M

ADD

r

ADC

M

ADC

r

ADI

dato8

ACI

dato8

DAA

SUB

M

SUB

r

SBB

M

SBB

r

SUI

dato8

SBI

dato8

DAD

rp

INR

INR

DCR

DCR

INX

DCX

Registro

designado

por r o rp

Operacin realizada

E.P.S. BURGOS

Grado en Ingeniera informtica Modalidad Virtual

ANA

ANA

ORA

ORA

XRA

XRA

ANI

ORI

XRI

CMP

CMP

CPI

CMA

CMC

STC

Funciones

lgicas

RLC

RAL

Instrucciones de

desplazamiento

RRC

RAR

EI

DI

Instrucciones

especiales

RIM

SIM

NOP

HLT

r, rs,

DDD SSS

rd

A

111

B

000

C

001

E

011

H

100

L

101

M(HL)

110

rp

B C

D E

H L

SP

RP

00

01

10

11

M

r

M

r

M

r

dato8

dato8

dato8

M

r

dato8

A

+

A

+

A

A

A +

A A A A

(CY)

1

A, B, C, D, E,

H, L

Indicadores

puestos a

cero:

A, B, C, D, E,

H, L

A, B, C, D, E,

H, L

CY

CY, AC

CY, AC

CY, AC

CY, AC

TODOS

A, B, C, D, E,

H, L

Ninguno

1

1

1

1

CY

1

1

1

1

1

1

NINGUNO

Parmetros para especificar registros y posiciones

de memoria con direccionamiento indirecto con

registros HL

Parmetros para especificar parejas de registros y

SP(todos de 16 bits)

CCC

Parmetros que identifican las

condiciones de bifurcacin

000

001

010

011

100

101

110

111

El cdigo 11 en las instrucciones PUSH y POP representa a PSW

7

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

1

1

1

1

1

1

2

2

2

1

1

2

1

1

1

CY

desp. izq. sin

CY

(en

el bucle)

desp. izq. con CY

(en

el bucle)

desp. der. sin

CY

(en

el bucle)

desp. der. con CY

(en

el bucle)

Habilitacin de

interrupciones

Inhabilitacin de

interrupciones

Lectura de la mscara

de interrup.

Escritura de la mscara

de interrup.

No operar

Parada del

microprocesador

Condicin ( X X )

NZ no cero ( Z = 0 )

Z cero ( Z = 1 )

NC no acarreo ( CY = 0 )

C acarreo ( CY = 1 )

PO paridad impar ( P = 0 )

PE

paridad par ( P = 1 )

P

positivo ( S = 0 )

M negativo ( S = 1 )

Nota:

M(HL) A

r

A

M(HL) A

r

A

M(HL) A

r

A

dato A

dato A

dato A

M(HL)

r

dato

A

CY

CY

REA DE TECNOLOGA ELECTRNICA

E.P.S. BURGOS

Grado en informtica

INST.

ACI

ADC A

ADC B

ADC C

ADC D

ADC E

ADC H

ADC L

ADC M

ADD A

ADD B

ADD C

ADD D

ADD E

ADD H

ADD L

ADD M

ADI

ANA A

ANA B

ANA C

ANA D

ANA E

ANA H

ANA L

ANA M

ANI

CALL

CC

CM

CMA

CMC

CMP A

CMP B

CMP C

CMP D

HEX INST.

CE

8F

88

89

8A

8B

8C

8D

8E

87

80

81

82

83

84

85

86

C6

A7

A0

A1

A2

A3

A4

A5

A6

E6

CD

DC

FC

2F

3F

BF

B8

B9

BA

CMP

CMP

CMP

CMP

CNC

CNZ

CP

CPE

CPI

CPO

CZ

DAA

DAD

DAD

DAD

DAD

DCR

DCR

DCR

DCR

DCR

DCR

DCR

DCR

DCX

DCX

DCX

DCX

DI

EI

HLT

IN

INR

INR

INR

INR

HEX INST.

E

H

L

B

D

H

SP

A

B

C

D

E

H

L

M

B

D

H

SP

A

B

C

D

BB

BC

BD

BE

D4

C4

F4

EC

FE

E4

CC

27

09

19

29

39

3D

05

0D

15

1D

25

2D

35

0B

1B

2B

3B

F3

FB

76

DB

3C

04

0C

14

INR E

INR H

INR L

INR M

INX B

INX D

INX H

INX SP

JC

JM

JMP

JNC

JNZ

JP

JPE

JPO

JZ

LDA

LDAX B

LDAX D

LHLD

LXI B

LXI D

LXI H

LXI SP

MOV A,A

MOV A,B

MOV A,C

MOV A,D

MOV A,E

MOV A,H

MOV A,L

MOV A,M

MOV B,A

MOV B,B

MOV B,C

HEX INST.

1C

24

2C

34

03

13

23

33

DA

FA

C3

D2

C2

F2

EA

E2

CA

3A

0A

1A

2A

01

11

21

31

7F

78

79

7A

7B

7C

7D

7E

47

40

41

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

B,D

B,E

B,H

B,L

B,M

C,A

C,B

C,C

C,D

C,E

C,H

C,L

C,M

D,A

D,B

D,C

D,D

D,E

D,H

D,L

D,M

E,A

E,B

E,C

E,D

E,E

E,H

E,L

E,M

H,A

H,B

H,C

H,D

H,E

H,H

H,L

HEX INST.

42

43

44

45

46

4F

48

49

4A

4B

4C

4D

4E

57

50

51

52

53

54

55

56

5F

58

59

5A

5B

5C

5D

5E

67

60

61

62

63

64

65

MOV H,M

MOV L,A

MOV L,B

MOV L,C

MOV L,D

MOV L,E

MOV L,H

MOV L,L

MOV L,M

MOV M,A

MOV M,B

MOV M,C

MOV M,D

MOV M,E

MOV M,H

MOV M,L

MVI A

MVI B

MVI C

MVI D

MVI E

MVI H

MVI L

MVI M

NOP

ORA A

ORA B

ORA C

ORA D

ORA E

ORA H

ORA L

ORA M

ORI

OUT

PCHL

HEX INST.

66

6F

68

69

6A

6B

6C

6D

6E

77

70

71

72

73

74

75

3E

06

0E

16

1E

26

2E

36

00

B7

B0

B1

B2

B3

B4

B5

B6

F6

D3

E9

POP B

POP D

POP H

POP PSW

PUSH B

PUSH D

PUSH H

PUSH PSW

RAL

RAR

RC

RET

RIM

RLC

RM

RNC

RNZ

RP

RPE

RPO

RRC

RST 0

RST 1

RST 2

RST 3

RST 4

RST 5

RST 6

RST 7

RZ

SBB A

SBB B

SBB C

SBB D

SBB E

SBB H

8

PRCTICAS DE FUNDAMENTOS DE COMPUTADORES

REA. TECNOLOGIA ELECTRNICA

E.P.S. BURGOS

HEX INST.

C1

D1

E1

F1

C5

D5

E5

F5

17

1F

D8

C9

20

07

F8

D0

C0

F0

E8

E0

0F

C7

CF

D7

DF

E7

EF

F7

FF

C8

9F

98

99

9A

9B

9C

SBB L

SBB M

SBI

SHLD

SIM

SPHL

STA

STAX B

STAX D

STC

SUB A

SUB B

SUB C

SUB D

SUB E

SUB H

SUB L

SUB M

SUI

XCHG

XRA A

XRA B

XRA C

XRA D

XRA E

XRA H

XRA L

XRA M

XRI

XTHL

HE

X

9D

9E

DE

22

30

F9

32

02

12

37

97

90

91

92

93

94

95

96

D6

EB

AF

A8

A9

AA

AB

AC

AD

AE

EE

E3

You might also like

- Usuarios y Grupos WindowsDocument4 pagesUsuarios y Grupos WindowsJesus Roca FernandezNo ratings yet

- Practica MVDocument2 pagesPractica MVJesus Roca FernandezNo ratings yet

- Practica MVDocument2 pagesPractica MVJesus Roca FernandezNo ratings yet

- Practica 02Document11 pagesPractica 02Jesus Roca FernandezNo ratings yet

- Practica 01Document18 pagesPractica 01Jesus Roca FernandezNo ratings yet

- Simulador de 8085Document63 pagesSimulador de 8085Juan Antonio100% (1)

- Practica 02Document11 pagesPractica 02Jesus Roca FernandezNo ratings yet

- Practica 01Document18 pagesPractica 01Jesus Roca FernandezNo ratings yet

- Elaboracion Manual Tecnico RubricaDocument2 pagesElaboracion Manual Tecnico RubricaLAURA VANESSA CONTRERAS GOMEZNo ratings yet

- Edan - F3 Con IUPDocument4 pagesEdan - F3 Con IUPLina MariaNo ratings yet

- Ensayo TuringDocument3 pagesEnsayo Turingnoslen reivaxNo ratings yet

- Triptico PDFDocument2 pagesTriptico PDFFabián RuízNo ratings yet

- Roles de QA en Poyectos AgilesDocument40 pagesRoles de QA en Poyectos AgilesDigital Harbor Bolivia100% (1)

- Políticas de Protección Contra Ataques InformáticosDocument1 pagePolíticas de Protección Contra Ataques InformáticosVanne Bedoya De GarciaNo ratings yet

- Investigación Ensambladores y DecompiladoresDocument1 pageInvestigación Ensambladores y DecompiladoresPatricio Lema G.No ratings yet

- Elementos Del SoftwareDocument14 pagesElementos Del SoftwareIvan RomeroNo ratings yet

- Catálogo de Piezas - OKI - MPS5501b - Página 1Document3 pagesCatálogo de Piezas - OKI - MPS5501b - Página 1emir pestanaNo ratings yet

- Balance de Carga Por SoftwareDocument7 pagesBalance de Carga Por SoftwareMadaleini Lizana cuevaNo ratings yet

- S04 PresentacionDocument23 pagesS04 PresentacionalicosakNo ratings yet

- Ejercicio Obligatorio - CSS 1 - Revisión Del IntentoDocument3 pagesEjercicio Obligatorio - CSS 1 - Revisión Del IntentoMorriganNo ratings yet

- Puntaje intento 62.5 de 125 preguntas programaciónDocument11 pagesPuntaje intento 62.5 de 125 preguntas programaciónAndres PinzonNo ratings yet

- IAS Ensayo 3 Estructuras lineales y recursividadDocument4 pagesIAS Ensayo 3 Estructuras lineales y recursividadBrandon EscareñoNo ratings yet

- Practica No. 6 ESIMEDocument5 pagesPractica No. 6 ESIMERaul ChavezNo ratings yet

- PROV-FP-CM-002 (Ficha de Diseño y Fabricación de Tableros)Document2 pagesPROV-FP-CM-002 (Ficha de Diseño y Fabricación de Tableros)Enrique Renzo Ascencio PachecoNo ratings yet

- Características de la capa de transporte OSIDocument17 pagesCaracterísticas de la capa de transporte OSIDanMasNo ratings yet

- Que Es Una Libreria en Arduino - POODocument5 pagesQue Es Una Libreria en Arduino - POOErick Martinez GámezNo ratings yet

- Algoritmos de Búsqueda en GrafosDocument12 pagesAlgoritmos de Búsqueda en Grafosrodrigo.a.arceNo ratings yet

- Modo de Uso Del ToraDocument14 pagesModo de Uso Del ToraPatricia Janett Inocente MorenoNo ratings yet

- cc302 Modulo2bDocument30 pagescc302 Modulo2bGonzalo InnNo ratings yet

- 2.4.11 Packet Tracer - Modify Single-Area OSPFv2Document5 pages2.4.11 Packet Tracer - Modify Single-Area OSPFv2Renato Tomas Davila MayorgaNo ratings yet

- TECSF - Ajustes de InventarioDocument6 pagesTECSF - Ajustes de InventarioCristobalArayaNo ratings yet

- Universidad San Francisco de Quito UsfqDocument46 pagesUniversidad San Francisco de Quito UsfqallahisgreatNo ratings yet

- Tarea 1 - PLE, Modelos de Transportes y AsignaciónDocument33 pagesTarea 1 - PLE, Modelos de Transportes y AsignaciónLedherzon ContrerasNo ratings yet

- Tarea 5 - Codigos de Caracteres y Detección de Errores - Revisión Del IntentoDocument3 pagesTarea 5 - Codigos de Caracteres y Detección de Errores - Revisión Del IntentoDavid CandelarioNo ratings yet

- JF 5 ProjectSolution EspDocument11 pagesJF 5 ProjectSolution EspSanders VazquezNo ratings yet

- Instalación de Jitsi en DockerDocument5 pagesInstalación de Jitsi en DockerMariana DávilaNo ratings yet

- Brochure-Linux Compressed PDFDocument7 pagesBrochure-Linux Compressed PDFCarla MariaNo ratings yet

- Materiales para MastilesDocument3 pagesMateriales para Mastilesgerman9224No ratings yet