Professional Documents

Culture Documents

A Fast and Efficient Method For Frequency Deviation Measurement Based On Genetic Algorithms Using A FPGA Approach

Uploaded by

Italo ChiarellaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Fast and Efficient Method For Frequency Deviation Measurement Based On Genetic Algorithms Using A FPGA Approach

Uploaded by

Italo ChiarellaCopyright:

Available Formats

1

2006 IEEE PES Transmission and Distribution Conference and Exposition Latin America, Venezuela

A Fast and Efficient Method for Frequency

Deviation Measurement Based on Genetic

Algorithms using a FPGA Approach

A. C. B. Delbem1, E. V. Simes1, B. F. Souza1, M. Oleskovicz 2, S. A. Souza,2

and D. V. Coury 2, Member, IEEE

Abstract - The main objetive of this research is to present a

fast and efficient method based on Genetic Algorithms (GAs) for

measuring the frequency deviation as well as the voltage

magnitude and phase angle of a noisy sinusoid wave. The

situation was formulated as an optimization problem, and the

goal was to minimize the estimation error. The use of GAs has

the advantage of better immunity against noise disturbance

present in the input data. In addition, this work also investigates

the implementation of such a scheme in FPGA (FieldProgrammable Gate Array). It is expected that the new approach

is able to accurately estimate the frequency, voltage magnitude

and phase angle, simulating an on-line frequency relay.

The inicial performance suggests that the proposed

Index Terms Frequency relay, Genetic algorithms, FPGA.

I. INTRODUCTION

N a power system, the correct evaluation of the frequency is

an important task. Some good examples of application are

in power system relaying, power-quality monitoring and

operation as well as control of devices using digital

technologies.

The typical use of frequency estimation in power system is

for protection schemes against loss of synchronism [1], underand-over frequency relaying and for power system

stabilization [2]. Generally, frequency relays are used in

power system to protect the generating units. In addition to

provide complete primary and back up protection. The

The authors acknowledge the Department of Electrical Engineering

Engineering, School of Engineering of So Carlos and Department of

Mathematics and Computer Science, University of So Paulo (Brazil), for the

research facilities provided to conduct this project. This work was supported

by CNPq Conselho Nacional de Desenvolvimento Cientfico e Tecnolgico,

FAPESP - Fundao de Amparo Pesquisa do Estado de So Paulo and

CAPES Coordenao de Aperfeioamento de Pessoal de Nvel Superior.

The authors A. C. B, Delbem1, E. V. Simes1 and B. F. Souza1 are with

Department of Mathematics and Computer Science, University of So Paulo,

SP, Brazil (e-mails: {acdb, bferes, simes}@icmc.usp.br).

The authors M. Oleskovicz2, S. A. Souza2 and D. V. Coury2 are with

Department of Electrical Engineering Engineering School of So Carlos,

University of So Paulo, SP, Brazil (e-mails: {olesk, silvios,

coury}@sel.eesc.usp.br).

1-4244-0288-3/06/$20.00 2006 IEEE

performance of these relays, however, depends primarily on

the accuracy of the frequency and voltage magnitude

measurements.

Some solutions have been suggested utilizing signal

processing for the estimation problem. The applications can be

categorized based on their time demand, that is: critical real

time application, such as the mentioned relay protection; online data monitoring in control room and off-line data analysis

from computer recordings. The classification is useful since

the different time demands imply in restrictions on what type

of frequency estimator and filter technique that can be used.

In general, the available frequency estimation techniques

use digitized samples of the system voltage. Considering the

power system voltage waveforms as purely sinusoidal, the

time between two zero crossings is an indication of system

frequency. However, in reality, the measured signals are

available in a distorted form and this can be a problem for the

frequency estimation. Discrete Fourier transform, Least Error

Square, Kalman filtering, orthogonal finite-impulse-response

(FIR) filtering, and iterative approaches [3]-[10] are some of

the important techniques in this area. Soft computing

techniques, such as Artificial Neural Network (ANN) [11] and

Genetic Algorithms (GAs) [12] are also utilized for power

frequency measurement.

This research presents a fast and efficient method based on

GAs for measuring the frequency deviation as well as the

voltage magnitude and phase angle of a sinusoid wave. In this

approach, the problem is formulated as an optimization

problem. The goal is to minimize the estimation error utilizing

Gas, which have the advantage of having immunity against

noise disturbance. However, it should be pointed out that one

of the main objectives of this study is to investigate if the

proposed GA approach for FPGA (Field-Programmable Gate

Array) is able to accurately estimate the frequency, voltage

magnitude and phase angle of a system. The performance of

the proposed estimator is judged though numerous examples

and the results obtained show that the technique estimates the

waveform parameters with high degree of accuracy.

II. BASIC CONCEPTS RELATED TO THE GENETIC ALGORITHMS

A genetic algorithm (GA) is a search algorithm based on

the mechanism of natural selection and natural genetics. Its

fundamental principle is the fittest member of a population

has highest probability for survival. A GA operates on a

population of current approximations the individuals

initially drawn at random, from which improvement is sought.

Individuals are encoded as strings the chromosomes so

that its values represent a possible solution for a given

optimization problem [13].

There is a fitness value associated to each chromosome.

The better the solution the chromosome represents the larger

its fitness its chances to survive and produce offspring, such

as the role of environment. In this context, the objective

function establishes the basis of selection. At the reproduction

stage, a fitness value is derived from the raw individual

performance measure as given by the objective function, as is

used to bias the selection process. The selected individuals are

then modified using genetic operators. After this, individual

chromosomes are decoded, evaluated, and selected according

to their fitness, and the process continues for different

generations. By manipulating simultaneously a population of

possible solutions, the GAs can explore several areas of the

search space.

The GAs relies on two basic kinds of operators: genetic

and evolutionary: Genetic operators, namely crossover and

mutation, are responsible for establishing how individuals will

exchange or simply change their genetic features in order to

produce new individuals. Evolutionary operators deal with

determining which individuals will suffer crossover or

mutation.

Essentially, a GA tries to minimize or maximize the value

presumed by the fitness function. In many cases, the

development of a fitness function can be based on this return

and can represent only a partial evaluation of the problem.

Additionally, the algorithm must be fast, because it will

analyze each individual from a population and its successive

generations.

III. FPGA A SYSTEM-ON-CHIP-SOLUTION

Specialized hardware poses as an attractive solution to cope

with the necessary real-time constrains of modern

applications. FPGAs (Field-Programmable Gate Arrays) are a

flexible alternative to implement complex models, since

hardware functionality can be changed according to the task to

be executed [14]. However, designing and programming such

a specialized hardware can still be very complex, leading to

project delays. This has motivated many authors to propose

frameworks for the design of reconfigurable solutions on

FPGA. Amongst them, Alteras Excalibur System with the

NIOS Soft Core Embedded Processor [15] has been chosen as

the system platform. The proposed solution makes use of the

System-On-Chip (SOC) concept [16] with high-level system

integration.

Thompson [17]-[20] took the first steps towards bridging

the gap between computer models of Evolutionary Algorithms

(EAs) and physical reality. In his work, he applied EAs to

FPGAs and showed how to automatically produce useful

circuits by evolution. Soon after, many authors followed [21][23]. Nevertheless, all these authors lack parallelism or

independence from external computation, or both. With the

advances on FPGA techniques in the last decade, mainly in

capacity and speed of the logic cell arrays, it became possible

to implement sophisticated full-parallel versions of EAs in

hardware, without the necessity of a processor (external or

internal). Still, Thompson deserves credit for describing the

first experiments with the Embedded Evolution (EE) concept.

EE is a methodology for the design of evolutionary

hardware that coexists with the control system that it is trying

to optimize inside a single chip (SOC solution). It avoids the

problems of evolving in simulation and transferring the design

to physical chips and speeds up evolution by exploring the

intrinsic parallelism of the FPGA logic cell arrays, such as

evaluating each EA individual in parallel. The evolutionary

algorithm is conceived in a way to explore parallelism, having

its main functions distributed among and embedded within the

FPGA logic cells, so that there is no need for human

intervention to evaluate, select, breed, or reconfigure the

evolving population. Fitness evaluation, partner selection, and

reproduction can be carried out autonomously and in parallel

by the embedded evolutionary system. The system hardware is

not only autonomous in their application-specific control

circuit, but in the evolutionary algorithm as well.

When designing evolutionary systems for parallel

hardware, it is not always clear how the evolutionary

functions (e.g., selection, crossover, mutation, etc.) should be

decomposed and the sub-systems often include interactions

mediated via very long interconnection lines. Another major

problem is that the interactions among sub-parts tend to grow

exponentially as the systems become more concurrent. When

the complexity of the interactions grows, a primary

decomposition of the design becomes difficult to obtain. An

alternative to this is to allow evolution to deal with the

unexpected interactions between sub-systems and design a

controller based on the behavior of the complete system (i.e.,

seeing the controller as a whole and measuring only behavior

performance).

A noticeable disadvantage of EE is that it is difficult to

collect experimental data from the chip. Nevertheless, it is

possible in many cases to include memory and processor

hardware in the system, so that the evolutionary process can

be monitored and data can be transferred to an external

computer to be analyzed. EE adds even more difficulty to the

inherent real-time hardware problem of replicating entire

experiments. Noise in the sampled signals and the

environment may result in a large variance across trials. This

uncertainty is also difficult to reproduce in simulation, even

by preserving the same random seeds, but it is practically

impossible in a physical controller, embedded within a real

integrated circuit. Any stochastic components in the algorithm

compound the problem. In simulated evolution, the

programmer can manipulate the rules to eliminate nondeterminism and produce repeatable trials.

In EE, evolution is manipulating a physical object that

exists in real-time and space, and behaves according to the

physics of the electronic circuit. Evolution should be able to

exploit freely the collective behavior of the components of the

control circuit without the necessity of predicting it from

knowledge of their individual properties. It can take advantage

of the rich structures and dynamical behaviors that are natural

to the FPGA hardware, far beyond the scope of conventional

design, which is only a sub-set of the possibilities. Even

stochastic noise is not always a problem and can present

advantageous effects. However, it alters the behavior of the

control circuit hardware, modifying fitness and obscuring the

fitness landscape. This effect decreases the difference in

fitness between two individuals that are neighbors in genotype

space and may lead to imprecision in selecting the fittest

robot.

The design of a fitness function in EE is more difficult than

in simulation, because not all sensory information taken by

simulation is actually available from the point of view of the

integrated circuit in the real world. Towards the end of the

evolutionary experiment, the differences between individual

fitness become smaller, resulting in a less effective selection.

In EE, a possible alternative is to increase the duration of a

generation at the end of the experiment, to introduce more

selection pressure in the environment and differentiate the

better-adapted individuals.

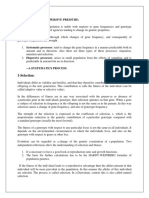

A graphical representation of chromosome is given by Fig.

1.

Fig. 1. Chromosome representation

B. Selection

The selection process is concerned about stochastically

choosing individuals for reproduction. As a rule of thumb, it

emphasizes the best solutions in the current population. Here,

the selection is carried out by the well-known tournament

operator [13]. This operator has been reported to give

adequate results for several application domains and can be

easily implemented in FPGA [24]. Moreover, this selection

strategy has presented superior performance than the roulette

wheel operator.

C. Crossover

Crossover is a genetic operator used to guide the

evolutionary process through potentially better solutions. This

operator interchanges genetic material of different

chromosomes in order to create individuals that can benefit

from their parents fitness. The crossover of the proposed GA

follows a general approach, similar to the blend crossover for

real numbers [25],[26]. Consider 2 individuals, xit and x tj

(where t indicates the generation), chosen by the selection

process. For each of their 3 genes, which are written as x.t , a

truncated value t =

xit + x tj

is calculated. With this value, 3

2

new points can be generated, as showed in Fig. 2. Parents are

marked with empty circles.

IV. PROPOSED GA FOR FPGAS

A. Encoding

The proposed GA employes a binary-code scheme for

representation of the parameters Vm (amplitude), f (frequency)

and (phase angle). A chromosome has three sequences of

bits representing three integer numbers. The first number is an

index for the value of Vm, the second number is an index for f

and the third is an index for . Table I shows the number of

bits used to encode each parameter, the integer values they can

assume in the chromosome and the corresponding real value.

Fig. 2. Crossover operator

The offspring is created by randomly choosing one of the 5

points represented in Fig. 2 for each gene. For example, the

first gene of the new individual xk can be any x1i 1 , x1j ,

TABLE I

PARAMETERS ENCODING

Parameter

Vm

f

No of bits

8

8

9

Integer range

[0, 255]

[0, 255]

[0, 511]

x1i + 1 , x1j or x1j + 1 . An exception for that is when a given

Real range

[2.5, 12.5]

[58.0, 62.0]

[0, 2]

gene have the same value for the 2 parents, making 1 = 0 . In

this case, xkt is randomly chosen between xit / and xit * ,

where is a user defined parameter (here, = 2 ). If xkt is

out of the range [ xkmin , xkmax ] , it is set to the bordery values.

D. Mutation

Mutation is the genetic operator responsible for generation

of solution diversity in the population [27]. It works

producing alteration of a gene value independently from the

gene value of its parent. The proposed mutation operator adds

1 to (subtracts 1 from) each gene x.t of the chromosome

according to a mutation rate. If x.t is out of the range

[ x.min , x.max ] , it is set to the bordery values.

where m indicates the number of discretization points used for

f, as showed in Table 1, and n is the number of points sampled

of the waveform signal. As, in this work, a sampling

frequency of 800Hz and half cycle were considered, n = 7.

After calculating matrix in Fig. 3, one can easily retrieve a

number Index f *ti + , indicating the index of one of its

elements. This index is used to construct matrix

sin( Index f *ti + ) (Fig. 4) of dimension mnxl, where l is the

number of discretization points used for

Table 1. The values of the elements

E. Fitness

The fitness function is used to evaluate a solution of a

problem. Different fitness functions can produce very

different GA performances for the problem. Moreover, the

fitness evalutation may require large running time depending

on the employed fitness function. For frequency-relaying

estimation, EL-Naggar and Youssef [12] have proposed two

types of fitness functions: one is based on the sum of the

errors in the equation and the other on the maximum

individual error. Based on experimentation, they concluded

that, in most cases, the maximum function outperformed the

sum one. Thus, in this work, the authors use the maximum

function. Furthermore, it requires fewer operations than the

sum function to be calculated and it is, therefore, more

suitably implemented in FPGAs. Formally, the fitness

function (FF) considered here is given by (1):

b.,. are mapped into the

discretized vector of the sine function, as showed in Table 1.

It has p = 1024 points in [-1, 1].

Finally, matrix in Fig. 5 computes S ' (c f , cv m , c , ti ) . It has

dimension oxp, where o is the number of discretization points

used for Vm, as showed in Table 1, and p is the number of

points used to discretize the sine function. Fig. 6 shows a

graphical representation of the sine vector. The function

S ' (c f , cv m , c , ti ) itself was discretized, using q = 4096

points in [-12.5, 12.5], which is the range it can assume, given

the considered values of Vm. Thus the elements of matrix in

Fig. 5 are mapped to the S'() vector of Fig. 6.

FF (c) = max | S ( f , V m , , t i ) S ' (c f , c v m , c , t i ) (1)

i =0,..., n

where c represents an individual of the population, n is the

number of points ( t i ) and S ( f , V m , , t i ) is the original

FIG. 3. MATRIX

f * ti

signal calculated over the point ( t i ) and S ' (c f , c v m , c , t i )

is the signal calculated over ( t i ) using the parameters f, Vm

and

codified in the chromosome c. It is important to notice

that both S() and S() are discretized, as explained at next

section .

F. Memory Organization

In order to largely reduce running time for evalutation of the

fitness function, mathematical calculations like multiplication

and sine operations are computed a priori on a workstation.

The results were stored in a tabular manner, such that they can

be easely configured into the FPGA. Fig. 3-6 summarize the

memory organization of the FPGA.

Consider the expanded form of S ' (c f , cv m , c , t i ) in (1):

S ' (c f , c v m , c , t i ) = c v m * sin( 2c f t i + c )

FIG. 4. MATRIX

Fig. 5. Matrix

sin( Index f *ti + )

S ' (c f , cv m , c , t i )

(2)

The computation of (2) can be splitted into two steps: first,

the sine function argument should be calculated and next the

multiplication between amplitude and sine takes place. Matrix

3 (Fig. 3) stores the product f * t i . It has dimension mxn,

as showed in

Fig. 6. Sine and S() vectors

V. EXPERIMENTAL RESULTS

The main objective of this work is to investigate if the

proposed GA approach for FPGA is able to accurately

estimate the voltage frequency, magnitude and phase angle of

a noisy waveform. The experiments consist in generating a

digitalized sine waveform, with 1 % noise and different

amplitude values, phase angles and frequencies to test the

algorithm. The various values considered are shown in Table

2. Based on another study [28], the authors used a data

window size of 0.5 cycle and a sampling frequency of 800 Hz.

The time reference is considered at the beginning of the data

window.

In all experiments, the GA have the following parameters:

population of 30 individuals, runs of 300 generations,

crossover probability of 1, mutation rate of 20%. As GAs are

stochastic methods, there are no guarantees that the same

results will be encountered in different runs. Thus, the results

of the proposed method are averaged over 1000 trials.

Fig. 8 shows the percentage errors for estimation of the

three parameters for several frequency values. For all the

parameters, the estimation provides relative errors smaller

than 1.4%.

TABLE II

PARAMETERS USED FOR TESTS WITH THE PROPOSED GA

Parameter

Amplitude (Vm)

Frequency (f)

Phase ()

Values range considered

[2.5, 12.5] with steps of 2.5 V

[58.0, 62.0] with steps of 0.5 Hz

[0, 360] with steps of 30o

The proposed GA was evaluated for more than 500 different

test cases. In the following, a subset of the obtained results are

highlighted. The experiments are based on a sine waveform

with 60Hz and 0o. They provide estimation results involving

effects of variation on amplitude, frequency and phase. The

test cases were generated considering the values range as

shown in Table 2.

Fig. 7 shows the percentage errors for estimation of the

three parameters for the tested cases with different values of

amplitude. The GA was very accurate in estimating the

frequency and the amplitude of the waves. The relative errors

were smaller than 0.7%. It also works properly for the phase

estimation. It shows a maximal relative error of 1.1% for this

case.

Fig. 8. Relative errors (%) when varying frequency (f)

Fig. 9 shows the percentage errors for estimation of the

three parameters when phase angle varies. The relative errors

obtained are in general bigger for this set of tested cases. The

maximum error on estimating the phase angle was around 30o.

For these cases, the relative error was about 1.80%.

Nevertheless, the obtained results for this set of tested cases

are also adequate.

Fig. 9. Relative errors (%) when varying phase

VI. CONCLUSIONS

Fig. 7. Relative errors (%) when varying Vm amplitude

This work presented a method based on Genetic Algorithms

(GAs) for measuring the frequency deviation as well as the

voltage magnitude and phase angle for a sinusoid wave.

Moreover, one of the main objectives of this work is to

investigate if the proposed GA could be implemented in

FPGA (Field-Programmable Gate Array) simulating an online frequency relay with advantages if compared to the

conventional one.

The inicial performance presented high performance both in

the implementation point of view as well as high precision on

the estimations realized. It suggests that the proposed

methodoloy could provide an efficient alternative for

frequency relays.

VII. REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

[18]

P. Denys, C. Counan, L. Hossenlopp, and C. Holweck. Measurement of

voltage phase for the French future defense plan against losses of

synchronism. IEEE Transactions on Power Delivery, vol. 7, no. 1, pp.

62-69, Jan., 1992.

V. Eckhardt, P. Hippe, and G. Hosemann. Dynamic Measuring of

frequency and frequency oscillations in multiphase power systems.

IEEE Transactions on Power Delivery, vol. 4, no. 1, pp. 95-102, Jan.,

1989.

A. G. Phadke, J. Thorp, and M. Adamiak. A new measurement

technique for tracking voltage phasors, local system frequency and rate

of change of frequency. IEEE Trans. Power Apparatus Syst., vol. PAS102, no. 5, pp. 1025-1038, 1983.

M. S. Sachdev and M. M. Giray. A least square technique for

determining power system frequency. IEEE Trans. Power Apparatus

System., vol. PAS-104, no. 2, pp. 437-443, 1985.

V. Terzija and M. Djuric. A numerical algorithm for direct real-time

estimation of voltage phasor, frequency and its rate of change. Electr.

Mach. Power System., vol. 24, pp. 417-428, 1996.

A. A. Girgis and T. L. Hwang. Optimal estimation of voltage phasors

and frequency deviation using linear and nonlinear Kalman filtering.

IEEE Trans. Power Apparatus System., vol. PAS-103, no. 10, pp. 29432944, 1984.

T. S. Sidhu and M. S. Sachdev. An iterative technique for fast and

accurate measurement of power system frequency. IEEE Transactions

on Power Delivery, vol. 13, no. 1, pp. 109-115, Jan., 1998.

P. K. Dash, A. K. Pradhan, and G. Panda. Frequency estimation of

distorted power system signals using extended complex Kalman filter.

IEEE Transactions on Power Delivery, vol. 14, no. 3, pp. 761-766, Jul.,

1999.

M. Akke. Frequency estimation by demodulation of two complex

signals. IEEE Transactions on Power Delivery, vol. 12, no. 1, pp. 157163, Jan., 1997.

A. K. Pradhan, A. Routray, and A. Basak. Power system frequency

estimation using mean square technique. IEEE Transactions on Power

Delivery, vol. 20, no. 3, Jul., 2005.

L. L. Lai, W. L. Tse, C. T. Chan, and A. T. P. So. Real-time frequency

and harmonic evaluation using artificial neural networks. IEEE

Transactions on Power Delivery, vol. 14, no. 1, pp. 52-59, Jan., 1999.

K. M. El-Naggar and H. K. M. Youssed. A genetic based algorithm for

frequency-relaying applications. Electric Power Systems Research, vol.

55, pp. 173-178, 2000.

D. Goldberg. Genetic algorithms in search, in: Optimization and

Machine Learning. Addison-Wesely, Longman Publishing, Boston,

MA, 1989.

J. V. Oldfield. Field-programmable gate arrays: reconfigurable logic for

rapid prototyping and implementation of digital systems. John Wiley &

Sons, Inc., 1995.

Stratix

Altera.

Nios

development

kit.

edition.http://www.altera.com/products/devkits/altera/kit-nios1S10.html,

2004.

A. Habibi and S. Tahar, S. A survey on system-on-a-chip design

languages. In The 3rd IEEE International Workshop on System-onChip for Real-Time Applications, pages 212215, Calgary, Alberta,

Canada, 2003.

A. Thompson. Evolving Fault-Tolerant Systems. Report ID: Cognitive

Science Research Paper Serial N. CSRP 385, The University of Sussex

School of Cognitive and Computing Sciences, Falmer Brighton, BN1

9QH, England, UK, 6p., 1994.

A. Thompson. Real Time for Real Power: Methods of Evolving

Hardware to Control Autonomous Mobile Robots. Report ID:

Cognitive Science Research Paper Serial N. CSRP 350, The University

of Sussex School of Cognitive and Computing Sciences, Falmer

Brighton, BN1 9QH, England, UK, 6p., 1994.

[19] A. Thompson. Evolutionary Techniques for Fault Tolerance.

Proceedings of the UKACC International Conference on Control CONTROL'96 (IEE Conference Publication no.427), pp. 693-698, 1996.

[20] A. Thompson. An Evolved Circuit, Intrinsic in Silicon, Entwined With

Physics. Proceedings of the First International Conference on

Evolvable Systems: From Biology to Hardware - ICES96, Oct. 7-8,

1996, Tsukuba, Japan, Higuchi, T. and Iwata, M. (Eds.), Publisher:

Springer-Verlag LNCS, pp. 390-405, 1996.

[21] A. Thompson and P. Layzell. Analysis of Unconventional Evolved

Electronics. In Communications of the Association of Computing

Machinery, v. 42, n. 4, Yao, X. (Ed.), pp. 71-79, 1999.

[22] A. Thompson and P. Layzell. Evolution of Robustness in an Electronics

Design. Proceedings of the 3rd International Conference on Evolvable

Systems - ICES 2000, Publisher: Springer Verlag, pp. 218-228, 2000.

[23] A. Thompson, I. Harvey, and P. Husbands. Unconstrained Evolution

and Hard Consequences. Report ID: Cognitive Science Research Paper

Serial no. CSRP 397, The University of Sussex School of Cognitive and

Computing Sciences, Falmer Brighton, BN1 9QH, England, UK, 31p.,

1994.

[24] T. Back, D. B. Fogel, and Z. Michalewicz. Handbook of Evolutionary

Computation. IOP Publishing Ltd., Bristol, UK, 1997.

[25] K. Deb, and D. Kalyanmoy, D. Multi-Objective Optima Optimization

Using Evolutionary Algorithms. John Wiley & Sons, Inc., 2001.

[26] A. H. Wright. Genetic Algorithms for Real Parameter Optimization. In

Rawlins, G. J., editor, Foundations of Genetic Algorithms, pages 205

218. Morgan Kaufmann, San Mateo, CA, 1991.

[27] D. Whitley. A Genetic Algorithm Tutorial. Statistics and Computing,

4:6585, 1994.

[28] E. T. Vargas. Application of GAs in Frequency Digital Relays. 146p,

Master Dissertation. Universidade de So Paulo, So Carlos, SP, 2005.

VIII. BIOGRAPHIES

Alexandre C. B. Delbem received the Ph.D. degree from the University of

So Paulo, So Paulo, Brazil, in 2002. He became Assistant Professor with the

University of So Paulo in 2003. His main research interests are network

design problems, graph data structures, evolutionary computation and

bioinformatics.

Eduardo V. Simes received the Ph.D. degree from the University of Kent at

Canterbury, UKC, England, in 2001. He became Assistant Professor with the

University of So Paulo in 2003. His main research interests are network

design problems, dynamically reconfigurable computing (FPGAs),

evolutionary controllers and bioinformatics.

Bruno F. Souza is currently a Ph.D. Student at the Computer Science

Department of Institute if Mathematics and Computer Science, University of

So Paulo. His main interests include bioinspired approaches to deal with

practical

questions. Recently, he has been involved with Power System Protection

and Power Quality problems and bioinformatics.

Mrio Oleskovicz is currently a lecturer at the Electrical Engineering Dept.,

University of So Paulo. His field of interests includes techniques for Power

Systems Control and Protection, Power Quality, including the use of Genetic

Algorithms and Artificial Neural Network.

Silvio A. de Souza is currently a Ph.D. student at Electrical Engineering Dept.

in EESC, University of So Paulo. His main interests are Power System

Analysis, Power System Protection and Power Quality, including the use of

Genetic Algorithms.

Denis V. Coury is presently a Full Professor in the Power System Group at

the Department of Electrical Engineering, University of So Paulo. His areas

of research interest are Power System Protection as well as techniques for

Power Systems Control and Protection, Power Quality, including the use of

Genetic Algorithms and Artificial Neural Network.

You might also like

- Natural History of Ashkenazi IntelligenceDocument36 pagesNatural History of Ashkenazi IntelligenceMagnus Strömgren100% (1)

- Evolutionary Biology Ideology Then and NowDocument20 pagesEvolutionary Biology Ideology Then and Nowzpervan1No ratings yet

- Summary Notes - Topic 5 Energy Flow, Ecosystems and The Environment - Edexcel (IAL) Biology A-Level PDFDocument9 pagesSummary Notes - Topic 5 Energy Flow, Ecosystems and The Environment - Edexcel (IAL) Biology A-Level PDFsammam mahdi samiNo ratings yet

- GENBIO2 MOD6 Evolutionary-Thoughts.Document21 pagesGENBIO2 MOD6 Evolutionary-Thoughts.Kris LaglivaNo ratings yet

- (Peter Leow) Genetic Algorithms Demystified UnravDocument58 pages(Peter Leow) Genetic Algorithms Demystified Unravasdsad123mNo ratings yet

- Structural Optimization Using Evolutionary Algorithms PDFDocument19 pagesStructural Optimization Using Evolutionary Algorithms PDFAyad SlabyNo ratings yet

- DLP Grade 10 Theories of EvolutionDocument5 pagesDLP Grade 10 Theories of EvolutionJoy MonteroNo ratings yet

- ... Systematic or Dispersive PressureDocument12 pages... Systematic or Dispersive PressureNomi Altaf58% (12)

- Plant BreedingDocument364 pagesPlant BreedingElizabeth Peña Reyes100% (4)

- 1996 The Natural Way To Evolve HardwareDocument4 pages1996 The Natural Way To Evolve HardwareZxNo ratings yet

- Digital Signal ProcessingDocument8 pagesDigital Signal Processingdebd1989No ratings yet

- 1996 Unconstrained Evolution and Hard ConsequencesDocument31 pages1996 Unconstrained Evolution and Hard ConsequencesZxNo ratings yet

- Asoodeh2015 Article NMRParametersDeterminationThroDocument26 pagesAsoodeh2015 Article NMRParametersDeterminationThroFarooq ArshadNo ratings yet

- SPE-176468-MS A Self-Adaptive Surrogate-Assisted Evolutionary Algorithm For Well Placement Optimization ProblemsDocument16 pagesSPE-176468-MS A Self-Adaptive Surrogate-Assisted Evolutionary Algorithm For Well Placement Optimization ProblemsMarcos SilvaNo ratings yet

- Applied Sciences: An Optimized Brain-Based Algorithm For Classifying Parkinson's DiseaseDocument16 pagesApplied Sciences: An Optimized Brain-Based Algorithm For Classifying Parkinson's Diseaseultimatekp144No ratings yet

- Bretas A.S. Artificial Neural Networks in Power System RestorationDocument6 pagesBretas A.S. Artificial Neural Networks in Power System RestorationNibedita ChatterjeeNo ratings yet

- Self-Optimized Routing Protocol For Wireless Sensor NetworksDocument4 pagesSelf-Optimized Routing Protocol For Wireless Sensor NetworksvinoaspsNo ratings yet

- Ant Algorithm For Grid Scheduling Problem: Abstract. Grid Computing Is A Form of Distributed Computing That inDocument8 pagesAnt Algorithm For Grid Scheduling Problem: Abstract. Grid Computing Is A Form of Distributed Computing That inEngr Safiyan Abubakar GizaNo ratings yet

- Ieee Research Papers On Genetic AlgorithmDocument6 pagesIeee Research Papers On Genetic Algorithmliwas0didov3100% (1)

- Reconfigurable Architectures For Bio-Sequence Database Scanning On FpgasDocument5 pagesReconfigurable Architectures For Bio-Sequence Database Scanning On Fpgasfer6669993No ratings yet

- I A G A (GA) O P F (OPF) P: Mplementation and Nalysis of Enetic Lgorithms To The Ptimal Ower LOW RoblemDocument19 pagesI A G A (GA) O P F (OPF) P: Mplementation and Nalysis of Enetic Lgorithms To The Ptimal Ower LOW RoblemDalessandroNo ratings yet

- Optimum Coordination of Overcurrent Relays Using SADE AlgorithmDocument10 pagesOptimum Coordination of Overcurrent Relays Using SADE AlgorithmJamile_P_NNo ratings yet

- The International Journal of Engineering and Science (The IJES)Document7 pagesThe International Journal of Engineering and Science (The IJES)theijesNo ratings yet

- A Hybrid Algorithm Based On KFCM-HACO-FAPSO For Clustering ECG BeatDocument6 pagesA Hybrid Algorithm Based On KFCM-HACO-FAPSO For Clustering ECG BeatInternational Organization of Scientific Research (IOSR)No ratings yet

- Genetic Programming For Moment Capacity Modeling of FerrocementDocument8 pagesGenetic Programming For Moment Capacity Modeling of FerrocementWilliam CaballeroNo ratings yet

- Evolutionary Programming Optimization Technique FoDocument7 pagesEvolutionary Programming Optimization Technique FoJean Baptiste nkongoloNo ratings yet

- Application of Improved Genetic Algorithm in Ultrasonic Locationof Transformer Partial DischargeDocument10 pagesApplication of Improved Genetic Algorithm in Ultrasonic Locationof Transformer Partial DischargeNicolas MoreiraNo ratings yet

- 049 - Flores Et Al - Loaeza - Rodriguez - Gonzalez - Flores - TerceñoDocument9 pages049 - Flores Et Al - Loaeza - Rodriguez - Gonzalez - Flores - TerceñosicokumarNo ratings yet

- An Improved Genetic Algorithm and Its Blending Application With Neural NetworkDocument3 pagesAn Improved Genetic Algorithm and Its Blending Application With Neural NetworkVishnu S. M. YarlagaddaNo ratings yet

- Literature ReviewDocument6 pagesLiterature ReviewMatthew RyanNo ratings yet

- Civicioglu 2013Document20 pagesCivicioglu 2013Abdelrafik TOUZENNo ratings yet

- Exploiting A Workstation Network For Automatic Generation of Test Patterns For Digital CircuitsDocument17 pagesExploiting A Workstation Network For Automatic Generation of Test Patterns For Digital CircuitsDhwal MehtaNo ratings yet

- SPE 59308 IOR Evaluation and Applicability Screening Using Artificial Neural NetworksDocument6 pagesSPE 59308 IOR Evaluation and Applicability Screening Using Artificial Neural NetworksenrileiNo ratings yet

- 2010 Amcalar Design, Implementation and Evaluation of A Real-Time P300-Based Brain-Computer Interface SystemDocument4 pages2010 Amcalar Design, Implementation and Evaluation of A Real-Time P300-Based Brain-Computer Interface SystemNolam NolNo ratings yet

- IJETA-V4I2P13 O. Deepa Dr. J. Suguna PDFDocument6 pagesIJETA-V4I2P13 O. Deepa Dr. J. Suguna PDFAmulya AnuragNo ratings yet

- Thesis Genetic AlgorithmDocument7 pagesThesis Genetic Algorithmcarmensanbornmanchester100% (1)

- Movement prediction from real-world images using a liquid state machineDocument12 pagesMovement prediction from real-world images using a liquid state machinePhuong anNo ratings yet

- Ga 1Document15 pagesGa 1Sumala G LakshmiNo ratings yet

- Next Generation Sequencing and Sequence Assembly: Methodologies and AlgorithmsFrom EverandNext Generation Sequencing and Sequence Assembly: Methodologies and AlgorithmsNo ratings yet

- Chapter - 1: Another Problem During The Time of Optimizing Any Objective FunctionsDocument14 pagesChapter - 1: Another Problem During The Time of Optimizing Any Objective FunctionsHossein HosseinNo ratings yet

- A Review of Clonal Selection Algorithm and Its AppDocument23 pagesA Review of Clonal Selection Algorithm and Its AppRaja ANo ratings yet

- Thesis Genetic Algorithm PDFDocument5 pagesThesis Genetic Algorithm PDFveronicamorseaurora100% (1)

- PHD Thesis Genetic AlgorithmDocument8 pagesPHD Thesis Genetic Algorithmrobinmoralestopeka100% (2)

- Anfis PDFDocument11 pagesAnfis PDFAnamika PancholiNo ratings yet

- Spectrum Allocation FireflyDocument11 pagesSpectrum Allocation FireflyAnumandla kiran kumarNo ratings yet

- A Novel Modified Sparrow Search Algorithm With Application in Side Lobe Level Reduction of Linear Antenna ArrayDocument25 pagesA Novel Modified Sparrow Search Algorithm With Application in Side Lobe Level Reduction of Linear Antenna ArrayghorbanlNo ratings yet

- Workpackage 4: Optimization: Distributed Modelling ApproachDocument4 pagesWorkpackage 4: Optimization: Distributed Modelling ApproachMelissa MillerNo ratings yet

- The Application Research of Genetic Algorithm: Jumei ZhangDocument4 pagesThe Application Research of Genetic Algorithm: Jumei ZhangSanderNo ratings yet

- Parallel Smith-Waterman Algorithm For Gene SequencingDocument4 pagesParallel Smith-Waterman Algorithm For Gene SequencingEditor IJRITCCNo ratings yet

- A Parallel Evolutionary Algorithm Applied To The Minimum Interference Frequency Assignment ProblemDocument12 pagesA Parallel Evolutionary Algorithm Applied To The Minimum Interference Frequency Assignment ProblemKhaled MeriNo ratings yet

- Introduccion UPDocument16 pagesIntroduccion UPOscar SanchezNo ratings yet

- Germinal Center Optimization Applied to Neural Inverse Optimal ControlDocument16 pagesGerminal Center Optimization Applied to Neural Inverse Optimal ControlOscar SanchezNo ratings yet

- Combinational Circuit Design Using Genetic AlgorithmsDocument7 pagesCombinational Circuit Design Using Genetic AlgorithmsJournal of Computer ApplicationsNo ratings yet

- Interactive Evolutionary Computation in Identification of Dynamical SystemsDocument12 pagesInteractive Evolutionary Computation in Identification of Dynamical SystemsmdjudeNo ratings yet

- Research ProposalDocument8 pagesResearch ProposalJavaria Chiragh100% (1)

- Time Domain Structural Health Monitoring With Magnetostrictive Patches Using Five Stage Hierarchical Neural NetworksDocument7 pagesTime Domain Structural Health Monitoring With Magnetostrictive Patches Using Five Stage Hierarchical Neural NetworksDebiprasad GhoshNo ratings yet

- Nimpitiwan s20 ReportDocument233 pagesNimpitiwan s20 ReportbajricaNo ratings yet

- Dietmar Heinke and Fred H. Hamker - Comparing Neural Networks: A Benchmark On Growing Neural Gas, Growing Cell Structures, and Fuzzy ARTMAPDocument13 pagesDietmar Heinke and Fred H. Hamker - Comparing Neural Networks: A Benchmark On Growing Neural Gas, Growing Cell Structures, and Fuzzy ARTMAPTuhmaNo ratings yet

- EpsocDocument8 pagesEpsocapi-3712774No ratings yet

- Particle Swarm OptimizationDocument17 pagesParticle Swarm OptimizationMitul Kumar AhirwalNo ratings yet

- PR Oof: Memristor Models For Machine LearningDocument23 pagesPR Oof: Memristor Models For Machine LearningtestNo ratings yet

- Genetic Algorithm Research Paper 2012Document8 pagesGenetic Algorithm Research Paper 2012afmczrsey100% (1)

- 10 1 1 131 6734 PDFDocument9 pages10 1 1 131 6734 PDFKyaw Min ThetNo ratings yet

- Investigation On The Performance of Linear Antenna Array Synthesis Using Genetic AlgorithmDocument7 pagesInvestigation On The Performance of Linear Antenna Array Synthesis Using Genetic AlgorithmCyberJournals MultidisciplinaryNo ratings yet

- Model-Free Functional MRI Analysis Using Kohonen Clustering Neural Network and Fuzzy - MeansDocument12 pagesModel-Free Functional MRI Analysis Using Kohonen Clustering Neural Network and Fuzzy - MeansOsoesantoYusufNurFathoniNo ratings yet

- Alser 等。 - 2019 - Shouji a Fast and Efficient Pre-Alignment FilterDocument24 pagesAlser 等。 - 2019 - Shouji a Fast and Efficient Pre-Alignment Filter潘炤伍No ratings yet

- Term Paper On Genetic Algorithm and Its ApplicationsDocument6 pagesTerm Paper On Genetic Algorithm and Its ApplicationsaflsiqhahNo ratings yet

- Partial-Update Adaptive Signal Processing: Design Analysis and ImplementationFrom EverandPartial-Update Adaptive Signal Processing: Design Analysis and ImplementationNo ratings yet

- 0 AE549 BEd 01Document6 pages0 AE549 BEd 01Italo ChiarellaNo ratings yet

- Synchronous Machine TestsDocument10 pagesSynchronous Machine TestsItalo ChiarellaNo ratings yet

- 0 FF349 BEd 01Document6 pages0 FF349 BEd 01Italo ChiarellaNo ratings yet

- Yi Ming 2003Document7 pagesYi Ming 2003Italo ChiarellaNo ratings yet

- Observation of Frequency Oscillation in Western Japan 60Hz Power System Based On Multiple Synchronized Phasor MeasurementsDocument6 pagesObservation of Frequency Oscillation in Western Japan 60Hz Power System Based On Multiple Synchronized Phasor MeasurementsItalo ChiarellaNo ratings yet

- 5 A58243 FD 01Document8 pages5 A58243 FD 01Italo ChiarellaNo ratings yet

- 141020131617446117500Document8 pages141020131617446117500Italo ChiarellaNo ratings yet

- A Uniform Line Model For Non-Uniform Single-Phase Lines With Frequency Dependent Electrical ParametersDocument6 pagesA Uniform Line Model For Non-Uniform Single-Phase Lines With Frequency Dependent Electrical ParametersItalo ChiarellaNo ratings yet

- Street Light by Using ZigbeeDocument5 pagesStreet Light by Using ZigbeeRohit Khodke100% (1)

- A Fast Electric Load Forecasting UsingDocument6 pagesA Fast Electric Load Forecasting UsingItalo ChiarellaNo ratings yet

- Simulation of The Impact of Wind Power On The Transient Fault BehaviorDocument10 pagesSimulation of The Impact of Wind Power On The Transient Fault Behaviormanigopal123No ratings yet

- Abdel Akher2014Document6 pagesAbdel Akher2014Italo ChiarellaNo ratings yet

- Operating Stationary Fuel Cells On Power System and Micro-GridsDocument6 pagesOperating Stationary Fuel Cells On Power System and Micro-GridsItalo ChiarellaNo ratings yet

- Replicating Interruptible Supply Contracts For Security Constrained Transmission ManagementDocument7 pagesReplicating Interruptible Supply Contracts For Security Constrained Transmission ManagementItalo ChiarellaNo ratings yet

- Analysing Negative Skewness of Spot Returns in The Australian Electricity MarketDocument7 pagesAnalysing Negative Skewness of Spot Returns in The Australian Electricity MarketItalo ChiarellaNo ratings yet

- CD2 B2 C3 CD 01Document4 pagesCD2 B2 C3 CD 01Italo ChiarellaNo ratings yet

- ACEE3 D87 D 01Document6 pagesACEE3 D87 D 01Italo ChiarellaNo ratings yet

- Applications of Optical Current and Voltage Sensors in High-Voltage SystemsDocument4 pagesApplications of Optical Current and Voltage Sensors in High-Voltage SystemsItalo ChiarellaNo ratings yet

- An Efficient Multi-Objective Meta-Heuristic Method For Distribution Network Expansion PlanningDocument6 pagesAn Efficient Multi-Objective Meta-Heuristic Method For Distribution Network Expansion PlanningItalo ChiarellaNo ratings yet

- Stochastic Assessment of Unbalanced Voltage Dips in Large Transmission SystemsDocument8 pagesStochastic Assessment of Unbalanced Voltage Dips in Large Transmission SystemsItalo ChiarellaNo ratings yet

- A6 E733 C1 D 01Document7 pagesA6 E733 C1 D 01Italo ChiarellaNo ratings yet

- CD9 C2 C3 CD 01Document8 pagesCD9 C2 C3 CD 01Italo ChiarellaNo ratings yet

- An Integrated Machine Learning Model For Day-Ahead Electricity Price ForecastingDocument7 pagesAn Integrated Machine Learning Model For Day-Ahead Electricity Price ForecastingItalo ChiarellaNo ratings yet

- Direct Load Control As A Market-Based Program in Deregulated Power IndustriesDocument4 pagesDirect Load Control As A Market-Based Program in Deregulated Power IndustriesItalo ChiarellaNo ratings yet

- Technological Evolution of MV Equipment and Structure NetworkDocument5 pagesTechnological Evolution of MV Equipment and Structure NetworkItalo ChiarellaNo ratings yet

- Power System Stability Improvement by Energy Storage Type STATCOMDocument7 pagesPower System Stability Improvement by Energy Storage Type STATCOMItalo ChiarellaNo ratings yet

- CA3 C2 C3 CD 01Document7 pagesCA3 C2 C3 CD 01Italo ChiarellaNo ratings yet

- A Dynamic SecurityDocument8 pagesA Dynamic SecurityItalo ChiarellaNo ratings yet

- CCB82C3Cd01 PDFDocument4 pagesCCB82C3Cd01 PDFItalo ChiarellaNo ratings yet

- Overpopulation in EgyptDocument9 pagesOverpopulation in EgyptAhmed Sobhy KhattabNo ratings yet

- Speciation: Process of Speciation Reproductive Isolating Mechanisms 2 Dimensions of Evolution Modes of SpeciationDocument15 pagesSpeciation: Process of Speciation Reproductive Isolating Mechanisms 2 Dimensions of Evolution Modes of SpeciationdumayantiNo ratings yet

- Anthro 1020 Darwin FinchesDocument6 pagesAnthro 1020 Darwin Finchesapi-312174259No ratings yet

- Module 28 - EditedDocument11 pagesModule 28 - Editedrichard reyesNo ratings yet

- Hybridization in Freshwater Fishes A Review of CasDocument33 pagesHybridization in Freshwater Fishes A Review of CasCássia Gabriel RinaldiNo ratings yet

- General Biology 2: Department of EducationDocument3 pagesGeneral Biology 2: Department of EducationJaime SorianoNo ratings yet

- Worksheet - Chapter 7 - EvolutionDocument3 pagesWorksheet - Chapter 7 - Evolutionsukaina fatimaNo ratings yet

- Chapter 10 Variation LATESTDocument63 pagesChapter 10 Variation LATESTSiti AthilahNo ratings yet

- Lecture 1 - Historical Perspectives On Brain and BehaviorDocument12 pagesLecture 1 - Historical Perspectives On Brain and BehaviorA KNo ratings yet

- Definition, Aim, Objectives and Scope of Plant BreedingDocument137 pagesDefinition, Aim, Objectives and Scope of Plant BreedingYosef AndualemNo ratings yet

- Chapter 30-31 EvolutionDocument10 pagesChapter 30-31 EvolutionKiu yu LiuNo ratings yet

- M. SC Wildlife Biology and Conservation National Entrance Test, December 10, 2017Document21 pagesM. SC Wildlife Biology and Conservation National Entrance Test, December 10, 2017Barnali DuttaNo ratings yet

- Introduction To Physical Anthropology 2013 2014 Edition 14th Edition Jurmain Test BankDocument26 pagesIntroduction To Physical Anthropology 2013 2014 Edition 14th Edition Jurmain Test BankJohnGibsoneios100% (47)

- StsreviewerDocument15 pagesStsreviewerSy CervantesNo ratings yet

- Darwin's Original Contributions to the Theory of Natural SelectionDocument5 pagesDarwin's Original Contributions to the Theory of Natural SelectionPaco AlcacerNo ratings yet

- LS SA #1 (Change Over Time) : Test/Quiz CommentsDocument6 pagesLS SA #1 (Change Over Time) : Test/Quiz Commentsapi-357968234No ratings yet

- Lessonexemplarculed207 FsaribuaboDocument34 pagesLessonexemplarculed207 FsaribuaboCherubim GanayNo ratings yet

- Human Bio-Cultural Social EvolutionDocument21 pagesHuman Bio-Cultural Social EvolutionAndrey CabuntocanNo ratings yet

- Buddhism and ScienceDocument24 pagesBuddhism and SciencepgmetgudNo ratings yet

- The Broken Globe ThesisDocument8 pagesThe Broken Globe ThesisHelpOnWritingAPaperUK100% (2)

- Bryson Reading Guide-3Document32 pagesBryson Reading Guide-3sherinrachiNo ratings yet

- Dawkins by DennettDocument2 pagesDawkins by DennettJBNo ratings yet