Professional Documents

Culture Documents

IJSR PaperFormat-1

Uploaded by

sneha sakundeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IJSR PaperFormat-1

Uploaded by

sneha sakundeCopyright:

Available Formats

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

Level Shifted Pulse Width Modulation in Three

Phase Multilevel Inverter for Power Quality

Improvement

S. B. Sakunde1, V. D. Bavdhane2

1

PG Student, 2Assistant Professor

Department of Electrical Engg,

Zeal education societys DCOE, Narhe ,Pune, Maharashtra, India

1

sakunde.sneha@gmail.com, 2vivek.bavdhane@zealeducation.com

Abstract: This paper emphasize on harmonics elimination by using 5 level cascaded H-bridge (CHB) inverter. The CHB inverter is

having more importance in power electronics application due to reduction in switching losses to other type of inverter. The inverter

is adopted with level shifted PWM (LSPWM) technique. The reference harmonics compensating current signal is generated by

synchronous reference frame (SRF) theory and DC side voltage of inverter is regulated by using PI controller. The inverter functions

as a DSTATCOM for reduction of harmonics and improvement of power factor. System is designed in MATLAB/SIMULINK for

11kV distribution system.

Keywords: Synchronous reference frame theory (SRF), phase shifted carrier pulse width modulation (PSCPWM), level shifted carrier

pulse width modulation (LSCPWM), cascaded H bridge multilevel inverter (CHB)

1. Introduction

With present distribution system, the use of non-linear

devices has been increased to large extent which results in

injection of large amount of harmonics in the distribution

side which further leads to major power quality issues. The

consequences observed are voltage sag, swell, heating effects

in rotating devices, reactive power burden, lagging power

factor etc. [1-5]

With development in power utility and power electronics,

various techniques have been implemented for reduction of

harmonics. The multilevel inverter found their importance

in power quality improvement.[6-9] The most important

topologies like diode-clamped inverter (neutral-point

clamped), capacitor-clamped (flying capacitor), and

cascaded multilevel inverters with separate dc sources are

discussed in literatures. Various control and modulation

techniques are being presented for these topologies of

inverters. [10-12]

This paper focuses on level shifted pulse width technique

used for cascaded 5 level H-bridge inverter. This inverter

functions as DSTATCOM in order to reduce harmonics and

improves the power factor also.

DSTATCOM voltage is lower than source voltage then

power is absorbed from transmission line. The schematic

diagram of DSTATCOM is presented in fig.1.

Figure 1: Schematic diagram of DSTATCOM

2. DSTATCOM

DSTATCOM consists of voltage source converter (VSC)

with DC link capacitor connected in shunt, capable of

absorbing or supplying the reactive power. As VSC is

having two voltage levels, the power injection takes place

but harmonics remain same. In order to reduce the

harmonic contents DSTATCOM with multilevel inverter is

expected for better operation. DSTATCOM also improves

power factor to unity.[9]

DSTATCOM converts DC link voltage into set of three

phase AC voltage so that active and reactive power transfer

to transmission line takes place. If DSTATCOM voltage is

equal to source voltage then there is no power transfer to

transmission line. If DSTATCOM voltage is greater than

source voltage then power is injected to transmission line. If

This paper proposes DSTATCOM with five level CHB

inverter with DC link as capacitor which stores or inject

power as per requirement. DSTATCOM is connected in

shunt to transmission line through inductive reactance

which is useful for filtering action. Also the DSTATCOM

produces current having magnitude equal to of harmonics

current but opposite in direction so that harmonics current

get nullified. As it is capable of injecting reactive power at

point of common coupling (PCC), the voltage profile is

improved which leads to improved voltage regulation.

3. Three Phase Cascaded Multilevel Inverter

A five level LSPWM based CHB is illustrated in fig.2. DC

source is connected to each inverter separately. Each

Volume 4 Issue 7, July 2015

www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

inverter in a phase generates three different voltage outputs,

+Vdc, 0, and Vdc by different combinations of the four

switches. In CHB inverter the ac outputs of each of the

different full bridge inverter levels are connected in series

such that the synthesized voltage waveform is the sum of the

inverter outputs. The number of output phase voltage levels

of inverter x in a cascaded inverter is defined by x=2y+1,

where y is per phase separate dc sources.

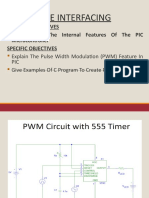

Figure 3: Level Shifted carrier PWM

The level shifted carrier pulses are generated with repeating

sequence in MATLAB/SIMULINK environment as shown

in fig. 4. Carrier waveform is continuously compared with

error signal to provide gate signal to inverter.

5. MATLAB Modeling and Results

The

system

parameters

considered

simulation study are tabulated in table-1.

for

Table 1: System parameter

Figure 2: Three phase cascaded five level inverter

4. PWM technique for gate signal generation

Generally following two PWM methods are used for gate

signal generation in multilevel inverters.

1. Level Shifted Carrier PWM (LSCPWM)

2. Phase Shifted Carrier PWM (PSCPWM)

System parameter

Rating

Source voltage

11 kV

Frequency

50Hz

DC bus capacitance

1550e-6F

Inverter series inductance

10 mH

Source resistance

0.1 ohm

Source inductance

0.9 mH

Load resistance

60 ohms

Load inductance

30mH

5.1 Results Obtained Without DSTATCOM

The Matlab model for basic power system without any

compensating device is shown in Fig.5.

The level shifted pulse width modulation technique has

three types [13]

1. In Phase disposition

2. Phase disposition opposition

3. Alternate phase opposition disposition

This work focuses on in phase disposition method where all

the carrier signals are in phase as shown in Fig.3. The

number of carrier waveforms required are given by m-1,

where m is number of output voltage levels. So the 5 level

CHB inverter requires four triangular carrier waveforms.

The triangular carrier waveforms with frequency 2 kHz are

chosen.

Figure 5: Basic uncompensated power system under

study with a nonlinear load

The source voltage, current and load current

without DSTATCOM are presented in fig.6. It

seems that load current and source current

Volume 4 Issue 7, July 2015

www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

both are same and non sinusoidal without

DSTATCOM.

Fig -6: Source voltage, source current and

load current without DSTATCOM

6

The harmonic spectrum of Phase-A source

current without DSTATCOM is presented in

fig.7. The THD of source current without

Fig -8: Simulink model of power system with

DSTATCOM

The voltage of Phase A of Five level LSPWM

inverter is represented in fig. 9. It shows five

step output

DSTATCOM is observed as 28.25%.

Fig -7: Harmonic spectrum of Phase-A Source

Fig -9: Five level output voltage of inverter.

Fig -10. Shows Source voltage, current and load

current with five level CHB inverter with LSPWM

based DSTATCOM using SRF method. In this

case the source current is found more

sinusoidal in comparison to system without

compensating device.

current without DSTATCOM

5.2 Results Obtained with LSCPWM

based DSTATCOM

The MATLAB/SIMULINK model of power system

under study compensated with multilevel CHB

based inverter with LSPWM using SRF based

method is represented in fig.8.

Volume 4 Issue 7, July 2015

www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

Fig -10: Source voltage, current and load current with

five level CHB inverter with LSCPWM based DSTATCOM

using SRF.

Harmonic spectrum analysis of Phase-A Source

current with five level CHB inverter with PSPWM

based DSTATCOM using SRF method is shown in

fig.11. The THD of source current with five level

inverter is further reduced to 4.68%.

6. CONCLUSION

In this paper five level multilevel inverter with

LSCPWM based CHB inverter is presented. The

percentage of total harmonic distortion is

reduced with LSCPWM multilevel inverter

method of gate signal generation from 28.25 to

4.65 %. This method found superior in support

to power quality issue. The total harmonics

distortion can be further reduced by increasing

number of steps of inverter.

REFERENCES

[1] N. G. Hingorani, Introducing Custom Power, IEEE

Spectrum, vol.32, pp.41-48, june1995

[2] M. Jawad, H. Mokhtari, Impact of harmonics on power

quality and losses in power distribution systems,

International Journal of Electrical and computer engg.,

vol.5, no.1, feb-2015, pp. 166-174.

[3] Angela Iagar, Gabriel Nicolae Popa, Corina Maria Dinis,

The influence of home nonlinear electric equipments

operating modes on power quality, WSEAS Transactions

Fig -11: Harmonic spectrum analysis of Phase- on systems, ISSN: 2224-2678, vol.13, 2014

A Source current with five level CHB inverter[4] S. Khalid, Bharti Dwiwedi, Power Quality issue,

problems, standards and their effect in industry with

with LSCPWM based DSTATCOM using SRF

corrective means, International Journal of Advances in

Engineering & Technology, May 2011

For this case the source current and voltage

[5] Haroon Farooq*, Chengke Zhou, Mohamed Emad Farrag,

both are found to be in phase, so power factor Analyzing the Harmonic Distortion in a Distribution System

Caused by the Non-Linear Residential Loads, International

is unity as shown in fig.12.

Journal of Smart Grid and Clean Energy, august 2012.

[6] Jos Rodrguez, Jih-Sheng Lai, Fang Zheng Peng,

Multilevel Inverters: A Survey of Topologies, Controls, and

Applications, IEEE Trans. on Industrial Electronics, Vol.

49, No. 4, Aug. 2002

[7] Dr. Jagdish Kumar, THD Analysis for Different Levels of

Cascaded Multilevel Inverters for Industrial Applications,

International Journal of Emerging Technology and

Advanced Engineering, Volume 2, Issue 10, October 2012

[8] J.S.Lai. and F.Z.Peng "Multilevel converters - A new bread

of converters, "IEEE Trans. Ind.Appli. vo1.32. No.3.

pp.S09-S17. May/ Jun. 1996.

[9] J. Ganesh Prasad Reddy and K. Ramesh Reddy Design

and Simulation of Cascaded H-Bridge Multilevel Inverter

Based DSTATCOM for Compensation of Reactive Power

Fig -12: Phase A source voltage and current

and Harmonics,1 st Infl Conf. on Recent Advances in

Meanwhile the DC side voltage of capacitor is

Information Technology RAIT-2012

[10] P.Bhagwat. and V.R.Stefanovic. "Generalized structure of a

regulated to 11KV as shown in fig.13.

multilevel PWM Inverter:' IEEE Trans. Ind. Appln, VoI.IA19. no.6, pp. I OS7-1069, Nov.!Dec. 1983.

[11] Roozbeh Naderi, and Abdolreza rahmati, "Phase-shifted

carrier PWM technique for general cascaded inverters,"

IEEE Trans. Power.Electron., vo1.23, no.3, pp. I 257-I 269.

May.2008.

[12] B. P. McGrath and D. G. Holmes, "Multicarrier PWM

strategies for multilevel inverters," IEEE Trans. Ind.

Electron., vol. 49, no. 4, pp.858- 867, August 2002.

[13] A.Venkatakrishna, R. Somnatham, Sandeep Reddy, Phase

Shifted and Level Shifted PWM Based Cascaded Multilevel

Inverter Fed Induction Motor Drive, International Journal

of Current Engineering and Technology, Vol.4, No.1

(February 2014)

Fig -13: DC bus voltage.

Volume 4 Issue 7, July 2015

www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

Volume 4 Issue 7, July 2015

www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

You might also like

- Engineering Journal Software Based Reconfiguration For The Cascaded H-Bridge Multilevel ConverterDocument8 pagesEngineering Journal Software Based Reconfiguration For The Cascaded H-Bridge Multilevel ConverterEngineering JournalNo ratings yet

- Naresh DC Re Injection FinalDocument6 pagesNaresh DC Re Injection FinalRamu ThommandruNo ratings yet

- For Final ThesisDocument28 pagesFor Final ThesisParkash Kaur GillNo ratings yet

- International Journal of Research in Computer Applications and RoboticsDocument8 pagesInternational Journal of Research in Computer Applications and Roboticsakashgrg07No ratings yet

- Static Synchronous Series Compensator Using ADocument4 pagesStatic Synchronous Series Compensator Using ASai Bhargav VeerabathiniNo ratings yet

- Improved Power Quality For Renewable Power Generation Systems Presence of Non-Linear LoadsDocument6 pagesImproved Power Quality For Renewable Power Generation Systems Presence of Non-Linear LoadsPhanikumar Bellam KondaNo ratings yet

- I C D M I T C W I: Mplementation and Ontrol Ifferent Ultilevel Nverter Opologies For Urrent Aveform MprovementDocument9 pagesI C D M I T C W I: Mplementation and Ontrol Ifferent Ultilevel Nverter Opologies For Urrent Aveform MprovementNguyễn Trung HiếuNo ratings yet

- SRCEM Three level H-bridge inverter reportDocument7 pagesSRCEM Three level H-bridge inverter reportAnil ShahNo ratings yet

- High Efficiency THIPWM Three-Phase Inverter For Grid Connected SystemDocument6 pagesHigh Efficiency THIPWM Three-Phase Inverter For Grid Connected SystemffarhaniNo ratings yet

- A Unity Power Factor Converter Using HalfDocument14 pagesA Unity Power Factor Converter Using HalfLivia Faria PeresNo ratings yet

- Sample Paper - ICPCES 2010Document5 pagesSample Paper - ICPCES 2010ShwetaGautamNo ratings yet

- Multi Level Statcom For Harmonic ReductionDocument8 pagesMulti Level Statcom For Harmonic ReductionInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- 498 610 PDFDocument5 pages498 610 PDFhafiz858No ratings yet

- Cascaded Theory - FullDocument14 pagesCascaded Theory - FullTJPRC PublicationsNo ratings yet

- 51i8 Ijaet0805989 Performance and EvaluationDocument10 pages51i8 Ijaet0805989 Performance and EvaluationSureshNo ratings yet

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocument5 pagesImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNo ratings yet

- Mac Int J.Power ElectronicsDocument14 pagesMac Int J.Power Electronicssandeepbabu28No ratings yet

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDocument6 pagesMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNo ratings yet

- Harmonics and Torque Ripple Reduction of Brushless DC Motor (BLDCM) Using Cascaded H-Bridge Multilevel InverterDocument4 pagesHarmonics and Torque Ripple Reduction of Brushless DC Motor (BLDCM) Using Cascaded H-Bridge Multilevel InverterPidikiti Surendra BabuNo ratings yet

- Electrical - Ijeeer - 16 - Cell Back-To-back - NaveenaDocument12 pagesElectrical - Ijeeer - 16 - Cell Back-To-back - NaveenaTJPRC PublicationsNo ratings yet

- Power Quality Improvement of Grid Interconnected 3-Phase 4-Wire Distribution System Using Fuzzy Logic ControlDocument5 pagesPower Quality Improvement of Grid Interconnected 3-Phase 4-Wire Distribution System Using Fuzzy Logic ControlJeyanthi GanesanNo ratings yet

- 14 - New Cascaded PDFDocument9 pages14 - New Cascaded PDFsreekantha2013No ratings yet

- HVDC System Harmonic Reduction with VSCDocument7 pagesHVDC System Harmonic Reduction with VSCGiwrgos GewrgiadisNo ratings yet

- ARTICLE Onduleurs MultiniveauxDocument14 pagesARTICLE Onduleurs MultiniveauxKhalid SalmiNo ratings yet

- Maswood 01035144Document9 pagesMaswood 01035144rahulanlNo ratings yet

- Control Strategy For Three Phase PWM Rectifier Using SVM ModulationDocument7 pagesControl Strategy For Three Phase PWM Rectifier Using SVM Modulationeditor_ijtelNo ratings yet

- Iceict2015i020315001 PDFDocument6 pagesIceict2015i020315001 PDFmadihaNo ratings yet

- Buck & Boost Operation Using Single Phase Matrix ConverterDocument25 pagesBuck & Boost Operation Using Single Phase Matrix ConverterManu JainNo ratings yet

- Design of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsDocument6 pagesDesign of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsManpreet SinghNo ratings yet

- Transformer Less Voltage Quadrupler Based DC-DC Converter With Coupled Inductor and PI Filter For Increased Voltage Gain and EfficiencyDocument8 pagesTransformer Less Voltage Quadrupler Based DC-DC Converter With Coupled Inductor and PI Filter For Increased Voltage Gain and EfficiencywelsyaNo ratings yet

- Pulse August 2014Document16 pagesPulse August 2014lets_share_sthNo ratings yet

- Neuro Controlled Seven Level Shunt Active Power Filter For Power Quality EnhancementDocument9 pagesNeuro Controlled Seven Level Shunt Active Power Filter For Power Quality EnhancementInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- 2.analysis of Different - FullDocument10 pages2.analysis of Different - Fulliaset123No ratings yet

- A Novel Single Phase Cascaded H-Bridge Inverter With Reduced Power Electronics SwitchesDocument8 pagesA Novel Single Phase Cascaded H-Bridge Inverter With Reduced Power Electronics SwitchesHemanth KumarNo ratings yet

- A Novel Passive Filter To Reduce PWM Inverters Adverse Effects in Electrical Machine SystemDocument9 pagesA Novel Passive Filter To Reduce PWM Inverters Adverse Effects in Electrical Machine SystemshaheerdurraniNo ratings yet

- A Novel Control Strategy of Indirect Matrix ConverDocument10 pagesA Novel Control Strategy of Indirect Matrix Convermạnh phanNo ratings yet

- Harmonic Reduction in Parallel Inverters Using THIPWMDocument6 pagesHarmonic Reduction in Parallel Inverters Using THIPWMAhmed JanadNo ratings yet

- Indirect Control For Cascaded H-Bridge Rectifiers With Unequal LoadsDocument6 pagesIndirect Control For Cascaded H-Bridge Rectifiers With Unequal Loadsvinay kumarNo ratings yet

- Pod-Pwm Based Capacitor Clamped Multilevel InverterDocument3 pagesPod-Pwm Based Capacitor Clamped Multilevel InverterInternational Jpurnal Of Technical Research And ApplicationsNo ratings yet

- Reduction of THD in Power Systems Using STATCOMDocument5 pagesReduction of THD in Power Systems Using STATCOMeditor9891No ratings yet

- Ijsron2013794 PDFDocument5 pagesIjsron2013794 PDFRaviIdhayachanderNo ratings yet

- Multilevel InverterDocument7 pagesMultilevel InverterJournalNX - a Multidisciplinary Peer Reviewed JournalNo ratings yet

- Direct Power Control Strategies For Multilevel Inverter Based Custom Power DevicesDocument9 pagesDirect Power Control Strategies For Multilevel Inverter Based Custom Power DevicestrrplacementNo ratings yet

- Modified Multilevel Inverter Topology For Grid Connected PV SystemsDocument7 pagesModified Multilevel Inverter Topology For Grid Connected PV SystemsAJER JOURNALNo ratings yet

- Precision Constant Current Source For Electrical Impedance TomographyDocument4 pagesPrecision Constant Current Source For Electrical Impedance Tomographyjorgeluis.unknownman667No ratings yet

- Qwe Erer-135Document9 pagesQwe Erer-135vinai2086No ratings yet

- Power Quality Improvement, THD Analysis Using Dstatcom For Low Voltage SystemDocument14 pagesPower Quality Improvement, THD Analysis Using Dstatcom For Low Voltage SystemTJPRC PublicationsNo ratings yet

- An Optimized Three-Phase Multilevel Inverter Topology With Separate Level and Phase Sequence Generation PartDocument26 pagesAn Optimized Three-Phase Multilevel Inverter Topology With Separate Level and Phase Sequence Generation PartNaga AnanthNo ratings yet

- Power Quality Improvement of Unified Power Quality Conditioner Using Reference Signal Generation MethodDocument5 pagesPower Quality Improvement of Unified Power Quality Conditioner Using Reference Signal Generation MethodSurya Ch VenkataNo ratings yet

- Three-Level Inverter Speed Control of Induction MotorDocument12 pagesThree-Level Inverter Speed Control of Induction MotorMallikarjunBhiradeNo ratings yet

- Modeling and Simulation of Matrix Converter Using Pi and Fuzzy Logic ControllerDocument9 pagesModeling and Simulation of Matrix Converter Using Pi and Fuzzy Logic Controllertayeb deNo ratings yet

- 9-Level Trinary DC Source Inverter Using Embedded ControllerDocument6 pages9-Level Trinary DC Source Inverter Using Embedded ControllerIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNo ratings yet

- Design and Construction of Single Phase Pure Sine Wave Inverter For Photo Voltaic ApplicationDocument4 pagesDesign and Construction of Single Phase Pure Sine Wave Inverter For Photo Voltaic ApplicationRafid Haider ShantonuNo ratings yet

- A New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterDocument8 pagesA New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterVenktesh MishraNo ratings yet

- 125 130 PDFDocument6 pages125 130 PDFJubin JainNo ratings yet

- Control Strategy for Three-Phase PWM Boost RectifierDocument18 pagesControl Strategy for Three-Phase PWM Boost RectifierHoàngMạnhTuấnNo ratings yet

- PI, FUZZY and ANFIS Control of 3-Phase Shunt Active Power FilterDocument9 pagesPI, FUZZY and ANFIS Control of 3-Phase Shunt Active Power FilterHery SetyoNo ratings yet

- Modeling and Simulation of Frequency Converter Used in Speed Control of Asynchronous MotorDocument6 pagesModeling and Simulation of Frequency Converter Used in Speed Control of Asynchronous MotorLelosPinelos123No ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- MGM CET Course Plan for Conventional and Non-Conventional Power GenerationDocument3 pagesMGM CET Course Plan for Conventional and Non-Conventional Power Generationsneha sakundeNo ratings yet

- SsDocument49 pagesSssneha sakundeNo ratings yet

- ManagemntDocument51 pagesManagemntsneha sakundeNo ratings yet

- ManagemntDocument51 pagesManagemntsneha sakundeNo ratings yet

- Introduction To Voice AlarmDocument58 pagesIntroduction To Voice AlarmShaaban HassanNo ratings yet

- PBL62 1 30M3Document1 pagePBL62 1 30M3Hai Tran HongNo ratings yet

- Muhammad Usama: Internship at Ibrahim Fibres Limited, Polyester PlantDocument20 pagesMuhammad Usama: Internship at Ibrahim Fibres Limited, Polyester PlantUsamaNo ratings yet

- Pendola Suspendida MPK 450 1x150wDocument3 pagesPendola Suspendida MPK 450 1x150wwilber ticonaNo ratings yet

- Recommended Reading and Links On Public Bicycle SchemesDocument13 pagesRecommended Reading and Links On Public Bicycle SchemesZé MiguelNo ratings yet

- CA2005 User Manual 1.3-Custom-FDocument34 pagesCA2005 User Manual 1.3-Custom-FDinesh SreedharanNo ratings yet

- STT041 and STT041.1 PDFDocument59 pagesSTT041 and STT041.1 PDFHayrah Lawi100% (2)

- University of Tripoli Faculty of Engineering Petroleum EngineeringDocument10 pagesUniversity of Tripoli Faculty of Engineering Petroleum EngineeringesraNo ratings yet

- Reportte Cambios CPC 2a1Document1 pageReportte Cambios CPC 2a1FERNANDO FERRUSCANo ratings yet

- 8 State Based or Graph Based TestingDocument4 pages8 State Based or Graph Based TestingZINNIA MAZUMDER 19BIT0155No ratings yet

- Math 362, Problem Set 5Document4 pagesMath 362, Problem Set 5toancaoNo ratings yet

- K+12 Orientation & STEC SHS Program: Prepared By: Bryant C. AcarDocument76 pagesK+12 Orientation & STEC SHS Program: Prepared By: Bryant C. AcarElle Segovia SungaNo ratings yet

- Analyze: ADDIE WorksheetDocument2 pagesAnalyze: ADDIE WorksheetCatherine LaraNo ratings yet

- Interview@InfosysDocument13 pagesInterview@InfosysSudheer KumarNo ratings yet

- COT - Lesson PlanDocument4 pagesCOT - Lesson PlanLyzeanj SuycanoNo ratings yet

- 5S PDFDocument41 pages5S PDFpranayrulzNo ratings yet

- IEEE STD 1193™-2003 Guide For Measurement of Environmental SensitivitiesDocument81 pagesIEEE STD 1193™-2003 Guide For Measurement of Environmental SensitivitiesVitalyNo ratings yet

- Resume HarishArchitectDocument11 pagesResume HarishArchitectharishNo ratings yet

- 5.2 PWM 7 Mac 2017Document34 pages5.2 PWM 7 Mac 2017Elawarasi Nadarajan100% (1)

- ChironDocument13 pagesChironGP100% (1)

- References Edfd227 Group Assessment 2 Newsletter WebsiteDocument8 pagesReferences Edfd227 Group Assessment 2 Newsletter Websiteapi-523911286No ratings yet

- Rule 4 - Types of Construction (Book Format)Document2 pagesRule 4 - Types of Construction (Book Format)Thea AbelardoNo ratings yet

- Classroom Management PlanDocument6 pagesClassroom Management Planapi-607580556No ratings yet

- Origin and Meaninng of Little P in PH PDFDocument2 pagesOrigin and Meaninng of Little P in PH PDFlNo ratings yet

- Coggins Pop CycleDocument3 pagesCoggins Pop Cycleapi-518568920No ratings yet

- Electronic Devices and Circuit TheoryDocument32 pagesElectronic Devices and Circuit TheoryIñaki Zuriel ConstantinoNo ratings yet

- Managerial Roles and Skills in An OrganizationDocument7 pagesManagerial Roles and Skills in An Organizationanon_17604921833% (3)

- Altamirov DishniDocument95 pagesAltamirov DishniEmersonJParedes100% (1)

- Steps To Design A PCB Using OrcadDocument3 pagesSteps To Design A PCB Using OrcadkannanvivekananthaNo ratings yet

- WCO - Data Model PDFDocument25 pagesWCO - Data Model PDFCarlos Pires EstrelaNo ratings yet