Professional Documents

Culture Documents

I.P (Digital Electronics)

Uploaded by

HarmanWaliaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

I.P (Digital Electronics)

Uploaded by

HarmanWaliaCopyright:

Available Formats

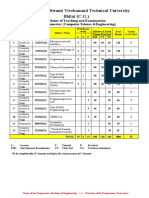

Lovely Professional University, Punjab

Course Code

Course Title

Course Planner

Lectures

ECE213

DIGITAL ELECTRONICS

13402::Bharat Sanklecha

Course Category

Courses with conceptual focus

3.0

TextBooks

Sr No

Title

Author

Edition

Year

Publisher Name

T-1

Digital Design Principles and

Practices

John F. Wakerly

4th

2008

Pearson Education, Inc.

Year

Publisher Name

Reference Books

Sr No

Title

Author

Edition

R-1

Digital Fundamentals

Thomas L. Floyd , R. P

Jain

8th

Pearson

R-2

Digital Electronics Principles and

Integrated Circuits

Anil K Maini

1st

Wiley

R-3

Digital Integrated Electronics

H. Taub and D. Schilling

1st

2008

M. G.Hills

R-4

Analysis & Design of Digital

Integrated Circuits

Resve Saleh, David

Hodges, Horace Jackson

3rd

2005

M. G.Hills

Relevant Websites

Sr No

(Web address) (only if relevant to the course)

Salient Features

RW-1

http://www.tutorialspoint.com/computer_logical_organization/octal_arithmetic.htm

Octal and hexadecimal Aritmetic

Audio Visual Aids

Sr No

(AV aids) (only if relevant to the course)

Salient Features

AV-1

http://nptel.iitm.ac.in/video.php?subjectId=117106086

Video Lectures

AV-2

http://filebox.ece.vt.edu/~jgtront/introcomp/flipflop_noaudio.swf

Animation of flip Flops

Software/Equipments/Databases

Sr No

(S/E/D) (only if relevant to the course)

Salient Features

SW-1

Proteus

Circuit Design and Simulation Tool

Sr No

(VL) (only if relevant to the course)

Salient Features

VL-1

http://www.digital.iitkgp.ernet.in/dec/index.php

Circuit Simulation

Virtual Labs

LTP week distribution: (LTP Weeks)

Tutorials Practicals Credits

0.0

0.0

3.0

Weeks before MTE

Weeks After MTE

Spill Over

Detailed Plan For Lectures

Week

Number

Lecture

Number

Broad Topic(Sub Topic)

Week 1

Lecture 1

Number Systems(Digital Systems)

Week 2

Chapters/Sections

of Text/reference

books

Other Readings, Lecture Description

Relevant

Websites, Audio

Visual Aids,

software and

Virtual Labs

Learning Outcomes

T-1:Chapter 1

Section 1.1 and 1.2

Lecture will explain the

digital systems in detail

with all system

requirement

Students will

understand basic

difference between

analog and digital

systems

Number Systems(Data

representation and coding)

T-1:Chapter 1

Section 1.4

Lecture will explain the

Electronic aspect of

digital design

how to represent data in

different formats

Lecture 2

Number Systems(Logic circuits)

T-1:Chapter 3

Section 3.1

How to design basic

logic circuits using

examples

designing of basic logic

circuits

Lecture 3

Number Systems(Implementation

of digital systems)

T-1:Chapter 1

Section 1.1 and 1.2

practical aspects of

digital system

understanding a digital

system its applications

and advantages

Lecture 4

Number Systems(Number

Systems)

R-2:Chapter 1

Section 1.2

Lecture will explain

about different

mathematical notations

that will represent

numbers of given set

Different methods of

expressing numbers

with symbols

Number Systems(CodesPositional number system)

T-1:Chapter 2

Section 2.1

Lecture will explain

placevalue notation is a

method of representing

or encoding numbers

use of the same symbol

for the different orders

of magnitude

Number Systems(Binary number

system)

R-2:Chapter 1

Section 1.4

Lecture will explain the

usual base 2 system that

is a positional notation

with a radix of 2

Representation of

numeric values using

two symbols 0 and 1

and its simplicity in

digital system

Number Systems(Methods of base

conversions)

T-1:Chapter 2

Section 2.3

Lecture will explain the Conversion of one

substitution,Division and number system to

Summation method for another number system

general positional

number system

conversions

Pedagogical Tool

Demonstration/ Case

Study / Images /

animation / ppt etc.

Planned

Week 2

Lecture 4

Number Systems(Binary

arithmetic)

Lecture 5

Number Systems(Representation

of signed numbers)

Lecture 6

Week 3

Lecture 7

Lecture 8

T-1:Chapter 2

Section 2.4 section

2.8 and 2.9

Binary addition

Subtraction

Multiplication and

division

Students will

understand basic rules

of binary addition

subtraction

Multiplication and

Division method

T-1:Chapter 2

Section 2.5

Lecture will explain

representation of

negative numbers using

simple and complement

method

Different formats used

for binary

representation of

negative numbers

Number Systems(Fixed numbers)

R-2:Chapter 1

Section 1.2

Introduction to number

system and its

represntation

Difference between

representation of fixed

and floating point

number system

Number Systems(Binary coded

decimal

codes)

T-1:Chapter 2

Section 2.10

Lecture will explain the

method to represent

decimal numbers using

8421 excess 3 and 2421

code

Students will

understand how digital

devices process and

display numbers in tens

Number Systems(Gray codes)

T-1:Chapter 2

section 2.11

Lecture will explain two

ways to construct a gray

code one is reflected

code and other is n bit

method

Students will

understand the

Electromechanical

applications of digital

systems

Number Systems(Error detection

code)

T-1:Chapter 2

Section 2.15

Lecture will explain

different error detection

codes and how to detect

one bit two bit and three

bit error using these

codes

students will be able to

detect the error in the

different codes using

these techniques

Number Systems(Parity check

codes)

R-2:Chapter 1

Section 1.23

Lecture explain error

detection technique by

adding extra bits

Students will

understand even and

odd parity error

detection technique

Number Systems(octal number

system)

T-1:Chapter 2

Section 2.2

Number Systems(Hexadecimal

number system)

T-1:Chapter 2

Section 2.16

RW-1

Lecture will explain the Students will

representation of number understand the

using radix 8

representation of multi

bit numbers using radix

radix 8

Lecture will explain the Students will

representation of number understand the

using radix 16

representation of multi

bit numbers using radix

radix 16

Week 3

Week 4

Week 5

Lecture 9

Number Systems(Error correction

code)

T-1:Chapter 2

Section 2.15

Lecture will explain

different error correction

codes and how to correct

one bit two bit and three

bit error using these

codes

students will be able to

correct the error in the

different codes using

these techniques

Number Systems(Hamming code)

T-1:Chapter 2

Section 2.15.3

Lecture 9 will explain

the Hamming codes that

is the one bit error

correction code on

message of any length

and Lecture 10 is

reserved for contingency

Students will

understand the

complete algorithm and

its use in

telecommunication ,

computing and other

applications

Lecture 10

Number Systems(Hamming code)

T-1:Chapter 2

Section 2.15.3

Lecture 9 will explain

the Hamming codes that

is the one bit error

correction code on

message of any length

and Lecture 10 is

reserved for contingency

Students will

understand the

complete algorithm and

its use in

telecommunication ,

computing and other

applications

Lecture 11

Number Systems(Octal arithmetic)

T-1:Chapter 2

Section 2.2

RW-1

Octal addition and

subtraction

students will understand

to perform arithmetic

operations with the

numbers of radix 8

Number Systems(Hexadecimal

arithmetic)

T-1:Chapter 2

Section 2.2

RW-1

Hexadecimal addition

and subtraction

students will understand test 1 allocation

to perform arithmetic

operations with the

numbers of radix 16

Lecture 12

Number Systems(Floating point

numbers)

R-2:Chapter 1

Section 1.17

Lecture will explain the

conventional

representation of small

fractional or mixed

numbers

Students will

understand the most

common format for

representing floating

point numbers

Lecture 13

Combinational Logic System

(Truth table)

T-1:Chapter 3

Section 3.1

Lecture will explain the

three basic logic

functions AND OR and

NOT and its use to build

any combinational digital

logic circuit

Students will be able to

design the

combinational circuits

using basic gates

Combinational Logic System

(Basic logic operation)

T-1:Chapter 3

Section 3.1

Lecture will explain

basic logic operations

using simple gates and

lecture will explain the

all these basic gates in

detail

Students will be able to

design combinational

circuits by

understanding these

basic gates

Combinational Logic System

(Basic postulates)

T-1:Chapter 4

Section 4.1.1

Lecture will explain the

basic axioms of a

mathematical system

Students will

understand that how

digital abstraction will

take place

Lecture 14

mini project allocation

Week 5

Lecture 14

Combinational Logic System

(Standard representation of logic

functions -SOP forms)

T-1:Chapter 4

Section 4.3.5

Lecture will explain the

method of reducing the

complex logic expression

into simple logic

expression using SOP

reduction method

Lecture 15

Week 6

Lecture 16

Lecture 17

Lecture 18

Students will

understand how to

design digital circuits

using minimum logic

gates

Quiz,Test,Mini project 1

Combinational Logic System

(Simplification of switching

functions - K-map)

T-1:Chapter 4

Section 4.3.2

Graphical representation Input combination for

of logic function truth

any cell can be easily

table

determined and circuit

simplification

Combinational Logic System

(Quine-McCluskey tabular

methods)

T-1:Chapter 4

Section 4.4.1

Algorithm for circuit

minimization

Combinational Logic System

(Synthesis of combinational logic

circuits)

T-1:Chapter 4

Section 4.3

SW-1

Different methods of

How to design

synthesis like canonical combinational logic

SOP,POS and truth table circuits

method

Combinational Logic System

(Logic gates)

R-2:Chapter 3

Section 3.3

SW-1

all the logic gates with

truth tables and logic

symbols

Combinational Logic System

(Fundamental theorems of Boolean

algebra)

R-1:Chapter 1

Section 1.6

Representation of binary Understanding of duals

variables in letters

or boolean algebra

theorems

Combinational Logic System

(Standard representation of logic

functions POS forms)

T-1:Chapter 4

Section 4.3.6

Lecture will explain the

method of reducing the

complex logic expression

into simple logic

expression using

POSreduction method

Students will

understand how to

design digital circuits

using minimum logic

gates

Logic Families(Introduction to

different logic families)

R-1:Chapter 4

Section 4.1

Unipolar and Bipolar

Logic Families

understanding of group

of compatible ICs with

the same logic levels

and supply voltages

Logic Families(Operational

characteristics of BJT)

T-1:Chapter 3

Section 3.9.3

Characteristics of

Transistors

How to use BJTs for

designing Digital

circuits using there

characteristics

Logic Families(Operational

characteristics of MOSFET as

switch)

R-1:Chapter 3

Section 3.7

Designing of digital

switches

How to use on off logic

using MOSFETs

Logic Families(TTL inverter)

T-1:Chapter 3

Section 3.2

Not gate implementation understanding of

using TTL logic

different logic

implementation using

TTLs

Logic Families(CMOS inverter)

T-1:Chapter 3

Section 3.3.3

Not gate implementation Understand the use of

using CMOS

NMOS and PMOS for

designing different

gates

How to reduce number

of components by using

truth table

Simulation of Basic

gates on Proteus

how to implement these Simulation of Basic

logic gates in boolean gates on Proteus

expression

Week 6

Lecture 18

Logic Families(Structure and

operations of TTL gates)

R-1:Chapter 4

Section 4.8

TTL gate with totem

Design of different

pole output driver and

gates using TTL

implementation of gates

Week 7

Lecture 19

Logic Families(Electrical

characteristics of logic gates)

T-1:Chapter 3

Section 3.5

Behaviour of logic gates problems with logic

gates in real time

Logic Families(Decoders)

T-1:Chapter 5

Section 5.4

SW-1

Multiple inputs and

multiple outputs logic

circuit

How to convert coded

inputs into coded

outputs

Simulation of decoder

on proteus

Logic Families(Encoders)

T-1:Chapter 5

Section 5.5

SW-1

Coding the output of

decoder into fewer bits

like using priority

encoder

How to minimize the

output before sending

it on channel

Simulation of encoder

on proteus

Logic Families(Multiplexers)

T-1:Chapter 5

Section 5.7

SW-1

Circuits used to send

multiple inputs on a

single channel like 2

raise to the power n t0 1

MUX

Digital circuits used to Simulation of

combine the data on a multiplexer on proteus

single channel and how

to simplify the circuit

designingh

Logic Families(Demultiplexers)

T-1:Chapter 5

Section 5.7.3

Circuits used to send

single inputs on a

multiple channels after

decoding it

Digital circuits used to

separate the data and

send it on multiple

channels

Logic Families(Parity circuits)

T-1:Chapter 5

Section 5.8

Even parity and odd

parity circuits

Understanding of

different circuits that

will be used for error

correction

Logic Families(Adders)

T-1:Chapter 5

Section 5.10

SW-1

Half adder and Full

adder

How to design and

simulation of adder on

perform addition

proteus

operation in ALU using

Digital circuits

Logic Families(Subtractors)

T-1:Chapter 5

Section 5.10

SW-1

Half subtracter and full

subtracter

How to design and

Simulation of

perform subtraction

Subtractor on proteus

operation in ALU using

Digital circuits

Logic Families(ALU)

R-1:Chapter 6

Section 6.6

Block diagram of 74181 how to design ALU

using digital gates

Logic Families(Comparators)

R-1:Chapter 6

Section 6.7

2 bit and 4 bit

comparator

Logic Families(Structure and

operations of CMOS gates)

R-1:Chapter 4

Section 4.14

Lecture 20 will cover all students will be able to

the basic gates using

design any gate using

NMOS and PMOS

CMOS technology

combinations and

Lecture 21 will be

reserved for contingency

Lecture 20

Students will be able to

design comparators and

use them for

comparison of bits

Week 7

Lecture 21

Logic Families(Structure and

operations of CMOS gates)

R-1:Chapter 4

Section 4.14

Lecture 20 will cover all students will be able to

the basic gates using

design any gate using

NMOS and PMOS

CMOS technology

combinations and

Lecture 21 will be

reserved for contingency

MID-TERM

Week 8

Week 9

Week 10

Lecture 22

Sequential Logic systems

(Definition of state machines)

T-1:Chapter 7

Section 7.1

AV-1

What is state machine,

use of machine

Basics of state

machines

Lecture 23

Sequential Logic systems(State

machine as a sequential controller)

T-1:Chapter 7

Section 7.3

AV-1

application of state

machine to design

sequential circuit

How to design

sequential circuits using

state machines

Lecture 24

Sequential Logic systems(Basic

sequential circuits)

T-1:Chapter 7

Section 7.3

Lecture 25

Sequential Logic systems(SRlatch)

T-1:Chapter 7

Section 7.2.1 and

7.2.2 and 7.2.3

AV-2

Explanation of basic SR

latch

its circuits and

component and its

working

Basic working of SET

RESET LATCH,its

drawbacks and

applications

Lecture 26

Sequential Logic systems(D-latch)

T-1:Chapter 7

Section 7.2.4 and

7.2.5

AV-2

Explanation of basic D

latch circuit and its

working

How to store a single

Animation

bit of information and Quiz allocation

how to design this basic

flip flop using gates

Lecture 27

Sequential Logic systems(D flipflop)

T-1:Chapter 7

Section 7.2.5 and

7.2.6

AV-2

Explanation of D flip

flop circuit and its

working

Difference between

latch and flip flop and

its circuit

Animation

Lecture 28

Sequential Logic systems(JK flipflop)

T-1:Chapter 7

Section 7.2.9 and

7.2.10

AV-2

Explanation of JK flip

flop circuit and its

working

How to improve

drawbacks of JK Flip

Flop

Animation

Lecture 29

Sequential Logic systems(T flipflop)

T-1:Chapter 7

Section 7.2.11

AV-2

Explanation of T flip

flop circuit and its

working

Use of toggle flip flop

its applications and

working

Animation

Sequential Logic systems(Timing

hazards and races)

T-1:chapter 7 section

7.9.3

Lecture 30

Sequential Logic systems(Analysis T-1:chapter 7 section

of state machines using D flip7.4.6

flops)

Video lectures

explanation of basic

Understand the

sequential circuit and its designing of state

major component

machines like basic flip

flops

What is hazards and race Why race condition its

condition in flip flop

drawback and how to

avoid it practiaclly

Lecture 30 is for How to Designing of state

design state machine by machines using flip

using D Flip Flop and its flops

simplification

Lecture 31 is reserved

for contingency

Animation

Week 11

Lecture 31

Sequential Logic systems(Analysis T-1:chapter 7 section

of state machines using D flip7.4.6

flops)

Lecture 30 is for How to Designing of state

design state machine by machines using flip

using D Flip Flop and its flops

simplification

Lecture 31 is reserved

for contingency

Lecture 32

Lecture 33

Week 12

Week 13

Quiz,Test,Mini project 2

Sequential Logic systems(Design

of state machines)

T-1:chapter 7 section

7.5

AV-1

How to design state

applications of state

tables and state machines machines in real world

and its use in real world like in controlling the

rear lights of the car

system

Sequential Logic systems

(Designing state machine using

ASM charts)

T-1:chapter 7 section

7.12

AV-1

Introduction about

Algorithmic State

Machine

Lecture 34

Sequential Logic systems

(Designing state machine using

state diagram)

T-1:chapter 7 section

7.5

AV-1

How to design state

applications of state

tables and state machines machines in real world

and its use in real world like in controlling the

rear lights of the car

system

Lecture 35

Sequential Logic systems(Analysis T-1:chapter 7 section

of state machines using JK flip7.3.5

flops)

how to implement State

machines using JK Flip

flop or the clocked

synchronous state

machine design

what are drawbacks of

implementing state

machines using other

flip flops and how they

can be removed by

using this Flip Flop

Lecture 36

Sequential logic Application

(Multi-bit latches)

T-1:chapter 8 section

8.2.5

introduction hazard free

logic circuits

How to design latches

which can have large

number of bits

Mini Project

Submission

Lecture 37

Sequential logic Application

(Registers)

T-1:chapter 8 section

8.2.5 and 8.2.6

VL-1

How to combine two

more flip flops and give

them common clock to

design a register

to store a collection of

related bits

Virtual labs

Sequential logic Application(Shift T-1:chapter 8 section

register)

8.5

VL-1

How to design a system practical applications of Virtual labs

that will shift one bit of shift registers like in

data at each tick of clock moving displays etc

Lecture 38

Designing of Sequential

circuits using ASM

charts

Memory(Read-only memory)

R-1:chapter 14

section 14.5

ROM architecture,Types Internal structure of

and its applications

ROM with its

appliactions

Memory(read/write memory SRAM and DRAM)

R-1:chapter 14

section 14.4

basic building blocks of

RAM Cell and its

internal structure

Sequential logic Application

(Counters)

T-1:chapter 8 section

8.4

VL-1

Difference between

static and dynamic

RAM its applications

and internal structure

to design a clocked

to design counters and

sequential circuit whose use them in real time

state diagram contains a applications

single cycle

ripple,synchronous and

asynchronous counters

Virtual labs

Week 13

Week 14

Lecture 39

Lecture 40

Memory(PLAs and their

applications)

T-1:chapter 5 section

5.3

How to realize any SOP Applications and

Logic expression using designing of PLAs

two level AND OR

device

Memory(Sequential PLDs and

their applications)

T-1:chapter 8 section

8.3

Designing of Bipolar

Appliacations of PLDs

sequential PLDs and and and its designing

Sequential GAL devices

Memory(State- machine design

with sequential PLDs)

T-1:chapter 9 section

9.1

applications of PLDs in

State Machine Design

PLDs and PLAs its

difference in designing

and state machines

R-1:Chapter 12

Section 12.6

Logic cell array and its

design

how to increase the

effective size and to

add more functionality

in a single

programmable device

Memory(Introduction to field

programmable gate arrays)

Lecture 41

Memory(PALs and their

applications)

T-1:chapter 8 section

8.3.4

Lecture 41 introduction applications of PALs

to PLA , functioning and

designing and

application of PALs

Lecture 42 is reserve for

contingency

Lecture 42

Memory(PALs and their

applications)

T-1:chapter 8 section

8.3.4

Lecture 41 introduction applications of PALs

to PLA , functioning and

designing and

application of PALs

Lecture 42 is reserve for

contingency

SPILL OVER

Week 15

Lecture 43

Spill Over

Lecture 44

Spill Over

Lecture 45

Spill Over

Scheme for CA:

Component

Quiz,Test,Mini project

Frequency

Out Of

2

3

Total :-

Details of Academic Task(s)

Each Marks Total Marks

10

20

10

20

AT No.

Objective

Topic of the Academic Task

Nature of Academic Task

(group/individuals/field

work

Evaluation Mode

Allottment /

submission Week

Quiz 1

To Test Basic

Knowledge about

subject

MCQ based test. Level of question will be similar to gate.

Individual

Performance in Test

9 / 10

Test 1

To test the

knowledge about

subject

Analytical question

Individual

Performance in Test

4/5

Mini project 1

To test design skills Mini project to design digital circuit on hardware.

of students

Group size not more than 4

Group

Based on innovation

and quality

4 / 12

You might also like

- Course Outline Logic Circuits and Switching TheoryDocument2 pagesCourse Outline Logic Circuits and Switching TheorySravan KumarNo ratings yet

- HandoutDocument2 pagesHandoutAnimesh MishraNo ratings yet

- Cse 408Document7 pagesCse 408Kislay SinghNo ratings yet

- FE Exam Preparation Book VOL1 LimitedDisclosureVerDocument643 pagesFE Exam Preparation Book VOL1 LimitedDisclosureVerSuika Doreamon100% (1)

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Capstone Project Report FormatDocument5 pagesCapstone Project Report FormatHarmanWaliaNo ratings yet

- RP Tip Print NewDocument10 pagesRP Tip Print NewanakshaNo ratings yet

- DEMPDocument294 pagesDEMPLALLINo ratings yet

- Design Analysis of AlgorithmDocument8 pagesDesign Analysis of AlgorithmParinyas SinghNo ratings yet

- 15EC205 - Signals and Systems SyllabusDocument2 pages15EC205 - Signals and Systems Syllabusbashyam88No ratings yet

- Btech s7 Electrical Electro Eng 20131466834599Document38 pagesBtech s7 Electrical Electro Eng 20131466834599Nikhil EdwardNo ratings yet

- Digital Logic CircuitsDocument88 pagesDigital Logic CircuitsJenath SathikbashaNo ratings yet

- MTH212Document8 pagesMTH212Mandeep SinghNo ratings yet

- B1-5a Digital Techniques I SRDocument190 pagesB1-5a Digital Techniques I SRAlexander Mcfarlane50% (2)

- ECE CSESyllabusDocument42 pagesECE CSESyllabusVivekNo ratings yet

- Even Semester Syllabus-ICTDocument30 pagesEven Semester Syllabus-ICTemailidtofoolNo ratings yet

- GE8151 - Problem Solving & Python Programming (Ripped From Amazon Kindle Ebooks by Sai Seena)Document232 pagesGE8151 - Problem Solving & Python Programming (Ripped From Amazon Kindle Ebooks by Sai Seena)The QuranNo ratings yet

- Syl Btech EC 2014 PDFDocument122 pagesSyl Btech EC 2014 PDFnazlin sitharaNo ratings yet

- CSE CompleteDocument126 pagesCSE CompleteSameer ChandraNo ratings yet

- Francis Xavier Engineering College, Tirunelveli Department of Electronics and Communication EngineeringDocument8 pagesFrancis Xavier Engineering College, Tirunelveli Department of Electronics and Communication EngineeringImmanuel VinothNo ratings yet

- Lpu Ip of Microprocessor and Micro ControllersDocument11 pagesLpu Ip of Microprocessor and Micro ControllersMohammadAneesNo ratings yet

- UntitledDocument12 pagesUntitledSathiyaraj MurugarajNo ratings yet

- C Syl EL IV SemesterDocument15 pagesC Syl EL IV SemesterRitu SharmaNo ratings yet

- Final CSE V Semester New SyllabusDocument13 pagesFinal CSE V Semester New Syllabussaurabh303No ratings yet

- B.Tech ECE Academic Scheme and Syllabus (I-VIII SemestersDocument114 pagesB.Tech ECE Academic Scheme and Syllabus (I-VIII SemestersWaniBazillaNo ratings yet

- Anna University:: Chennai 600 025 Curriculum 2004 B.Tech. Information Technology Semester Iii Code No. Course Title L T P M TheoryDocument39 pagesAnna University:: Chennai 600 025 Curriculum 2004 B.Tech. Information Technology Semester Iii Code No. Course Title L T P M TheorySutha BalaNo ratings yet

- Signals and SystemsDocument3 pagesSignals and Systemsnisarg0% (1)

- Ece206 EDCDocument7 pagesEce206 EDCManojSharmaNo ratings yet

- STLD NotesDocument159 pagesSTLD NotesanithaNo ratings yet

- EEE241-DLD Course OutlineDocument2 pagesEEE241-DLD Course OutlineZeeshan TahirNo ratings yet

- Scheme 2009 - 13Document32 pagesScheme 2009 - 13Apoorva JagtapNo ratings yet

- 7.CS6201 - DPSDDocument160 pages7.CS6201 - DPSDNitinchandra HegadeNo ratings yet

- ECE219 Course Planner for Electronic Measurements and InstrumentationDocument10 pagesECE219 Course Planner for Electronic Measurements and InstrumentationPrinceDineshNo ratings yet

- CSE SyallbusDocument126 pagesCSE SyallbusAjay KumarNo ratings yet

- B.tech 5th Sem ECE FinalDocument13 pagesB.tech 5th Sem ECE FinalamanahmedaecNo ratings yet

- Calicut University ECE Scheme and Syllabus 2009Document132 pagesCalicut University ECE Scheme and Syllabus 2009Akhil Paul VNo ratings yet

- 4) Demp - Wase & WimsDocument8 pages4) Demp - Wase & WimsRashmitha RavichandranNo ratings yet

- RP Tip Print NewDocument8 pagesRP Tip Print NewChandan ShahNo ratings yet

- CSE322 Formal Languages and Automation Theory 17442::arun Malik 3.0 0.0 0.0 3.0 Courses With Numerical and Conceptual FocusDocument11 pagesCSE322 Formal Languages and Automation Theory 17442::arun Malik 3.0 0.0 0.0 3.0 Courses With Numerical and Conceptual FocusSunnyAroraNo ratings yet

- INSTRUCTION SET OF 8086: Data Transfer and ArithmeticDocument18 pagesINSTRUCTION SET OF 8086: Data Transfer and ArithmeticMallik KglNo ratings yet

- CIV220T Surveying 16076::vikash Sharma 4.0 1.0 0.0 5.0 Courses With Numerical and Conceptual FocusDocument10 pagesCIV220T Surveying 16076::vikash Sharma 4.0 1.0 0.0 5.0 Courses With Numerical and Conceptual Focuskaran ahariNo ratings yet

- Switching Thoery and Logic DesignDocument159 pagesSwitching Thoery and Logic DesignamarNo ratings yet

- Common To E&C, EI&C, CS&E & IS&E: Subject: Digital Electronics-1Document9 pagesCommon To E&C, EI&C, CS&E & IS&E: Subject: Digital Electronics-1Vikram RaoNo ratings yet

- School OF Information and Communication Technology: Gautam Budh Nagar, Greater NoidaDocument63 pagesSchool OF Information and Communication Technology: Gautam Budh Nagar, Greater NoidaPrashant Shukla100% (1)

- SLS Laboratory APU2F1908 PDFDocument5 pagesSLS Laboratory APU2F1908 PDFLimpei chinNo ratings yet

- B.SC Electronics Syllabi OnlyDocument5 pagesB.SC Electronics Syllabi OnlyDarrenLovelockNo ratings yet

- De Course File 2013-14Document75 pagesDe Course File 2013-14ragvshahNo ratings yet

- Digital Number SystemDocument18 pagesDigital Number SystemLeGrand BeltranNo ratings yet

- Signals and Systems Course OverviewDocument3 pagesSignals and Systems Course OverviewSeema P DiwanNo ratings yet

- Panjab University, Chandigarh: Syllabi of First Year Courses in B.E. (Computer Science and Engineering)Document32 pagesPanjab University, Chandigarh: Syllabi of First Year Courses in B.E. (Computer Science and Engineering)Anonymous t97R3yqNo ratings yet

- Teaching and Examination Scheme For Second Year Computer Science & Engineering (W.e.f. Academic Year 2009-10)Document10 pagesTeaching and Examination Scheme For Second Year Computer Science & Engineering (W.e.f. Academic Year 2009-10)VISION GAMINGNo ratings yet

- Syllabus MCA 12-15Document51 pagesSyllabus MCA 12-15Azar SheikhNo ratings yet

- BcasndtDocument38 pagesBcasndtPrakash DabhadeNo ratings yet

- Mahamaya Technical University: SyllabusDocument25 pagesMahamaya Technical University: SyllabusakttripathiNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Integer Optimization and its Computation in Emergency ManagementFrom EverandInteger Optimization and its Computation in Emergency ManagementNo ratings yet

- The Art of Assembly Language Programming Using PIC® Technology: Core FundamentalsFrom EverandThe Art of Assembly Language Programming Using PIC® Technology: Core FundamentalsNo ratings yet

- Professional Knowledge Questions Asked in Previous IBPS IT OfficerDocument10 pagesProfessional Knowledge Questions Asked in Previous IBPS IT OfficerHarmanWaliaNo ratings yet

- Cloning1Document16 pagesCloning1HarmanWaliaNo ratings yet

- CPP TutorialDocument329 pagesCPP Tutorialali veli100% (3)

- MEC109Document2 pagesMEC109HarmanWaliaNo ratings yet

- Project Status Report TemplateDocument1 pageProject Status Report TemplateHarmanWaliaNo ratings yet

- ECE131Document14 pagesECE131HarmanWaliaNo ratings yet

- Extension in Payment of FeesDocument3 pagesExtension in Payment of FeesHarmanWaliaNo ratings yet

- INT101Document8 pagesINT101HarmanWaliaNo ratings yet

- Bty 100Document2 pagesBty 100HarmanWaliaNo ratings yet

- R Programming Help FileDocument30 pagesR Programming Help FileHarmanWaliaNo ratings yet

- R Programming Help FileDocument30 pagesR Programming Help FileHarmanWaliaNo ratings yet

- Recover Lost Data with Backup MechanismsDocument35 pagesRecover Lost Data with Backup MechanismsHarmanWaliaNo ratings yet

- R Programming Help FileDocument30 pagesR Programming Help FileHarmanWaliaNo ratings yet

- Lecture10!10!18997 Interview QuestionDocument6 pagesLecture10!10!18997 Interview QuestionHarmanWaliaNo ratings yet

- LPU Biology Course Codes and DetailsDocument6 pagesLPU Biology Course Codes and DetailsHarmanWaliaNo ratings yet

- Num Sys NegativeDocument1 pageNum Sys NegativeBanarsee LalNo ratings yet

- OverflowDocument4 pagesOverflowHarmanWaliaNo ratings yet

- OverflowDocument4 pagesOverflowHarmanWaliaNo ratings yet

- Calculating The Hamming CodeDocument2 pagesCalculating The Hamming CodeHarmanWaliaNo ratings yet

- ErpDocument2 pagesErpHarmanWaliaNo ratings yet

- Number Systems and Conversions GuideDocument81 pagesNumber Systems and Conversions GuideHarmanWaliaNo ratings yet

- 23,24 HashingDocument16 pages23,24 HashingHarmanWaliaNo ratings yet

- Logic GatesDocument20 pagesLogic GatesHarmanWaliaNo ratings yet

- Quad TRI-STATE Buffer DatasheetDocument6 pagesQuad TRI-STATE Buffer Datasheet4ew018No ratings yet

- Trs Bit: Trs8Bit Trs8Bit Trs8Bit Trs8BitDocument251 pagesTrs Bit: Trs8Bit Trs8Bit Trs8Bit Trs8Bitmicros 8bitsNo ratings yet

- Oracle SPARC M5-32 Server Assessment (WBTDocument6 pagesOracle SPARC M5-32 Server Assessment (WBTRomeoNo ratings yet

- Temperature Indicator-Cum - ControllerDocument3 pagesTemperature Indicator-Cum - Controllerraghgk2012No ratings yet

- Quectel EC200U OpenCPU 系统资源信息 20210106Document19 pagesQuectel EC200U OpenCPU 系统资源信息 20210106Aaron ZhengNo ratings yet

- 2023 S1 IT1020 Lecture 03Document31 pages2023 S1 IT1020 Lecture 03Nadil NinduwaraNo ratings yet

- MBD J Jnc9f h61 ManualDocument40 pagesMBD J Jnc9f h61 ManualNewdinNo ratings yet

- DFT Interview Questions and AnswersDocument3 pagesDFT Interview Questions and AnswersJayesh PopatNo ratings yet

- DEN0001C Principles of Arm Memory MapsDocument25 pagesDEN0001C Principles of Arm Memory Mapsrysul12No ratings yet

- DG506A, DG507A, DG508A, DG509A: CMOS Analog Multiplexers FeaturesDocument19 pagesDG506A, DG507A, DG508A, DG509A: CMOS Analog Multiplexers FeaturesahmedNo ratings yet

- ES Notes PDFDocument160 pagesES Notes PDFerthineni ushaNo ratings yet

- Storage Devices 3Document29 pagesStorage Devices 3api-250921947No ratings yet

- Errata: Last Updated 5 December 2011Document4 pagesErrata: Last Updated 5 December 2011jacksparrow868No ratings yet

- Prefix-based Multi-Pattern Matching on FPGADocument2 pagesPrefix-based Multi-Pattern Matching on FPGAdanielcoding21No ratings yet

- CH 3: 8085 Instruction Set Memory and I/O InterfacingDocument85 pagesCH 3: 8085 Instruction Set Memory and I/O Interfacingabhishek310% (1)

- B.Tech Scheme for Computer Science & EngineeringDocument22 pagesB.Tech Scheme for Computer Science & EngineeringMahesh DeoNo ratings yet

- Dell Inspiron n4030 - Wistron Dj1 Calpella Uma 10212-Sb - Rev SBDocument90 pagesDell Inspiron n4030 - Wistron Dj1 Calpella Uma 10212-Sb - Rev SBRenato Araujo0% (1)

- 3eb4c Quanta r09, R09a R3a February 20 2012 SchematicsDocument58 pages3eb4c Quanta r09, R09a R3a February 20 2012 SchematicsalshameNo ratings yet

- Chapter-5-Synchronous Sequential Logic PDFDocument138 pagesChapter-5-Synchronous Sequential Logic PDFVINU ABRAHAMNo ratings yet

- From Sand To CircuitsDocument4 pagesFrom Sand To CircuitsdkishoreNo ratings yet

- Xilinx Device DriversDocument1,305 pagesXilinx Device DriversVikramNo ratings yet

- Pic 17cxxxDocument37 pagesPic 17cxxxankitguttu1No ratings yet

- Mpi LabDocument2 pagesMpi LabNanda KishoreNo ratings yet

- Design and Implementation of Ripple Carry Adder Using Area Efficient Full Adder Cell in 180nm CMOS TechnologyDocument6 pagesDesign and Implementation of Ripple Carry Adder Using Area Efficient Full Adder Cell in 180nm CMOS TechnologySushmaNo ratings yet

- Ads1115 PDFDocument36 pagesAds1115 PDFAnonymous pKKgYelNNo ratings yet

- July 2011 Rectron PE Price GuideDocument29 pagesJuly 2011 Rectron PE Price GuidepietervanschalkNo ratings yet

- Seeed OPL For Customer 20151021Document104 pagesSeeed OPL For Customer 20151021gobinathNo ratings yet

- Processor Performance EnhancementDocument3 pagesProcessor Performance EnhancementSheraz AliNo ratings yet

- Cs 2 PracticalsDocument61 pagesCs 2 PracticalsArya RanawareNo ratings yet