Professional Documents

Culture Documents

HVDC LCC

Uploaded by

sf1110 ratings0% found this document useful (0 votes)

140 views3 pagesA simple introduction on HVDC LCC

Original Title

HVDC_LCC

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentA simple introduction on HVDC LCC

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

140 views3 pagesHVDC LCC

Uploaded by

sf111A simple introduction on HVDC LCC

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 3

HVDC LCC Modelling

DIgSILENT PowerFactory

Abstract

This paper discusses the modelling of HighVoltage Direct Current (HVDC) Transmission Systems, in particular line-commutated

(LCC) technology, for the purpose of load

flow and time-domain simulation.

Content

This document presents a model of a HVDC

system. A few simulations are performed

and the results are discussed. The simulations show the steady-state effect of tap

changing commutation transformers, as well

as the transient response to faults in the AC

network on both sides of the HVDC system.

Model for

operation

steady-state

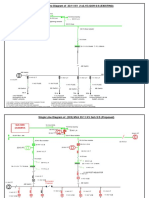

The model is based on the IEEE benchmark

model [1]. It has been constructed in DIgSILENT PowerFactory version 15.0 and is contained in the file HVDC Example.pfd. The

single line diagram of the system as implemented in PowerFactory is shown in Figure

1.

The system has twelve-pulse thyristor converters on both the rectifier and inverter side.

The 500 kV DC line has a length of 500

km and is rated at 2 kA. If the study case

0 BaseCase is activated and a load flow

DIgSILENT

GmbH, Heinrich-Hertz-Str. 9, 72810

Gomaringen, Germany, www.digsilent.de

DIgSILENT PowerFactory, r996

calculation performed, the user may observe

that approximately 1000 MW flows through

the DC link. The rectifiers set the DC current

to 2 kA and the inverters set the DC voltage

to 99%. The converter models include commutation transformers, which provide the 30

degree phase shift in AC voltage between

the upper and lower converters. The transformers include tap changers, which, initially,

have fixed positions of 1.01 on the rectifier

side and 0.989 on the inverter side. The resulting voltage ratio leads to a firing angle of

= 15.2 on the rectifier side and = 14.6

on the inverters side. The overlap angle on

the inverter side is 23.6 . The model also includes harmonic filters. In the load-flow calculation these harmonic filters can be seen

to compensate the reactive power consumption of the converters.

The study case 1 TapControl can be activated to demonstrate the effect of automatic

tap changers (installed in the commutation

transformers) on the steady-state operation.

The settings of the tap changers can be seen

under the load flow tab of the converters dialogue windows. The tap positions on the rectifier side are set so that the firing angle is

= 15 . The tap positions on the inverter side

are set so as to lead to an extinction angle of

= 20 . For the purpose of testing the tap

changers the initial tap positions have been

set to 0.95 on all converters.

Model for time-domain

simulation

The converter model used for the EMTsimulation reproduces the transients due to

the six thyristor switches and their snubber

HVDC LCC Modelling

circuits. Either a built-in firing controller or

a user-defined firing controller can be used.

The built-in firing controller represents EPC

(equidistant firing control). The firing angle

is measured relative to an internal synchronising angle phiref, which varies at the rate

of the frequency signal that is connected to

the converter model. The frequency is measured by a phase-locked loop (PLL). The

model requires the commutation reactance

to be entered correctly so that the internal

angle phiref can be initialised correctly.

When either the study case 2. . . or 3. . . is

activated then the variations HVDC Control

and Lower SCR are activated. The former links dynamic controllers to the converter models and the latter modifies the

short-circuit levels of the external AC grid elements.

The graphic HVDC Controls provides

an overview of the controls.

It shows

how the converter models are linked with

the dynamic controller models, phasemeasurement devices and voltage & current

measurement devices.

The graphic Rect Controller shows the dynamic model of the rectifier controller. Under normal conditions, this controller regulates the DC current to the reference Id ref,

which is calculated from the load flow solution.

In the event of a severe drop

in the DC voltage the current reference

is reduced through the VDCOL (voltagedependent current-order limiter).

The graphic Inv Controller shows the dynamic model of the inverter controller. Under normal conditions the controller regulates the extinction angle to gamma min,

which is obtained from the load flow solution. In the event of a severe reduction in DC

voltage the controller can switch to currentcontrol mode. In this case the inverter regulates the DC current (to the initial current less

the margin, Im).

Fault at the inverter side

The study case 2 Fault InverterSide is

used to study the response of the HVDC

system to a three-phase short circuit in the

DIgSILENT PowerFactory, r996

AC system on the inverter side using a timedomain simulation (EMT).

After running the EMT simulation the simulation plots appear in the graphics named

. . . . The inverter phase currents in the

graphic AC Waveforms display thyristor

commutation failures (see Figure 2). The

graphic Rec Ctrl shows that the VDCOL is

activated during the fault due to the reduction

in the DC voltage. The rectifier controller reduces the DC current and alleviates the commutation problems on the inverter side.

Fault at the rectifier side

The study case 3 Fault Rectifier Side is

used to study the response of the HVDC system to a three-phase short circuit in the AC

system on the rectifier side. The response

is studied using a time-domain simulation

(EMT).

After running the EMT simulation the plots

appear in the graphics named . . . . The

firing angle on the rectifier side reduces to

the minimum value of 5 degrees, but the rectifier controller is unable to regulate the current to its set-point. The inverter controller

switches to current control mode (see Figure

3). The inverter controller has a reference

current equal to 90% (the initial 100% less

a 10% margin). The inverter controller prevents the HVDC system from running down.

When the fault clears the rectifier controller

takes over current control again. After some

time the inverter controller switches back to

extinction-angle control.

References

[1] M. Szechtman, T. Wess, and C.V. Thio.

A benchmark model for HVDC system

studies. In International Conference on

AC and DC Power Transmission, pages

374378. IET, 1991.

HVDC LCC Modelling

Figure 1: Single line diagram for the HVDC system as modelled in PowerFactory

Figure 2: Commutation failure

Figure 3: Current control at the inverter

DIgSILENT PowerFactory, r996

You might also like

- 33 11KV Substation SLDDocument3 pages33 11KV Substation SLDRajeshYadav100% (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Sungazing Protocol: How to Practice Hira Ratan Manek's Sun Energy MethodDocument3 pagesSungazing Protocol: How to Practice Hira Ratan Manek's Sun Energy Methodparra7No ratings yet

- CCIOM, Diagnostic Trouble CodesDocument6 pagesCCIOM, Diagnostic Trouble CodesHari Hara Suthan80% (5)

- BuckConverter Design Jpe10Document13 pagesBuckConverter Design Jpe10joviflocasNo ratings yet

- Rosa 1908Document44 pagesRosa 1908joaomonterosNo ratings yet

- IET Wiring Regulations BS 7671 18th Edition: Transient Overvoltage ProtectionDocument20 pagesIET Wiring Regulations BS 7671 18th Edition: Transient Overvoltage ProtectionJackNo ratings yet

- IET Wiring Regulations BS 7671 18th Edition: Transient Overvoltage ProtectionDocument20 pagesIET Wiring Regulations BS 7671 18th Edition: Transient Overvoltage ProtectionJackNo ratings yet

- Laundry Engineering and Planning HandbookDocument343 pagesLaundry Engineering and Planning HandbookKhanh mai quocNo ratings yet

- Important Questions - APS - IDocument3 pagesImportant Questions - APS - IAakash MehtaNo ratings yet

- LCC HVDCDocument7 pagesLCC HVDCSubbu ChNo ratings yet

- IEEE Standard For The Specification of Microgrid ControllersDocument43 pagesIEEE Standard For The Specification of Microgrid Controllerssf111No ratings yet

- Ch-5 Sheet Metal OperationDocument20 pagesCh-5 Sheet Metal OperationJAYANT KUMARNo ratings yet

- Comparison Between LCC and VSCDocument5 pagesComparison Between LCC and VSCijsretNo ratings yet

- Frequency Stabilization in TransmissionDocument9 pagesFrequency Stabilization in Transmissionsf111No ratings yet

- VSC-Based HVDC Link: To Allow Further Modifications To The Original System. This Model ShownDocument38 pagesVSC-Based HVDC Link: To Allow Further Modifications To The Original System. This Model ShownleslyNo ratings yet

- ABB 2493 Is Limiter GB NewBrandingDocument20 pagesABB 2493 Is Limiter GB NewBrandingsf111No ratings yet

- Fault Reduction Strategy using Neutral Earth Resistor Installation (NERIDocument15 pagesFault Reduction Strategy using Neutral Earth Resistor Installation (NERIYume YumeNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- UPEC2010 Review Voltage Control Techniques Networks Distributed Generations OLTC TransformersDocument6 pagesUPEC2010 Review Voltage Control Techniques Networks Distributed Generations OLTC Transformersstrange_kid82No ratings yet

- 29B - Acid Gas Removal TechnologyDocument17 pages29B - Acid Gas Removal Technologyarlucky5459100% (1)

- HVDC LCC Modelling: Digsilent PowerfactoryDocument3 pagesHVDC LCC Modelling: Digsilent Powerfactorybeimar heredia saiguaNo ratings yet

- Design and Implementation of Parallel Connected DC-DC Buck ConvertersDocument6 pagesDesign and Implementation of Parallel Connected DC-DC Buck ConvertersIJARTETNo ratings yet

- Slidin Mode Research PaperDocument33 pagesSlidin Mode Research PaperAnimesh JainNo ratings yet

- Thyristor Based HVDC SystemDocument5 pagesThyristor Based HVDC SystemAnonymous hzXy93FAE0% (1)

- Ieee Current ModeDocument7 pagesIeee Current ModepqqpNo ratings yet

- Design and Implementation Three-Arms Rectifier Inverter of A Single PhaseDocument6 pagesDesign and Implementation Three-Arms Rectifier Inverter of A Single Phasecelo81No ratings yet

- Multipulse Converters and Controls For HVDC and FACTS SystemsDocument9 pagesMultipulse Converters and Controls For HVDC and FACTS SystemssanjusNo ratings yet

- Matrix Converter - ReportDocument31 pagesMatrix Converter - ReportAmal P Nirmal100% (2)

- Implementation of LCC HVDC Converter TransformerDocument6 pagesImplementation of LCC HVDC Converter Transformerdhuamani01No ratings yet

- HVDC Unit IIDocument20 pagesHVDC Unit IISaduMunisekharNo ratings yet

- Flow Analysis and Calculation of AC/DC Power System Based On MATLAB and PSASPDocument6 pagesFlow Analysis and Calculation of AC/DC Power System Based On MATLAB and PSASPAbdulrahmanNo ratings yet

- Modelling Bidirectional Buck BoostDocument7 pagesModelling Bidirectional Buck BoostAkay HanafiahNo ratings yet

- Unit 4Document15 pagesUnit 4prashantpnd07100% (2)

- Performance Estimation of Tristate DC-DC Buck Converter With Fixed Frequency and Constant Switching Hysteresis ControlDocument10 pagesPerformance Estimation of Tristate DC-DC Buck Converter With Fixed Frequency and Constant Switching Hysteresis ControleditorijaiemNo ratings yet

- Family Controller PFCDocument8 pagesFamily Controller PFCWesley de PaulaNo ratings yet

- Unit-2-Converter and HVDC System ControlDocument14 pagesUnit-2-Converter and HVDC System ControlT shivaprasadNo ratings yet

- Modelado DC DCDocument8 pagesModelado DC DCAndrés Vanegas GuillénNo ratings yet

- Control of HVDCDocument38 pagesControl of HVDCPrasanna Kumar100% (2)

- A Novel Filter Design For Output LC Filters of PWM InverterDocument8 pagesA Novel Filter Design For Output LC Filters of PWM InverterSTQ137No ratings yet

- A Modern Self-Defined Extinction AngleDocument8 pagesA Modern Self-Defined Extinction AngleSofarsogoodsowhat JgnNeNo ratings yet

- Unit-2-Converter and HVDC System ControlDocument13 pagesUnit-2-Converter and HVDC System Controlravikumar_ranganNo ratings yet

- Modelling and Control of a Flying-Capacitor InverterDocument9 pagesModelling and Control of a Flying-Capacitor InverterMariem KammounNo ratings yet

- Sensorless Current Mode ControlDocument6 pagesSensorless Current Mode Controlsumiths32No ratings yet

- AC Circuit Modeling of Switching Power ConvertersDocument65 pagesAC Circuit Modeling of Switching Power Convertershey_gluppyNo ratings yet

- Model Predictive Current Control For High-Power Grid-Connected Converters With Output LCL FilterDocument6 pagesModel Predictive Current Control For High-Power Grid-Connected Converters With Output LCL FilterAndreeaNo ratings yet

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocument5 pagesImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNo ratings yet

- Control VectorialDocument6 pagesControl VectorialdanipedoNo ratings yet

- 240 Power systems electromagnetic transients simulationDocument14 pages240 Power systems electromagnetic transients simulationkjfenNo ratings yet

- Analysis and Modeling of Digital Peak Current Mode ControlDocument6 pagesAnalysis and Modeling of Digital Peak Current Mode Controltinhmaixatoi2006No ratings yet

- 6 Michal KNAPCZYK Krzysztof PIENKOWSKI 2 PDFDocument16 pages6 Michal KNAPCZYK Krzysztof PIENKOWSKI 2 PDFDevendra HoleyNo ratings yet

- DC Voltage Control and Stability Analysis of PWM-voltage-type Reversible RectifiersDocument12 pagesDC Voltage Control and Stability Analysis of PWM-voltage-type Reversible RectifiersAli ErNo ratings yet

- An Electromagnetic Transient Simulation Model ForDocument4 pagesAn Electromagnetic Transient Simulation Model ForMohit Kumar ChowdaryNo ratings yet

- Adv Power ElectronicsDocument5 pagesAdv Power ElectronicsSumon DharaNo ratings yet

- Applying PWM to Control Overcurrents at Unbalanced Faults of Forced-Commutated VSCsDocument6 pagesApplying PWM to Control Overcurrents at Unbalanced Faults of Forced-Commutated VSCsJULFANRI SIRAITNo ratings yet

- PWM Rectifier Sliding Mode Control AnalysisDocument12 pagesPWM Rectifier Sliding Mode Control AnalysisMahmoud FawziNo ratings yet

- HVDC Control Principle ExplanationDocument12 pagesHVDC Control Principle ExplanationrasashpujNo ratings yet

- Converter Modeling EL - 18 - 1 - 06Document7 pagesConverter Modeling EL - 18 - 1 - 06sf111No ratings yet

- Design of Fuzzy Sliding Mode Control For DC-DC ConverterDocument6 pagesDesign of Fuzzy Sliding Mode Control For DC-DC ConverterXime Mendez FloresNo ratings yet

- Conv DC-DC Paper ENglishDocument5 pagesConv DC-DC Paper ENglishpepe890305No ratings yet

- Self 4Document8 pagesSelf 4ShenbagalakshmiNo ratings yet

- HVDC Link Fault Impacts Turbine GeneratorDocument8 pagesHVDC Link Fault Impacts Turbine GeneratorMuhammad ArifinNo ratings yet

- Aredes2001 Article MultipulseConvertersAndControlDocument9 pagesAredes2001 Article MultipulseConvertersAndControlAbhay KotnalaNo ratings yet

- A Novel Control Strategy of Indirect Matrix ConverDocument10 pagesA Novel Control Strategy of Indirect Matrix Convermạnh phanNo ratings yet

- EEE 1105 011 Comparison of The Effects of Phase To Ground FaultsDocument7 pagesEEE 1105 011 Comparison of The Effects of Phase To Ground FaultsFAKEIDS421No ratings yet

- Novel Control for Direct Interface Converters in DC and AC Power SuppliesDocument10 pagesNovel Control for Direct Interface Converters in DC and AC Power SuppliesSherif M. DabourNo ratings yet

- A Novel Sensorless Sliding Mode Control Strategy For DC To DC Converters: Analysis, Modeling and SimulationDocument5 pagesA Novel Sensorless Sliding Mode Control Strategy For DC To DC Converters: Analysis, Modeling and Simulationiamalways05No ratings yet

- An-1048 (1) BLDC Driver LossDocument9 pagesAn-1048 (1) BLDC Driver LossDeepa DevarajNo ratings yet

- Direct Digital Control of Single-Phase AC/DC PWM Converter SystemDocument10 pagesDirect Digital Control of Single-Phase AC/DC PWM Converter SystemPham LongNo ratings yet

- TechRef RectifierDocument28 pagesTechRef RectifierАлишер ГалиевNo ratings yet

- Design and Analysis of 24 Pulse Ac-Dc Converter: May 2015, Volume 2, Issue 5 JETIR (ISSN-2349-5162)Document8 pagesDesign and Analysis of 24 Pulse Ac-Dc Converter: May 2015, Volume 2, Issue 5 JETIR (ISSN-2349-5162)anuragpugaliaNo ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Some Power Electronics Case Studies Using Matlab Simpowersystem BlocksetFrom EverandSome Power Electronics Case Studies Using Matlab Simpowersystem BlocksetNo ratings yet

- Energy Rating: Property TypeDocument6 pagesEnergy Rating: Property Typesf111No ratings yet

- Generic Microgrid Controller SpecificationsDocument43 pagesGeneric Microgrid Controller Specificationssf111No ratings yet

- NIPS 2005 Assessing Approximations For Gaussian Process Classification PaperDocument8 pagesNIPS 2005 Assessing Approximations For Gaussian Process Classification Papersf111No ratings yet

- Gaussian Processes For Regression: A TutorialDocument7 pagesGaussian Processes For Regression: A Tutorialsf111No ratings yet

- Microgrid A Conceptual Solution - 01354758Document6 pagesMicrogrid A Conceptual Solution - 01354758sf111No ratings yet

- Clarifying Grid Code Fast Fault Current Injection RequirementsDocument8 pagesClarifying Grid Code Fast Fault Current Injection Requirementssf111No ratings yet

- PG&E Microgrid Program ApprovedDocument89 pagesPG&E Microgrid Program Approvedsf111No ratings yet

- Simple Representation of Dynamic Hysteresis Losses in Power TransformersDocument8 pagesSimple Representation of Dynamic Hysteresis Losses in Power Transformerssf111No ratings yet

- Harmonic Analysis: Registration InformationDocument2 pagesHarmonic Analysis: Registration Informationsf111No ratings yet

- Grid-Connected Power ConditionerDocument6 pagesGrid-Connected Power Conditionersf111No ratings yet

- Optiplex-7010 Owner's Manual2 En-UsDocument60 pagesOptiplex-7010 Owner's Manual2 En-Ussf111No ratings yet

- Swedish Neutral Neutral Earthing Resistor Specification PDFDocument12 pagesSwedish Neutral Neutral Earthing Resistor Specification PDFRazvan CostacheNo ratings yet

- Electra 028Document27 pagesElectra 028sf111No ratings yet

- PVS980 Product OverviewDocument51 pagesPVS980 Product Overviewsf111No ratings yet

- Par Syn GenDocument14 pagesPar Syn GenRafael RoratoNo ratings yet

- ICC C35D: Sheath Bonding of Multi-Conductor / Parallel CircuitsDocument24 pagesICC C35D: Sheath Bonding of Multi-Conductor / Parallel Circuitssf111No ratings yet

- Par Syn GenDocument14 pagesPar Syn GenRafael RoratoNo ratings yet

- Power Abb DrivesDocument16 pagesPower Abb Drivessf111No ratings yet

- Brugg Cables User GuideDocument27 pagesBrugg Cables User GuideMehdi_Mashayekhi_172No ratings yet

- Bath Installation GuideDocument4 pagesBath Installation Guidesf111No ratings yet

- Optimization of VoltageDocument6 pagesOptimization of Voltagesf111No ratings yet

- P54439EP - Drawings PDFDocument4 pagesP54439EP - Drawings PDFsf111No ratings yet

- 9 Ashwani Power System State Estimation PDFDocument54 pages9 Ashwani Power System State Estimation PDFsf111No ratings yet

- Alternating Current TechnologyDocument118 pagesAlternating Current TechnologyMadhav DeshpandeNo ratings yet

- An Impedance Source Multi-Level Three Phase Inverter With Common Mode Voltage Elimination and Dead Time CompensationDocument18 pagesAn Impedance Source Multi-Level Three Phase Inverter With Common Mode Voltage Elimination and Dead Time CompensationRadu GodinaNo ratings yet

- Geo 2002Document24 pagesGeo 2002Jennifer WatsonNo ratings yet

- Vdocuments - MX - Api 612 Latest Edition 612 Latest Editionpdf Free Download Here Api Standard PDFDocument2 pagesVdocuments - MX - Api 612 Latest Edition 612 Latest Editionpdf Free Download Here Api Standard PDFNeeraj JangidNo ratings yet

- Magnets Test 3rd GradeDocument4 pagesMagnets Test 3rd Gradeapi-33371151667% (3)

- Klauke - Different Crimping MethodsDocument4 pagesKlauke - Different Crimping MethodsBiplab PaulNo ratings yet

- Rwu90 SpecsDocument2 pagesRwu90 SpecsEduardo LuboNo ratings yet

- Exercise-01 Check Your Grasp: O CH HO HODocument7 pagesExercise-01 Check Your Grasp: O CH HO HOChesta MalhotraNo ratings yet

- Transient Stability Improvement of Power System Using UpfcDocument18 pagesTransient Stability Improvement of Power System Using UpfcMuhammadWaqarNo ratings yet

- 9 Electronics TDocument44 pages9 Electronics TBieonWongNo ratings yet

- Unit GC2 Element 6 - InternationalDocument14 pagesUnit GC2 Element 6 - InternationalSatya NaiduNo ratings yet

- Research Commercial CenterDocument100 pagesResearch Commercial CenterMia S. RetomeNo ratings yet

- LM 3900Document16 pagesLM 3900Fredy CasillaNo ratings yet

- MMTDocument36 pagesMMTAvoyNo ratings yet

- Automatic Water Tank Level Controller Motor Driver Circuit - Engineering Project Without Microcontroller - Circuits Gallery PDFDocument29 pagesAutomatic Water Tank Level Controller Motor Driver Circuit - Engineering Project Without Microcontroller - Circuits Gallery PDFEi Po Po AungNo ratings yet

- Module 2Document79 pagesModule 2uditNo ratings yet

- Pump QuotationsDocument3 pagesPump Quotationsdibyendu65No ratings yet

- CV Nur Atikah ShaariDocument2 pagesCV Nur Atikah ShaariMuhammad Khairuna SyahPutraNo ratings yet

- Convair Traveler Vol. X 1958-59Document180 pagesConvair Traveler Vol. X 1958-59TateNo ratings yet

- Chemical Kinetics: Practice ExamplesDocument31 pagesChemical Kinetics: Practice ExamplesJudith Del Valle MorejonNo ratings yet

- Sugar Industry in Pakistan (17-UGLC-650)Document16 pagesSugar Industry in Pakistan (17-UGLC-650)Waqar IbrahimNo ratings yet

- Cast Resin Transformers for Distribution, Rectification, Traction and Special SolutionsDocument80 pagesCast Resin Transformers for Distribution, Rectification, Traction and Special SolutionsQUANGNo ratings yet

- Calibrar Slide Valve y Slid Stop en Compresor NH3Document4 pagesCalibrar Slide Valve y Slid Stop en Compresor NH3Hector0412No ratings yet

- Siemens SSA31.04 PDFDocument6 pagesSiemens SSA31.04 PDFJohn DunbarNo ratings yet