Professional Documents

Culture Documents

Designing of Efficient FPGA Based Random Number Generators Using VHDL.

Uploaded by

IJAFRCOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Designing of Efficient FPGA Based Random Number Generators Using VHDL.

Uploaded by

IJAFRCCopyright:

Available Formats

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

Designing Of Efficient FPGA Based Random Number Generators

Using VHDL.

Mr. P.A.Deshmukh

Prof. D. R. Dandekar

Prof. Mrs. Y. A. Sadawarte

P.G.Student

Associate Professor

Assistant professor

B.D.C.O.E,SEVAGRAM,WARDHA

B.D.C.O.E,SEVAGRAM,WARDHA

B.D.C.O.E,SEVAGRAM,WARDHA

Pritish.Deshmukh23@gmail.com , d.dandekar@rediffmail.com, Y_sadawarte@rediffmail.com.

ABSTRACT

Random Number Generator is an electronic circuit or it can be software or can be optimized

architecture. In many practical applications such as cryptography, model simulation, sampling,

games of chance, numerical analysis, there is a need of the generation of series of random

number. This is achieved for ex. by means of tables, specific algorithms or electronic circuits. This

Random number can be generated by either specific software or a FPGA based architectures. Field

Programmable Gate Array (FPGA) optimized random number generator (RNG) are more resource

efficient than software optimized RNG because they can take the advantage of bitwise operations

and FPGA specific features. Hence for generation of random number, FPGA architecture is

generally used. By using different FPGA platform, random number can be generated. There are

several algorithms by which the random number has been generated. Each algorithm had used a

different FPGA platform for generation of random number. In this paper generation of 8, 16, 256

bit random number by means of four method i.e. EX-OR Shift method, Fibonacci series method,

Galois liner feedback shift register method and Blum Blum Shub method. Moreover for analysis

Altera platform is used i.e. for simulation Modelsim software and for synthesis Quartus II

software is used. Hence by using these four algorithms, random numbers have been generated

and each algorithm has shown different performance parameters i.e. area, speed and power.

Index TermsRandom number generator RNG, Field programmable gate array FPGA, Linear

Feedback Shift Register LFSR,

I.

INTRODUCTION

Random Number Generator is an electronic circuit or it can be software or can be optimized architecture.

In many practical applications such as cryptography, model simulation, sampling, games of chance,

numerical analysis, there is a need of the generation of series of random number. This is achieved for ex.

by means of tables, specific Algorithm or electronic circuits. Moreover there are again some FPGA

architecture by which we can generate the series of random number. Each algorithm uses a different

FPGA platform and the random number can be generated. FPGA optimized RNG are more resource

efficient than Software optimized RNG because they can take Advantages of bitwise operation and FPGA

specific features These FPGA architectures shows huge performance in terms of area and speed. In this

paper the 8 bit random number is generated by two methods i.e. Fibonacci series method and Galois liner

feedback shift register method..

II. INTRODUCTION ABOUT LINEAR FEEDBACK SHIFT REGISTER

63 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

In computing, a linear feedback shift register (LFSR) is a shift register whose input bit is a linear function

of its previous state. The most commonly used linear function of single bits is XOR. The initial value of the

LFSR is called the seed, and because the operation of the register is deterministic, the stream of values

produced by the register is completely determined by its current (or previous) state. Likewise, because

the register has a finite number of possible states, it must eventually enter a repeating cycle. However, an

LFSR with a well-chosen feedback function can produce a sequence of bits which appears random and

which has a very long cycle Applications of LFSRs include generating pseudo-random numbers, pseudonoise sequences, fast digital counters and whitening sequences

Figure 1. Block Diagram of Basic Linear Feedback Shift Register

III. PSEUDO-RANDOM NUMBER GENERATOR BASED ON FIBONACCI SERIES METHOD

The Bit positions that affect the next state are called the taps. In the diagram the taps are [7, 6, 4, 3] .The

rightmost bit of the LFSR is called the output bit. The taps are XOR'd sequentially with the output bit and

then fed back into the leftmost bit. The sequence of bits in the rightmost position is called the output

stream.

A maximum length LFSR produces an m-sequence i.e. it cycles through all possible 2n - 1 state. The

sequence of numbers generated by an LFSR can be considered a binary numeral system just as valid as

Gray code or the natural binary code. The arrangement of taps for feedback in an LFSR can be expressed

in finite field arithmetic as a polynomial mod

Figure 2. Block Diagram of Fibonacci Series Method

This means that the coefficients of the polynomial must be 1's or 0's. This is called the feedback

polynomial or reciprocal characteristic polynomial. For example, if the taps are at the 7th, 6th, 4th and

3th bits (as shown), the feedback polynomial is X7+ x6 + x4 + x3 +1. The 'one' in the polynomial does not

correspond to a tap it corresponds to the input to the first bit (i.e. x0, which is equivalent to 1).

64 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

The powers of the terms represent the tapped bits, counting from the left. The first and last bits are

always connected as an input and output tap respectively.

i.The LFSR is maximal-length if and only if the corresponding feedback polynomial is primitive. This

means that the following conditions are necessary (but not sufficient):

ii.The number of taps should be even.

iii.The set of taps taken all together, not pair wise (i.e. as pairs of elements) must be relatively

prime. In other words, there must be no divisor other than 1 common to all taps.

IV.PSEUDO-RANDOM NUMBER GENERATOR BASED ON GALOIS LFSR METHOD

In the Galois configuration, when the system is clocked, bits that are not taps are shifted one position to

the right unchanged. The taps, on the other hand, are XOR'd with the output bit before they are stored in

the next position. The new output bit is the next input bit.

The effect of this is that when the output bit is zero all the bits in the register shift to the right unchanged,

and the input bit becomes zero.

Figure 3 Block Diagram of Galois LFSR Method

When the output bit is one, the bits in the tap positions all flip (if they are 0, they become 1, and if they

are 1, they become 0), and then the entire register is shifted to the right and the input bit becomes 1.

Galois LFSRs do not concatenate every tap to produce the new input (the XOR'ing is done within the LFSR

and no XOR gates are run in serial, therefore the propagation times are reduced to that of one XOR rather

than a whole chain), thus it is possible for each tap to be computed in parallel, increasing the speed of

execution.

In a software implementation of an LFSR, the Galois form is more efficient as the XOR operations can be

implemented a word at a time: only the output bit must be examined individually.

V.PSEUDO-RANDOM NUMBER GENERATOR BASED ON EX-OR SHIFT METHOD

In computing, a linear feedback shift register (LFSR) is a shift register whose input bit is a linear function

of its previous state. The most commonly used linear function of single bits is XOR.

Thus, an LFSR is most often a shift register whose input bit is driven by the exclusive-or (XOR) of some

bits of the overall shift register value. The Bit positions that affect the next state are called the taps. In the

diagram, the taps is only at [7]. The rightmost bit of the LFSR is called the output bit.

65 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

The taps are XOR'd sequentially with the output bit and then fed back into the leftmost bit. The sequence

of bits in the rightmost position is called the output stream.

Figure 4. Block Diagram of EX-OR SHIFT Method

The sequence of numbers generated by an LFSR can be considered a binary numeral system just as valid

as Gray code or the natural binary code. The arrangement of taps for feedback in an LFSR can be

expressed in finite field arithmetic as a polynomial. This means that the coefficients of the polynomial

must be 1's or 0's. This is called the feedback polynomial or reciprocal characteristic polynomial

For example, if the taps are at the 7th (as shown),the feedback polynomial is X7+1. The 'one' in the

polynomial does not correspond to a tap it corresponds to the input to the first bit (i.e. x0, which is

equivalent to 1).

VI.PSEUDO-RANDOM NUMBER GENERATOR BASED ON BLUM BLUM SHUB METHOD

Blum Blum Shub (B.B.S.) is a pseudorandom number generator proposed in 1986 by Lenore Blum,

Manuel Blum and Michael Shub that is derived from Michael O. Rabin's oblivious transfer mapping. Blum

Blum Shub takes the form Xn+1`= Xn2 Mod M

where M = pq is the product of two large primes p and q. At each step of the of the algorithm, some

output is derived from Xn+1, the output is commonly either the bit parity of Xn+1 or one or more of the

least significant bits of Xn+1.

Figure 5. Block Diagram of BLUM BLUM SHUB Method

The main property of the BBS generator is that it is proven to be next-bit unpredictable to the left and to

the right, if the prime factors of a large integer N are unknown. Consequently, the security of the

generator is based on the intractability of factoring large integers, which is also used in the encryption

scheme. Next bit unpredictability to the right (to the left) means that for every positive polynomial p and

for sufficiently large m the following condition holds The seed x0 should be an integer that is co-prime to

M (i.e. p and q are not factors of x0) and not 1 or 0. If m-1 consecutive output bits are known, then for

66 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

every polynomial-time algorithm, it is impossible to guess the next output bit with a probability larger

than 1.

The BBS generator is quite slow, but due to the characteristic explained above, it is recommended for

cryptographic tasks which only need a small amount of random numbers

VII.APPLICATION OF RANDOM NUMBER GENERATOR AS SCRAMBLER AND DESCRAMBER

A scrambler is a device which transposes signals or encodes a message at the transmitter to make the

message unintelligible at a receiver. Scrambling is accomplished by the addition of components to the

original signal or the changing of some important components of the original signal in order to make

extraction of the original signal difficult

Figure 6. Block Diagram of SCRAMBLER and DESCRAMBLER

In the transmitter, a pseudorandom cipher sequence is added (modulo 2) to the data (or control)

sequence to produce a scrambled data (or control) sequence. In the receiver, the same pseudorandom

cipher sequence is subtracted (modulo 2) from the scrambled data (or control) sequence to recover the

transmitted data (or control) sequence. A receiver descrambles the received data or control sequence by

subtracting the same pseudorandom cipher sequence used for scrambling.

Since the subtraction is modulo 2, this is equivalent to adding the pseudorandom cipher sequence i.e. the

procedure is identical to that used for scrambling in the transmitter. The receiver must ensure that the

state of the descrambler register is synchronized with that of the scrambler register.

In the above application i.e. Scrambler and Descrambler, whatever random number have input as a plain

text in the scrambler, the same plain text in the form of random sequence is getting at the receiver I.e.

descrambler. Hence functionality of scrambler and descrambler is verified.

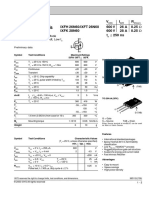

VIII. RESULT ANALYSIS

For simulation and synthesis of the algorithm Altera platform is used, Modelsim software is used for

simulation of the four methods and for synthesis, Quartus II software is used. In that Quartus II 9.1 build

350 03/24 /2010 SP 2 SJ web edition version is used. Moreover the family is cyclone II and the device is

EP2C20F484C7 is used.

67 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

30

25

20

15

10

5

0

Device Utilization Summary

Power Dissipation

Propagation Delay

EX-OR Shift

Method

Fibonacci

Series

Galois

Method

Blum Blum

Shub

Graph 1. Graphical Representations of Different Architectures for 8 Bit

In Graph 1, the comparison for 8 bit for different architectures has been shown. In that as per

comparison, Galois LFSR architecture has less device utilization summary, less power dissipation and less

propagation delay. Hence Galois Architecture is found efficient for 8 bit random number generation.

In Graph 2, The comparison for 16 bit for different architectures has been shown. In that as per

comparison, Galois LFSR architecture have less device utilization summary, less power dissipation and

less propagation delay. Hence Galois LFSR Architecture is found efficient for 16 bit random number

generation.

60

50

40

Device Utilization Summary

30

20

Power Dissipation

10

Propagation Delay

0

EX-OR Shift

Method

Fibonacci Series Galois Method

Method

Blum Blum

Shub Method

Graph 2. Graphical Representations of Different Architectures for 16 Bit

In Graph 3, the comparison for 256 bit for different architectures has been shown. Thus for synthesizing

for 256 bit, each architecture showing different device utilization summary, propagation delay and power

dissipation.

68 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

300

250

Device

Utilization

Summary

200

150

Power

Dissipation

100

50

0

EX-OR Shift

Fibonacci Series Galois Method

Propagation

Delay

Graph 3. Graphical Representations of Different Architectures for 256 Bit

IX. CONCLUSION

In this paper, After simulation and synthesis of four architectures for device utilization summary,

propagation delay and power dissipation, as per synthesis result, it is found that Galois LFSR is power

efficient and time efficient when applied for a particular application i.e. Scrambler and Descrambler for

different bit i.e. 8 bit, 16 bit and 256 bit. Thus Galois LFSR is efficient for Random number generation as

per above results.

X. REFERENCES

[1]

Ravi saini, Sanjay Singh, Anil Saini, AS Mandal, Chandra Shekhar CSIR- central electronics

engineering research institutes (CSIRCEERI) Pilani-Rajasthan, India 2013 on Design of a

Fast and Efficient Hardware Implementation of a Random Number Generator in FPGA

[2]

Carols Gayoso, C.gonzalez in 2013 on Pseudorandom Number Generator Based on the Residue

Number System and Its FPGA Implementation in international conference on advance electronic

system (ICAES).

[3]

Yuan li, Paul Chow, Senior member IEEE, Jiang, Minxuan zhang, and shaojun wei in 2013 on

Software / Hardware Parallel Long Period Random Number Generation Framework Based On

The Well Method in IEEE Transactions

[4]

David b. Thomas, member of IEEE and Wayne luk, fellow in April 2013 on A LUT-SR Family of

Uniform Random Number Generators for FPGA Architecture IEEE transactions on very large

scale integration system, Vol 21 no 4

[5]

Jonathan M. Comer, Juan C. Cerda, Chris D. Martinez, and David H. K. Hoe in 2012 on Random

Number Generators Using Cellular Automata Implemented on FPGA.

[6]

Ray C. C. Cheung, Student Member, IEEE, Dong-U Lee, Member, IEEE, Wayne Luk, Senior Member,

IEEE ,in 2007 on Hardware Generation of Arbitrary Random Number Distributions from Uniform

Distributions Via the Inversion Method

69 | 2015, IJAFRC All Rights Reserved

www.ijafrc.org

International Journal of Advance Foundation and Research in Computer (IJAFRC)

Volume 2, Issue 8, August - 2015. ISSN 2348 4853, Impact Factor 1.317

[7]

Jiang hanging, shaojun wei international conference on computer and information technology in

2012 on An efficient hardware random number generator based on MT method

[8]

N.szaboo and R Tanaka in 1967 on Residue arithmetic and its application to computer technology

[9]

M.soderstand, w Jenkins, jullien and F.Taylor in 1986 , residue number system arithmetic modern

application in digital signal processing.

[10]

Savir,, a new empirical test for quality of random integer generators

[11]

Residue arithmetic a tutorial with examples. Computer magazines IEEE vol 1

[12]

C.M. Gonzalez, H.A.larrondo Xi workshop

dispostivos logicos programmable

[13]

Intensive statically complexity measures of pseudorandom bit by C.M. Gonzalez, H.A.larrondo

[14]

A. Ross, H.larrondo, M mertin Generalized stastical complexity measures a new tool for dynamic

systems [14]Altera corporation www.altera.com FLEX 10K embedded programmable logic device

family data sheet 2001

[15]

F. Panneton, M.Mastumoto Improved long period generators based on the linear recurrences

modulo 2 overview and comparison

[16]

Yuan li, Paul Chow, Senior member IEEE, Jiang, Minxuan zhang, and shaojun wei in 2013 on

Hardware Parallel Long Period Random Number Generation Framework Based On The Well

Method IEEE Transactions On Very High Speed Large Scale Integration

70 | 2015, IJAFRC All Rights Reserved

Implementations of de sistemas caotiocs en

www.ijafrc.org

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- 3412 Generator Set Engines Electronically Contr-1 PDFDocument50 pages3412 Generator Set Engines Electronically Contr-1 PDFFrezgi Birhanu100% (1)

- Air PurgingDocument14 pagesAir PurgingjgdberizoNo ratings yet

- Application Structure and Files-R14Document23 pagesApplication Structure and Files-R14Developer T24No ratings yet

- TPSP 1P Professional Course Master Document v8.2Document576 pagesTPSP 1P Professional Course Master Document v8.2Claudia RosaslandaNo ratings yet

- Checklist of Mandatory Documentation Required by ISO 13485 2016 enDocument17 pagesChecklist of Mandatory Documentation Required by ISO 13485 2016 enGonzalo Maza100% (2)

- Effects of Social Media On The Psychology of PeopleDocument6 pagesEffects of Social Media On The Psychology of PeopleIJAFRCNo ratings yet

- Data Security and Anonymization For Collaborative Data PublishingDocument7 pagesData Security and Anonymization For Collaborative Data PublishingIJAFRCNo ratings yet

- Performance Analysis and Lifetime Maximization of Wireless Sensor Network Using Efficient Clustering AlgorithmDocument5 pagesPerformance Analysis and Lifetime Maximization of Wireless Sensor Network Using Efficient Clustering AlgorithmIJAFRCNo ratings yet

- CFS Based Feature Subset Selection For Software Maintainance PredictionDocument11 pagesCFS Based Feature Subset Selection For Software Maintainance PredictionIJAFRCNo ratings yet

- Detecting User Relevant ApplicationsDocument7 pagesDetecting User Relevant ApplicationsIJAFRCNo ratings yet

- Efficient Algorithm Comparison To Solve Sudoku PuzzleDocument5 pagesEfficient Algorithm Comparison To Solve Sudoku PuzzleIJAFRCNo ratings yet

- Monitoring Applications in Wireless Sensor NetworksDocument4 pagesMonitoring Applications in Wireless Sensor NetworksIJAFRCNo ratings yet

- Face Granulation Using Difference of Gaussian (DOG) Method For Face RecognitionDocument7 pagesFace Granulation Using Difference of Gaussian (DOG) Method For Face RecognitionIJAFRCNo ratings yet

- Detection and Defense of DDoS AttacksDocument11 pagesDetection and Defense of DDoS AttacksIJAFRCNo ratings yet

- To Design and Algorithm Using Zero Watermarking With Stegnography For Text DocumentDocument10 pagesTo Design and Algorithm Using Zero Watermarking With Stegnography For Text DocumentIJAFRCNo ratings yet

- A Review of BFOA Application To WSNDocument7 pagesA Review of BFOA Application To WSNIJAFRCNo ratings yet

- DDos System: A Disparagement System With Cache Based and Question Generation in Client-Server ApplicationDocument13 pagesDDos System: A Disparagement System With Cache Based and Question Generation in Client-Server ApplicationIJAFRCNo ratings yet

- Pocket Barcode Application-Data Transmission Between PDA & PC Using Wireless NetworkDocument5 pagesPocket Barcode Application-Data Transmission Between PDA & PC Using Wireless NetworkIJAFRCNo ratings yet

- A Survey On Designing of Turbo Encoder & Turbo DecoderDocument8 pagesA Survey On Designing of Turbo Encoder & Turbo DecoderIJAFRCNo ratings yet

- A Short Study On Effective Predictors of Academic Performance Based On Course EvaluationDocument6 pagesA Short Study On Effective Predictors of Academic Performance Based On Course EvaluationIJAFRCNo ratings yet

- The Various Ways of Programming and Embedding Firmware Into An ARM Cortex-M3 Microcontroller Based HardwareDocument6 pagesThe Various Ways of Programming and Embedding Firmware Into An ARM Cortex-M3 Microcontroller Based HardwareIJAFRCNo ratings yet

- Perceptions On Data Aggregation in Wireless Sensor NetworkDocument5 pagesPerceptions On Data Aggregation in Wireless Sensor NetworkIJAFRCNo ratings yet

- Automated Leukemia Detection by Using Contour Signature MethodDocument8 pagesAutomated Leukemia Detection by Using Contour Signature MethodIJAFRCNo ratings yet

- Analytical Evolution of WIMAX Coded OFDM in Various Fading EnvironmentDocument8 pagesAnalytical Evolution of WIMAX Coded OFDM in Various Fading EnvironmentIJAFRCNo ratings yet

- Face Verification With Age Progression Using Discriminative Method and Gradient Orientation PyramidDocument10 pagesFace Verification With Age Progression Using Discriminative Method and Gradient Orientation PyramidIJAFRCNo ratings yet

- Application of Malicious URL Detection in Data MiningDocument6 pagesApplication of Malicious URL Detection in Data MiningIJAFRCNo ratings yet

- A Review of Compact Asymmetric Coplanar Strip Fed Monopole Antenna For Multiband ApplicationsDocument5 pagesA Review of Compact Asymmetric Coplanar Strip Fed Monopole Antenna For Multiband ApplicationsIJAFRCNo ratings yet

- A Study On Denial-Of-Service Attacks and Their Countermeasure ApproachesDocument11 pagesA Study On Denial-Of-Service Attacks and Their Countermeasure ApproachesIJAFRCNo ratings yet

- Metamaterial Based Fractal Body Worn Antenna - A ReviewDocument6 pagesMetamaterial Based Fractal Body Worn Antenna - A ReviewIJAFRCNo ratings yet

- Energy Efficient Reconfigurable Fixed Width Baugh-Wooley MultiplierDocument9 pagesEnergy Efficient Reconfigurable Fixed Width Baugh-Wooley MultiplierIJAFRCNo ratings yet

- A Comparative Study On Classification and Clustering Techniques Using Assorted Data Mining ToolsDocument8 pagesA Comparative Study On Classification and Clustering Techniques Using Assorted Data Mining ToolsIJAFRCNo ratings yet

- Predictive Model For Blood-Brain BarrierDocument12 pagesPredictive Model For Blood-Brain BarrierIJAFRCNo ratings yet

- A Comparative Study of K-Means, K-Medoid and Enhanced K-Medoid AlgorithmsDocument4 pagesA Comparative Study of K-Means, K-Medoid and Enhanced K-Medoid AlgorithmsIJAFRCNo ratings yet

- A Simple and Effective Method For Filling Gaps in Landsat ETM+ SLC-off ImagesDocument12 pagesA Simple and Effective Method For Filling Gaps in Landsat ETM+ SLC-off ImagesJanos HidiNo ratings yet

- Prototyping Benefits of Paper PrototypesDocument34 pagesPrototyping Benefits of Paper PrototypesDiman IonutNo ratings yet

- NOS AdminGuide v411 PDFDocument748 pagesNOS AdminGuide v411 PDFMaeckol Segura PeñaNo ratings yet

- Financial Econometrics AssignmentDocument14 pagesFinancial Econometrics AssignmentYuhan KENo ratings yet

- Sony Hvr-V1j U N e P C Ver1.3Document504 pagesSony Hvr-V1j U N e P C Ver1.3DanNo ratings yet

- Tetra Voice Gateway: High Capacity, Flexible Integration of TETRA Voice With Control RoomsDocument2 pagesTetra Voice Gateway: High Capacity, Flexible Integration of TETRA Voice With Control RoomsSe ZeNo ratings yet

- Aoc LC42H063D, LC42H063DDocument133 pagesAoc LC42H063D, LC42H063DsachinNo ratings yet

- Narrow Band Powerline Communication Module With Simple MAC User Narrow Band Powerline Communication Module With Simple MAC User Manual Narrow Band Powerline CommunicationDocument8 pagesNarrow Band Powerline Communication Module With Simple MAC User Narrow Band Powerline Communication Module With Simple MAC User Manual Narrow Band Powerline CommunicationAle NqnNo ratings yet

- Columbia 1987-02-25 0001Document11 pagesColumbia 1987-02-25 0001Becket AdamsNo ratings yet

- Hiperfet Power Mosfets: V I R Ixfh 26N60/Ixft 26N60 600 V 26 A 0.25 Ixfk 28N60 600 V 28 A 0.25 T 250 NsDocument2 pagesHiperfet Power Mosfets: V I R Ixfh 26N60/Ixft 26N60 600 V 26 A 0.25 Ixfk 28N60 600 V 28 A 0.25 T 250 NsAmirNo ratings yet

- VP Human Resources Director Operations in New York NY Resume Melanese MoodyDocument2 pagesVP Human Resources Director Operations in New York NY Resume Melanese MoodyMelaneseMoodyNo ratings yet

- I-Unit C#Document20 pagesI-Unit C#Swapnil RathodNo ratings yet

- GSM ParametersDocument131 pagesGSM ParametersAjay ShuklaNo ratings yet

- SentryGuide75 10sept2015Document204 pagesSentryGuide75 10sept2015Adrian Calin RigoNo ratings yet

- Munyisia Et Al 2011bDocument12 pagesMunyisia Et Al 2011bpita romawatiNo ratings yet

- Gmail - Biometric Appointment Letter - Do Not ReplyDocument2 pagesGmail - Biometric Appointment Letter - Do Not ReplyDaddly WorldNo ratings yet

- Important Reminders: Step 1Document4 pagesImportant Reminders: Step 1rmrd86w5h5No ratings yet

- 1025936797Document184 pages1025936797Wilson AgudeloNo ratings yet

- Chapter 3Document5 pagesChapter 3Naveen KumarNo ratings yet

- RFP For Procurement of 2700 PBKsDocument194 pagesRFP For Procurement of 2700 PBKsAbhik ChattopadhyayNo ratings yet

- 3D Printing and Maker Lab For Kids Create Amazing Projects With CAD Design and STEAM Ideas (Lab For Kids, 22) (Sequeira, Eldrid)Document232 pages3D Printing and Maker Lab For Kids Create Amazing Projects With CAD Design and STEAM Ideas (Lab For Kids, 22) (Sequeira, Eldrid)fejeve7854No ratings yet

- Install Ansible On Mac OSXDocument5 pagesInstall Ansible On Mac OSXNagendraNo ratings yet

- Higher-Order Ghost StateDocument14 pagesHigher-Order Ghost StateamandaNo ratings yet

- Irrigation Canal Longitudinal & Cross Section Drawing and Quantity Offtake PackageDocument16 pagesIrrigation Canal Longitudinal & Cross Section Drawing and Quantity Offtake Packageram singhNo ratings yet

- Enabling Web ConsoleDocument2 pagesEnabling Web ConsolepmmanickNo ratings yet