Professional Documents

Culture Documents

LABORATORIO 03 CEI Sumador y Restador

Uploaded by

Agustina Gutierrez PariOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LABORATORIO 03 CEI Sumador y Restador

Uploaded by

Agustina Gutierrez PariCopyright:

Available Formats

CIRCUITOS ELECTRONICOS

INTEGRADOS

III CICLO

Laboratorio N 3

SUMADOR Y RESTADOR

INTEGRANTES:

Gutierrez Pari, Agustina

Vazques Velasco, Lizett Irene

PROFESOR:

Edgar Oporto Daz

SECCIN

C5 3 C

FECHA DE REALIZACION: 23 de agosto.

FECHA DE ENTREGA: 30 de agosto.

2016-2

LAB. N 3 Sumador y Restador

Fundamento Terico

Amplificador Sumador Inversor

El circuito sumador inversor permite sumar varias seales de

forma ponderada. Todas las seales de entrada aparecen

invertidas en la salida.

Se supone que el operacional no est saturado (ideal) por lo que la tensin en la entrada

inversora del operacional es cero. Por lo tanto, la corriente If que

circula por RF hacia la derecha

es:

Y la tensin de salida Vo es:

RF permite ajustar la ganancia global, y R1, R2 y R3 permiten ajustar la ganancia individual

de cada entrada.

Restador

Restador.

El circuito de la figura resta las seales de entrada y

el resultado se amplifica con la ganancia

Av = R2/R1

Es decir:

Vout = R2/R1 (V2-V1)

PROGRAMA DE FORMACIN REGULAR

LAB. N 3 Sumador y Restador

Procedimiento

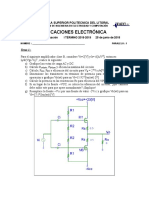

AMPLIFICADOR SUMADOR INVERSOR

1.

Implemente los siguientes divisores de voltaje mostrados en la Figura 1.

Mida en DC:

Vin1 =0.59

Vin2 =1.12

Vin3 =2

Figura 1 Divisores de voltaje a ser empleados en el circuito amplificador sumador

inversor

2.

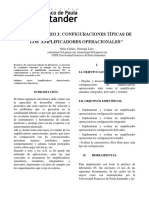

Implemente el circuito amplificador sumador inversor mostrado en la Figura 1.

Figura 2 OPAMP conectado como amplificador sumador inversor

3.

Escribir, para la configuracin de la Figura 2, las ecuaciones que definen las

caractersticas siguientes:

Avf: ganancia de tensin en lazo cerrado

PROGRAMA DE FORMACIN REGULAR

LAB. N 3 Sumador y Restador

Zvf: impedancia de entrada

Rf

r

Zn = Rn

Z0f: impedancia de salida.

4.

Para los casos indicados en la Tabla 1, mida la tensin real de salida, Vo.

Determine tambin el valor terico respectivo.

Tabla 1

Tensiones de entrada

Rf = 150K, R= 10K

7.

Tensiones de

salida

Vo

Vo real

terico

R1

R2

R3

V1

V2

V3

150K

150K

150K

0.53

1.08

1.98

-3.53

-3.59

22K

47K

51K

0.5

1.09

1.9

-11.36

-12.88

47K

33K

22K

0.5

1.08

1.9

10.70

-20.10

Medir el potencial en el punto a y compararlo con el valor terico.

El valor de a es igual a 0.

8.

Obtener la ganancia del circuito real y terico.

9.

Qu sucede cuando retira Rf.

el voltaje llega hasta 11.57089 v porque el opamp no puede amplificar mas de 12v.

10. Aplique una seal senoidal de 1V pico simultneamente a las tres entradas y

complete la tabla 2.

Tabla 2

Rf = 150K, R= 10K

Tensiones de entrada

R1

R2

R3

V1

V2

V3

51K

51K

51K

1VAC

1VAC

1VAC

PROGRAMA DE FORMACIN REGULAR

Tensiones de

salida

Vo

Vo real

terico

-8.82

4

LAB. N 3 Sumador y Restador

12. Medir el potencial en el punto a y compararlo con el valor terico.

El valor en el punto a es 0 o son nmeros pequeas menores a 1

13. Obtener la ganancia del circuito real y terico.

14. Qu sucede cuando retira Rf.

AMPLIFICADOR SUMADOR NO INVERSOR

1.

Implemente los siguientes divisores de voltaje mostrados en la Figura 3.

PROGRAMA DE FORMACIN REGULAR

LAB. N 3 Sumador y Restador

Mida en DC:

Vin1 =0.5

Vin2 =1

Vin3 =2

Figura 3 Divisores de voltaje a ser empleados en el circuito amplificador sumador

no inversor

Figura 4 OPAMP conectado como amplificador sumador no inversor

Avf: ganancia de tensin en lazo cerrado

(R=R1=R2=R3)

Zvf: impedancia de entrada

Z0f: impedancia de salida.

4.

Para los casos indicados en la Tabla 3, mida la tensin de salida real, Vo.

Determine tambin el valor terico respectivo.

Tabla 3

Rf = 150K, R= R1=R2=R3

Tensiones de entrada

PROGRAMA DE FORMACIN REGULAR

Tensiones de

salida

6

LAB. N 3 Sumador y Restador

7.

8.

9.

R1

R2

R3

V1

V2

V3

Vo real

Vo

terico

150K

150K

150K

0.5

2.46

2.33

47K

47K

47K

0.5

5.1

4.91

33K

33K

33K

0.5

6.8

6.50

Medir el potencial en el punto a y compararlo con el valor terico.

Obtener la ganancia del circuito real y terico.

Qu sucede cuando retira Rf.

Tabla 4

Rf = 150K, R= 51K

11.

12.

13.

14.

Tensiones de entrada

(voltaje pico)

R1

R2

R3

V1

V2

V3

51K

51K

51K

1VAC

1VAC

1VAC

Tensiones de

salida

(voltaje pico)

Vo

Vo real

terico

4.16

4.57

Comparar el resultado real de Vo con el terico.

Medir el potencial en el punto a y compararlo con el valor terico.

Obtener la ganancia del circuito real y terico.

Qu sucede cuando retira Rf.

PROGRAMA DE FORMACIN REGULAR

LAB. N 3 Sumador y Restador

VOLT/DIV= 500us

tiempo/div: 200us

Amplificador restador

Implemente el circuito amplificador restador mostrado en la Figura 5.

PROGRAMA DE FORMACIN REGULAR

LAB. N 3 Sumador y Restador

Figura 5 - OPAMP conectado amplificador restador

3.

Medir con el voltmetro las tensiones indicadas en la Tabla 5. Tambin pruebe

con entrada AC.

Resistores

Tensiones de entrada

R1

150K

R2

150K

V1

0.6

V2

1.14

Tensiones de salida

Vo real

Vo terico

0.52

0.54

22K

47K

0.6

1.14

1.08

1.15

47K

33K

0.6

1.14

0.36

0.37

51K

Tabla 5

22K

1VAC

2VAC

0.43

5.

Medir el potencial en el punto a y compararlo con el valor terico.

El punto sera 1.68 hallado con la formula vx=v2(R2/R2+R1)

6.

Obtener su ganancia del circuito real y terico.

Av = R2/R1

Ganancia real:1.59

Ganancia terica:1.50

Volt/div:

500us

tiempo/dic: 200us

Conclusiones:

PROGRAMA DE FORMACIN REGULAR

LAB. N 3 Sumador y Restador

se comprob los valores tericos y prcticos de los circuitos sumadores y

restadores del OPAMP.

Se identific los parmetros del OPAMP.

APLICACIN DE LO APRENDIDO 5 PUNTOS

Se pide disear, simular e implementar un circuito sumador con las siguientes especificaciones:

Encontrar adems los valores de R1, R2, R3 y Rc.

Considerar dos casos:

a) V1= V2= V3= 1V DC y Rf= 10K

b) V1= V2= V3= 1V AC pico y Rf= 10K

Explicar todo lo que se escoge y por qu.

DESARROLLO

De la ecuacin de salida se observa que es de la forma de un circuito Sumador Inversor, que

sabemos que es de la forma:

Comparando esto con lo pedido, y reemplazando los valores indicados.

PROGRAMA DE FORMACIN REGULAR

10

LAB. N 3 Sumador y Restador

v

v

v

Vo 1 2 3 10k v1 2v2 4v3

R1 R2 R3

R1 10k

R2 5k

R3 2.5k

Simulando el circuito mediante el programa multisim.

Se obtiene:

El valor de salida para los valores pedidos (V1=V2=V3=1), se observa que es -6.991, lo que

es muy cercano al -7 terico. Se puede ver adems que, modificando los valores de tensin de

entrada, se sigue cumpliendo la funcin de salida del opamp.

Eligiendo los valores v1=2, v2=2, v3=1:

PROGRAMA DE FORMACIN REGULAR

11

LAB. N 3 Sumador y Restador

Se esperara: - (2V+2*2V+4*1V) = -10V, y se obtiene el resultado-9.991V

Se observa que tambin cumple el resultado de la funcin de suma inversa pedida.

PROGRAMA DE FORMACIN REGULAR

12

You might also like

- Trans Tema3Document62 pagesTrans Tema3opachecoNo ratings yet

- Previo Practica 3 Circuitos ElectricosDocument3 pagesPrevio Practica 3 Circuitos ElectricosHugo98No ratings yet

- Informe Final 2Document17 pagesInforme Final 2EstivenAlarconPillcoNo ratings yet

- Universidad Nacional de Ingenieria Facultad de Electrotecnia y Computación Circuitos Eléctricos IIDocument11 pagesUniversidad Nacional de Ingenieria Facultad de Electrotecnia y Computación Circuitos Eléctricos IIGerald AburtoNo ratings yet

- Diseño e Implementación de Un Electrocardiograma Utilizando Un DspicDocument24 pagesDiseño e Implementación de Un Electrocardiograma Utilizando Un DspicFernando_Paez_100% (1)

- Amplificadores RealimentadosDocument16 pagesAmplificadores RealimentadosRolando Choque CahuanaNo ratings yet

- Practica Grupal Calficada de Mat - Avanz. Unac FieeDocument6 pagesPractica Grupal Calficada de Mat - Avanz. Unac FieeJorge More100% (1)

- Practica No. 2 de Sistemas de Datos Muestreados 1 PDFDocument14 pagesPractica No. 2 de Sistemas de Datos Muestreados 1 PDFPaola YllañisNo ratings yet

- El Amplificador Darlington Con BJTDocument2 pagesEl Amplificador Darlington Con BJTLeirsson PeñalvaNo ratings yet

- Lab Previo 1Document9 pagesLab Previo 1RENZO JETT VARGAS DELGADONo ratings yet

- El AMPLIFICADOR MULTIETAPA DIRECTAMENTE ACOPLADO PDFDocument11 pagesEl AMPLIFICADOR MULTIETAPA DIRECTAMENTE ACOPLADO PDFRoberto Carlos Sahuanay ArreNo ratings yet

- TBJDocument5 pagesTBJErik RojasNo ratings yet

- Marco Gabriel Maldonado GutiDocument5 pagesMarco Gabriel Maldonado GutiMARCO GABRIEL MALDONADO GUTIERREZNo ratings yet

- Resonancia en circuitos RLCDocument9 pagesResonancia en circuitos RLCAndrea Chavez CossioNo ratings yet

- INFORME N°9-Circuitos Electronicos IIDocument14 pagesINFORME N°9-Circuitos Electronicos IICarlosNo ratings yet

- Jiménez 2017079514Document3 pagesJiménez 2017079514Javier Jimnez FonsecaNo ratings yet

- Informe N°3 - ANÁLISIS DE CA DE UN BJTDocument8 pagesInforme N°3 - ANÁLISIS DE CA DE UN BJTOmar Ruiz Rodríguez100% (1)

- Informe Final 3 Sc-1Document14 pagesInforme Final 3 Sc-1gersonNo ratings yet

- Ejercicios Impares Del Archivo Tema1Document4 pagesEjercicios Impares Del Archivo Tema1David BravoNo ratings yet

- Tarea Campos2Document9 pagesTarea Campos2Miguel RodriguezNo ratings yet

- Cap 03 Modulacion AM2Document21 pagesCap 03 Modulacion AM2albertwillyNo ratings yet

- CuestionarioDocument10 pagesCuestionario25 Olmedo RenatoNo ratings yet

- Amplificadores BJT en CascadaDocument6 pagesAmplificadores BJT en CascadaJose SegoviaNo ratings yet

- Amplificador Diferencial - PrevioDocument10 pagesAmplificador Diferencial - PrevioOmar Minaya FerruzoNo ratings yet

- Examen Parcial-PeralesDocument23 pagesExamen Parcial-PeralesTRUJILLO ZULUETA RENATO ANGELONo ratings yet

- Problemas Propuestos 2018-2Document4 pagesProblemas Propuestos 2018-2Jhoelito KennedyNo ratings yet

- Rectificación media onda y onda completaDocument8 pagesRectificación media onda y onda completaMaick ZhNo ratings yet

- Informe MezcladorDocument10 pagesInforme Mezcladorcarolina cNo ratings yet

- Informe de La Fuente ElctronicaDocument7 pagesInforme de La Fuente ElctronicaAlexander Olvera LugoNo ratings yet

- Informe Final 1Document4 pagesInforme Final 1kevin ANNo ratings yet

- Lab 01 TCA1 - IntroMatlabDocument24 pagesLab 01 TCA1 - IntroMatlabChristian Choquehuanca PacoriNo ratings yet

- Informe Lab 5Document7 pagesInforme Lab 5LUIS ALBERTO CUPA HANCCONo ratings yet

- Circuito Derivador e Integrador AutoguardadoDocument12 pagesCircuito Derivador e Integrador AutoguardadoFlavio Adrian Sisa CastroNo ratings yet

- Practica 1 Diseño DigitalDocument8 pagesPractica 1 Diseño DigitalPandaNo ratings yet

- Informe Previo 4 Circuitos AritmeticosDocument8 pagesInforme Previo 4 Circuitos AritmeticosGhozt14891No ratings yet

- PDF Ejer Cici Os Compress PDFDocument66 pagesPDF Ejer Cici Os Compress PDFAlan Page HernandezNo ratings yet

- Práctica 6Document14 pagesPráctica 6Calvin CantuNo ratings yet

- Practica 1 Diseño Digital.Document11 pagesPractica 1 Diseño Digital.Angel OrochimaruNo ratings yet

- Introducción A Los Sistemas DiscretosDocument17 pagesIntroducción A Los Sistemas DiscretosGustavo Rico RasgadoNo ratings yet

- Deber #2 Amplificadores DiferencialesDocument30 pagesDeber #2 Amplificadores DiferencialesluisciferelectronicaNo ratings yet

- Aplicaciones Electrónica: Títulos de los 12 TemasDocument13 pagesAplicaciones Electrónica: Títulos de los 12 TemasDouglas Daniel Pincay QuimiNo ratings yet

- UNMSM Facultad de Ingeniería Eléctrica y Electrónica método bisecciónDocument3 pagesUNMSM Facultad de Ingeniería Eléctrica y Electrónica método bisecciónYAIR ROBERTO MALASQUEZ VILCHEZNo ratings yet

- Informe 1 (Implementacion de Circuito Retroalimentado)Document7 pagesInforme 1 (Implementacion de Circuito Retroalimentado)Ernesto Ezequiel Lamby DelgadoNo ratings yet

- RECTIFICADOR DE ONDA COMPLETA Y FILTRADODocument5 pagesRECTIFICADOR DE ONDA COMPLETA Y FILTRADOKatherine Cortez VillaNo ratings yet

- Alulema Diego Capitulo5 Impares 9931Document11 pagesAlulema Diego Capitulo5 Impares 9931DIEGO ALULEMA PARRANo ratings yet

- Informe 6 - Filtros PasivosDocument9 pagesInforme 6 - Filtros PasivosManuel GeronimoNo ratings yet

- Filtros de Sistemas y SeñalesDocument15 pagesFiltros de Sistemas y SeñalesMiguel AlejandroNo ratings yet

- Circuitos básicos con amplificador operacionalDocument9 pagesCircuitos básicos con amplificador operacionalAnonymous Shv3RwsWnrNo ratings yet

- Ampliación de escala de voltímetro y amperímetro en laboratorio de mediciones eléctricasDocument6 pagesAmpliación de escala de voltímetro y amperímetro en laboratorio de mediciones eléctricasMary Isabel EspinoNo ratings yet

- UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS circuitos electrónicos controlDocument3 pagesUNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS circuitos electrónicos controlCaptain UnderoosNo ratings yet

- Etn 805 Teoria de Sistemas Marisol Chipana MamaniDocument1 pageEtn 805 Teoria de Sistemas Marisol Chipana MamaniMari MamaniNo ratings yet

- Apuntes de Clases - Dispo - 2Document109 pagesApuntes de Clases - Dispo - 2Frank VenturaNo ratings yet

- Informe Lab 3 Electronica 3Document7 pagesInforme Lab 3 Electronica 3Carlos NiñoNo ratings yet

- Adc0804 Conversor Analogo DigitalDocument3 pagesAdc0804 Conversor Analogo DigitalRonald Däviid WarNo ratings yet

- Informe N°7Document7 pagesInforme N°7Joel AlvinagortaNo ratings yet

- Thevenin y NortonDocument6 pagesThevenin y NortonLeonel PalominoNo ratings yet

- OsciladoresDocument4 pagesOsciladoresHector Cajilema100% (1)

- Informe de Laboratorio N ° 3Document10 pagesInforme de Laboratorio N ° 3Josep LopezNo ratings yet

- Informe de Electronica TecsupDocument19 pagesInforme de Electronica TecsupBryan Escobedo0% (2)

- Armónicas en Sistemas Eléctricos IndustrialesFrom EverandArmónicas en Sistemas Eléctricos IndustrialesRating: 4.5 out of 5 stars4.5/5 (12)

- Ingenieria de Sistemas e InformaticaDocument8 pagesIngenieria de Sistemas e InformaticaLuis Meneses QuintoNo ratings yet

- Lab5 CostosDocument4 pagesLab5 CostosAgustina Gutierrez PariNo ratings yet

- Control de velocidad de motor DC con controlador Sipart DR-20Document14 pagesControl de velocidad de motor DC con controlador Sipart DR-20Agustina Gutierrez PariNo ratings yet

- CN 1 7 Ciencias Básicas Aplicadas 2016 01Document5 pagesCN 1 7 Ciencias Básicas Aplicadas 2016 01Agustina Gutierrez PariNo ratings yet

- Texto 3Document10 pagesTexto 3Agustina Gutierrez PariNo ratings yet

- Derivada PDFDocument10 pagesDerivada PDFRonny CárdenasNo ratings yet

- Libro Integrales Resueltas PDFDocument242 pagesLibro Integrales Resueltas PDFJordan Hernandez Vidal100% (2)

- LABORATORIO 5 Ciencias Básicas...................Document10 pagesLABORATORIO 5 Ciencias Básicas...................Agustina Gutierrez PariNo ratings yet

- Artificio Integral Ida 1Document13 pagesArtificio Integral Ida 1lili274No ratings yet

- Curso Estrategias de Control AutomáticoDocument4 pagesCurso Estrategias de Control AutomáticoAgustina Gutierrez PariNo ratings yet

- 3 Variadores de Velocidad Pot Control 3Document37 pages3 Variadores de Velocidad Pot Control 3Agustina Gutierrez PariNo ratings yet

- CN 1 4 Ciencias Básicas Aplicadas 2016 01Document5 pagesCN 1 4 Ciencias Básicas Aplicadas 2016 01Agustina Gutierrez PariNo ratings yet

- Energía Renovables 3Document15 pagesEnergía Renovables 3Agustina Gutierrez PariNo ratings yet

- Fluidos - Calor U2.2 Bombas CompreDocument27 pagesFluidos - Calor U2.2 Bombas CompreAgustina Gutierrez PariNo ratings yet

- Texto 5Document11 pagesTexto 5Agustina Gutierrez PariNo ratings yet

- Estadistica para IngenieriaDocument85 pagesEstadistica para IngenieriaAgustina Gutierrez Pari0% (1)

- Puertas LogicasDocument21 pagesPuertas LogicasAgustina Gutierrez PariNo ratings yet

- Probabilidad PDFDocument14 pagesProbabilidad PDFAgustina Gutierrez PariNo ratings yet

- Energía Renovables 3Document15 pagesEnergía Renovables 3Agustina Gutierrez PariNo ratings yet

- Electronica de Potencia Teoria y Aplicaciones - Jose Manuel Benavent PDFDocument0 pagesElectronica de Potencia Teoria y Aplicaciones - Jose Manuel Benavent PDFmakv12100% (2)

- 2 Dispositivos Integrados - Unidad FPGA VHDLDocument111 pages2 Dispositivos Integrados - Unidad FPGA VHDLAgustina Gutierrez PariNo ratings yet

- 1 Labep2017-IiDocument6 pages1 Labep2017-IiAgustina Gutierrez PariNo ratings yet

- Clase 10Document20 pagesClase 10Agustina Gutierrez PariNo ratings yet

- Transform Ad orDocument38 pagesTransform Ad orAgustina Gutierrez PariNo ratings yet

- Optimización 2016 - 2Document4 pagesOptimización 2016 - 2Agustina Gutierrez PariNo ratings yet

- Laboratorio 15 - Cei - Diseño JerárquicoDocument21 pagesLaboratorio 15 - Cei - Diseño JerárquicoAgustina Gutierrez PariNo ratings yet

- Estadistica para Ingenieria PDFDocument85 pagesEstadistica para Ingenieria PDFAgustina Gutierrez PariNo ratings yet

- Poderosa Ip EfluentesDocument64 pagesPoderosa Ip EfluentesAgustina Gutierrez PariNo ratings yet

- SeguridadDocument33 pagesSeguridadAgustina Gutierrez PariNo ratings yet

- 7 TrigonometriaDocument24 pages7 TrigonometriaAntonio Fernández ReyesNo ratings yet

- Controladores lógicos programables Siemens PLCDocument16 pagesControladores lógicos programables Siemens PLCGerardo Apolinar ArellanoNo ratings yet

- Curso de capacitación para reparación de TV Aquos LC52LE810Document93 pagesCurso de capacitación para reparación de TV Aquos LC52LE810Francisco Orozco100% (1)

- Manual Trafo Monofasico SecoDocument8 pagesManual Trafo Monofasico SecoJeniferNo ratings yet

- Memorias flash: ventajas, usos y tipos de unidades de almacenamiento electrónicoDocument7 pagesMemorias flash: ventajas, usos y tipos de unidades de almacenamiento electrónicoJJSilvaNo ratings yet

- Láminas FusiblesDocument11 pagesLáminas FusiblesJeans GonzalezNo ratings yet

- Proteccion SobretensionesDocument8 pagesProteccion SobretensionesJose-Maria Gordillo GomezNo ratings yet

- Curso Electricidad Básica: Amperaje, Voltaje, Frecuencia y FaseDocument2 pagesCurso Electricidad Básica: Amperaje, Voltaje, Frecuencia y FaseGERARDO ANTONIO HUIPE MARTINEZNo ratings yet

- Relacion de Transformacion y Polaridad en Transformadores MonofasicosDocument15 pagesRelacion de Transformacion y Polaridad en Transformadores MonofasicosLuis PerezNo ratings yet

- Circuitos Monofásicos y TrifásicosDocument10 pagesCircuitos Monofásicos y TrifásicosnandoNo ratings yet

- Manual Contruccion FTTHDocument38 pagesManual Contruccion FTTHElectronica EdwinNo ratings yet

- Caja de Filtro de Aire Completa para Yamaha JOG50 JOG 50cc XH 90 Scooter de 2 TiemposDocument80 pagesCaja de Filtro de Aire Completa para Yamaha JOG50 JOG 50cc XH 90 Scooter de 2 Tiemposjuan pablo galeano arangoNo ratings yet

- DSP - Diseño de Filtros Digitales Con Fdatool PDFDocument27 pagesDSP - Diseño de Filtros Digitales Con Fdatool PDFArmando CajahuaringaNo ratings yet

- Warrior 350iDocument34 pagesWarrior 350iWilleman GuadalupeNo ratings yet

- Esquemas Electricos Ok PDFDocument4 pagesEsquemas Electricos Ok PDFYefri JonasNo ratings yet

- En Qué Año Se Inventó La Fibra ÓpticaDocument2 pagesEn Qué Año Se Inventó La Fibra ÓpticaAlexis RiosNo ratings yet

- Generadores de Uso de GeneraciónDocument10 pagesGeneradores de Uso de GeneraciónEDSON JOAO MARTINEZ CARVAJALNo ratings yet

- Lab 1 CLDocument6 pagesLab 1 CLestabn quitoNo ratings yet

- Unidad Vi Circuitos Electricos IIDocument5 pagesUnidad Vi Circuitos Electricos IIJherson ChoqueNo ratings yet

- Feedback linealización técnicaDocument15 pagesFeedback linealización técnicaedwardNo ratings yet

- MTO250 DS Es V02Document3 pagesMTO250 DS Es V02ingenierobasilioNo ratings yet

- Diagrama A Bloques - 18140801Document6 pagesDiagrama A Bloques - 18140801Daniel RamirezNo ratings yet

- Proyecto IotDocument11 pagesProyecto IotDaniel Felipe Sanchez VillalbaNo ratings yet

- Industria MecanicaDocument34 pagesIndustria MecanicaSamy Orlando Meza CuentasNo ratings yet

- Arquitectura de HardwareDocument105 pagesArquitectura de HardwareFlora Silvestre ColqueNo ratings yet

- Paper Lora 3brDocument4 pagesPaper Lora 3brMishell CarolinaNo ratings yet

- Ma Di 08 002 018 Pruebas Reconectadores V 1Document22 pagesMa Di 08 002 018 Pruebas Reconectadores V 1hencyroballoNo ratings yet

- Guia Docente Instelec 2020-21Document10 pagesGuia Docente Instelec 2020-21Indalecio MerinoNo ratings yet

- Proyecto Tercer Trayecto RediseñoDocument100 pagesProyecto Tercer Trayecto RediseñoANTHONY ORTIZNo ratings yet

- Curriculum Vitae Javier Coronado BautistaDocument10 pagesCurriculum Vitae Javier Coronado BautistaJavier Coronado BautistaNo ratings yet

- CLASIFICACIÓN DE LOS MÉTODOS DE CONEXIÓN - VelazquezSanchezSylviaJeanetteDocument17 pagesCLASIFICACIÓN DE LOS MÉTODOS DE CONEXIÓN - VelazquezSanchezSylviaJeanetteSylvia J. VelSanNo ratings yet