Professional Documents

Culture Documents

7 2014 Itrs 2.0 Beyond Cmos r1

Uploaded by

VENKICopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

7 2014 Itrs 2.0 Beyond Cmos r1

Uploaded by

VENKICopyright:

Available Formats

BeyondCMOSWhitePaper

Beyond-CMOS White Paper

1. Emerging Research Devices (ERD) in ITRS 2.0

Emerging Research Devices (ERD) will be the core of the beyond CMOS focus team (FT) in

ITRS 2.0. The beyond CMOS FT will cover emerging memory, logic, and architectures that ERD

has traditionally focused on. In addition, new areas of emerging technologies relevant to new

application drivers will be explored. ERD is an established and respected brand name from ITRS;

therefore, it is important for ERD to continue its activities as a technology working group. Beyond

CMOS will be a focused task that ERD is undertaking in ITRS 2.0. ERD provides a unique function

as an interface between industry and academic research. It also serves as a guideline for funding

agencies. The focus on beyond CMOS in the future direction will enhance this function and keep

ERD aligned with new application drivers.

System

integration

Outside

system

connectivity

Application drivers;

Performance

requirements

ERD: Beyond CMOS

Integration and

manufacturability

requirements

Heterogeneous

integration

Heterogeneous

components

Assessment &

transition criteria

More Moore

Manufacturing

Figure 1 The role of ERD and interaction with other focus teams in ITRS 2.0

ERD and the beyond CMOS FT will closely interact with the other six FTs in ITRS 2.0, as

illustrated in Fig. 1. The beyond CMOS FT receives inputs regarding application drivers and

performance requirements from the system integration and outside system connectivity FTs. It

also interacts with the heterogeneous components and more Moore FTs to both receive

assessment/transition criteria and provide inputs of emerging components that may be adopted by

these FTs in the future. This is similar to the relationship that ERD has had with FEP and PIDS.

Interaction with the manufacturing and heterogeneous integration FTs will help the beyond

CMOS FT to consider manufacturing and integration feasibility of emerging technologies.

This white paper will outline the proposed scope of beyond CMOS by the ERD group.

2. Difficult Challenges

ERD has traditionally focused on novel memory and information processing devices based on

alternative materials and mechanisms to extend ultimately scaled CMOS. With application drivers

BeyondCMOSWhitePaper

broaden from computing/communication to IoT (Internet of Things), cloud computing, and big data,

there are new functionalities and performance requirements for emerging devices.

Table 1. Summary of difficult challenges in beyond CMOS technology options

Difficult challenges

High-performance and high-density memory

solutions for embedded and standalone

applications; devices and architectures for

storage-class memories.

Extend CMOS scaling with alternative channel

materials and device structures

Beyond-CMOS devices with substantially

improved performance and/or functionality

Emerging architectures to improve information

processing and utilize novel characteristics of

emerging device

Invent and reduce to practice long term

alternative solutions to technologies that

address functionality requirements in new

application drivers including mobile, IoT, cloud

computing, etc.

Opportunities and issues

A range of new memory concepts (mostly based on resistance change

in two-terminal structures) with promising characteristics to meet

requirement from working memory to storage applications

Most emerging memories are BEOL devices: integration and

processing issues

High-density memory arrays require functional selector devices in

addition to memory elements

Reliability issues of these emerging memories have to be identified

and addressed early in the technology development

Novel channel materials with better transport properties are actively

explored, e.g., III-V, Ge, carbon nanotube, 2D materials

Electrostatics can be better controlled in gate-all-around nanowire

devices

Integration of heterogeneous materials is challenging

Control variability of critical dimensions and statistical distributions

(e.g., gate length, channel thickness, S/D doping concentrations, etc.)

Novel mechanisms and alternative state variables have been utilized

to develop charge and non-charge based beyond-CMOS devices

While beyond-CMOS devices may achieve lower power, overall

performance has rarely exceed that of CMOS; energy-delay tradeoff

continues to exist

Unique characteristics (e.g., nonvolatility) may enable new designs

that are not possible in CMOS to improve performance on circuit and

system levels.

A variety of architecture solutions are actively explored to overcome

the limitation of von Neumann architecture and conventional CMOS

New architecture solutions may circumvent limitations of emerging

devices (e.g., speed) and utilize their advantages (e.g., low power) to

improve overall performance

New architectures may enable application-specific optimization

Lack of clear correlation between emerging architectures and devices

Architecture-level assessment and benchmark require different

approaches from device-level assessment

The industry faces an increasing importance of a new trend where

added value to devices is provided by incorporating functionalities

that do not necessarily scale according to "Moore's Law.

Heterogeneous integration of digital and non-digital functionalities

into compact systems that will be the key driver for a wide variety of

application fields, such as communication, automotive,

environmental control, healthcare, security and entertainment.

Some key attributes pursued by ERD devices continue to be critical

for new application drivers, e.g., low-power, scalability, etc.

New application drivers require new characteristics and capabilities,

e.g., sensing, security, etc.

3. Methodology

3.1 Technology entry selection, categorization, and tabulation

ERD has well-defined approaches to select, categorize, and tabulate emerging technology entries,

which will continue to be the main methodology used in beyond CMOS. Consistent and rigorous

criteria will be used to select a new technology entry and remove an existing entry. Currently, a new

BeyondCMOSWhitePaper

technology will be introduced into ERD only if at least two research groups are actively working on it

or one group has published extensively on it. Technology entries will be categorized for clarity and

tracking. For example, emerging memory devices are divided into volatile and nonvolatile, with

further categories based on maturity. Emerging logic devices are divided into three groups based on

novelty and state of variables. With the long-term research nature, emerging technologies are

difficult to be roadmapped as yearly projections. Instead, ERD tabulate technology entries with best

available demonstrated and projected parameters for assessment. One of the challenges is to balance

the best value of individual parameters and the tradeoff among parameters. A collection of the best

parameters of a technology from different publications and implementations may not provide a

realistic assessment of a technology.

3.2 Technology assessment and critical review

Key assessment parameters for emerging memory and logic devices include energy/power, speed,

scalability, endurance, and gain (for logic) or on/off ratio (for memory). ERD has traditionally

tracked device-level parameters. Recently, circuit-level parameters have become increasingly

important; however, tracking circuit-level parameters involves more complexity and variety of circuit

implementations that are difficult to manage. Nevertheless, ERD has gradually started including

some circuit-level performance metrics.

ERD has carried out critical reviews based on the survey in the ERD group to evaluate memory

and logic devices using eight criteria. It provides useful opinion-based assessment and the survey

results (plotted as spider charts) have been widely cited in research papers, reports, and presentations.

In the context of ITRS 2.0 with new application drivers, these criteria need to be re-designed to

ensure their relevance. Another challenge is to increase the statistical base of the survey to enhance

the validity of the critical review.

4. Proposed scope of Beyond CMOS

4.1 Emerging memory/logic devices and architectures

Table 2 is a summary of the entries of emerging memory/logic devices and architectures in the

2013 ERD chapter. The beyond CMOS chapter will continue to cover similar topics with updates

based on technology progress. Emerging memory/logic devices and architectures will still be the

most important sections with the new focus on beyond CMOS.

Among emerging memory devices, molecular memory has shown limited progress and may be

considered to transition out of the chapter. The macromolecular memory has raised many questions

on the real function of polymer materials in the switching mechanism. A possible arrangement is to

categorize macromolecular memory as a type of resistive memory featuring polymer materials.

MRAM (Magnetic RAM) / STTRAM (Spin Torque Transfer RAM) has transitioned from the ERD

chapter to the PIDS chapter, and the ERM chapter continues tracking perpendicular MTJ (Magnetic

Tunnel Junction) materials. However, some recent development (e.g., giant spin-Hall-effect, voltagecontrolled magnetic anisotropy) may enable novel STTRAM devices and structures. A novel

MRAM/STTRAM memory entry may be introduced in the chapter.

Among emerging logic devices, atomic switch and excitonic FET are two possible entries to be

removed from the chapter, due to limited progress. Atomic switch is essentially a logic application of

CBRAM(Conductive Bridging RAM)-type of memories. If it is removed from the logic tables, it

BeyondCMOSWhitePaper

may be discussed in the CBRAM category as its logic application and in the reconfigurable

architecture section. The n-Ge and p-IIIV FETs have been considered for transition because of its

relative more mature nature than the other beyond-CMOS devices. BisFET (Bilayer pseudo-spin

Field Effect Transistor) is going through major changes from its original concept and the ERD entry

will be revised accordingly. Several new logic devices have been proposed recently and will be

evaluated as possible new logic entries, e.g., 2D channel FET, pizeotronic transistors.

The emerging architecture section currently covers a broad range of interesting concepts;

however, it lacks consistent organization and clear link with device entries. This section will be reorganized to both reflect the most advanced progress in emerging architectures and also correlate

these architecture concepts with device options. An emerging architecture-device mapping workshop

is planned in early 2015 to explore this correlation and help revising this section.

Table 2. Emerging memory/logic devices and architectures in 2013 ERD chapter

Emerging memory devices

Emerging logic devices

Emerging architectures

Emerging ferroelectric memory

o FeFET

o FE tunnel junction

Carbon memory

Mott memory

Macromolecular memory

Molecular memory

ReRAM

o Electrochemical metallization bridge

o Metal oxide: bipolar filament

o Metal oxide: unipolar filament

o Metal oxide: bipolar non-filamentary

Carbon-based nanoelectronics

Nanowire FETs

Tunnel FET

n-Ge and p-IIIV

Spin-FET and spin-MOSFET

NEMS

Atomic switch

Mott FET

Neg-Cg ferroelectric FET

Spin wave devices

Nano-Magnet Logic

Excitonic FET

BisFET

Spin torque majority gate

All spin logic

Memory architectures for

program centric architectures

Storage Class Memories

Evolved architectures exploiting

emerging research memory

devices

Architectures that can learn

Morphic architectures

o Neuromorphic architecture

o Cellular automata architecture

o Cortical architecture

4.2 Emerging devices for RF

ERD has started a more-than-Moore (MtM) section in 2011 and the first topic was emerging

devices for analog and RF applications. Table 3 summarizes the devices categorized in the chapter.

With mobile applications identified as a key system driver, it is more important for ERD to evaluate

the potential of emerging devices for RF applications. A major weakness of the current section is the

lack of quantitative assessment of these devices, which will be addressed in 2015.

Table 3. Technology entries of emerging devices for RF application in ERD MtM section

ERD MtM devices for RF applications

BeyondCMOSWhitePaper

Graphene RF transistors

Spin torque oscillators

NEMS resonators

o Based on Si nanowires, CNT and graphene

o Based on resonant gate or vibrating body transistors

RF mixers

o Resonant tunneling diodes

o Single electron transistors

o Graphene and CNT transistors

4.3 Emerging devices for sensor applications

With the potential application drivers of mobile, IoT, and cloud computing, sensors have become

key components in ITRS 2.0 and are a major focus of the heterogeneous components FT. The

beyond CMOS FT will explore emerging devices suitable for sensor applications. This new

category for ERD requires new expertise to be added in the group. It is also important for ERD to

follow the methodology and assessment criteria developed by the heterogeneous components FT to

track emerging candidates for sensor applications.

4.4 Emerging devices with learning capabilities

The 2013 ERD chapter added devices with learning capabilities as a sub-category of MtM

section. It roughly divided learning devices into two types: learning through re-configuration and

learning by examples. Bio-inspired intelligent and efficient computing is considered an important

future direction. Therefore, this section will be further expanded into more detailed device categories

with assessment. These devices will also be discussed in the context of architectures with learning

capabilities.

4.5 Emerging devices for security

Security is a critical requirement for all the major application drivers identified for ITRS 2.0.

Current security solutions are often realized by software and algorithms. However, increasing

research effort has focused on security solutions that can be implemented in hardware. Physically

unclonable functions (PUFs), as an example, utilize intrinsic variability in IC and devices to generate

security primitives. Some emerging devices may be more robust against side-channel attack and

temper-resistant. The randomness in some emerging device characteristics can be utilized to realize

random number generators. These security features on the device level could be utilized for efficient

hardware security solutions. ERD plans to explore security applications of emerging devices in

beyond CMOS.

4.6 Flexible electronics

Flexible electronics may provide low-cost solutions (e.g., printing) and useful candidates for

wearable electronics. Some emerging devices have attractive features that are potentially useful for

flexible electronics, e.g., macromolecular devices, thin-film transistors, some resistive memories, etc.

Exploring this new category of emerging devices will require assessment criteria different from

conventional memory/logic devices.

5. Summary

BeyondCMOSWhitePaper

The ERD group will focus on beyond CMOS technology options for ITRS 2.0. The traditional

ERD focus on memory and logic devices will continue to be the major part in the chapter. Emerging

architectures have become increasingly important in beyond-CMOS research. Clear mapping

between devices and architecture concepts will provide more useful research guidelines. Significant

expansion of the ERD chapter is planned under the scope of beyond CMOS, including emerging

device for sensor applications, emerging devices for security applications, flexible electronics. The

expansion will require new expertise in the ERD group. ERD group will closely collaborate and

coordinate with other FTs and TWGs to deliver the future technology options in ITRS 2.0.

You might also like

- Final Approval Process Handbook 2017 18Document273 pagesFinal Approval Process Handbook 2017 18Jakkam Rajesh100% (2)

- iecWP Internetofthings LR en PDFDocument78 pagesiecWP Internetofthings LR en PDFAbebeNo ratings yet

- 8087Document23 pages8087Abhishek SenNo ratings yet

- VerilogDocument104 pagesVerilogPhu TranNo ratings yet

- Graduate AttributesDocument1 pageGraduate AttributesVENKINo ratings yet

- EC6304 Assignment 1 Set2Document2 pagesEC6304 Assignment 1 Set2VENKINo ratings yet

- VL7202 - Low Power VLSI Design PresentationDocument33 pagesVL7202 - Low Power VLSI Design PresentationVENKINo ratings yet

- Syllabi GATE2017 PDFDocument73 pagesSyllabi GATE2017 PDFAnkit Kumar AJNo ratings yet

- TTD Brahmotsavam InvitationDocument16 pagesTTD Brahmotsavam InvitationVENKINo ratings yet

- Sensors 14 06247Document32 pagesSensors 14 06247VENKINo ratings yet

- AUStudentHelp Anna University Chennai R2013 Time Table Nov Dec 2016 Min PDFDocument77 pagesAUStudentHelp Anna University Chennai R2013 Time Table Nov Dec 2016 Min PDFSundar Rajan ANo ratings yet

- AUStudentHelp Anna University Chennai R2013 Time Table Nov Dec 2016 Min PDFDocument77 pagesAUStudentHelp Anna University Chennai R2013 Time Table Nov Dec 2016 Min PDFSundar Rajan ANo ratings yet

- U401 8051 IntroductionDocument18 pagesU401 8051 IntroductionVENKINo ratings yet

- How It Works Book of The Human Body 7th Edition PDFDocument180 pagesHow It Works Book of The Human Body 7th Edition PDFNade Ojeranac100% (1)

- L1Document42 pagesL1VENKINo ratings yet

- Ladies Special Sup Nov 2016Document21 pagesLadies Special Sup Nov 2016VENKINo ratings yet

- 8051Document28 pages8051MadhuSquareNo ratings yet

- Ladies Special Nov 2016Document85 pagesLadies Special Nov 2016VENKINo ratings yet

- More Moore WPDocument21 pagesMore Moore WPVENKINo ratings yet

- Dunmugi Thanigai Thirukanitha PanchangamDocument20 pagesDunmugi Thanigai Thirukanitha Panchangamtechsivam0% (1)

- News Letter Vol 18 No 1 Jan-April 2016Document36 pagesNews Letter Vol 18 No 1 Jan-April 2016VENKINo ratings yet

- Tancet 2016Document1 pageTancet 2016VENKINo ratings yet

- Districtwise CollegesDocument7 pagesDistrictwise CollegesVENKINo ratings yet

- Study ESA 86/88-2 Microprocessor TrainerDocument6 pagesStudy ESA 86/88-2 Microprocessor TrainerVENKI100% (1)

- MASM Tutorial PDFDocument10 pagesMASM Tutorial PDFShashankDwivediNo ratings yet

- Software Architecture of The 8088 and 8086 MicroprocessorsDocument26 pagesSoftware Architecture of The 8088 and 8086 MicroprocessorsPauline AdamsNo ratings yet

- Ex8 DOS InterruptFunctionsDocument23 pagesEx8 DOS InterruptFunctionsVENKINo ratings yet

- Autonomous GuidelinesDocument3 pagesAutonomous GuidelinesVENKINo ratings yet

- Ec6504 Microprocessor and Microcontroller - SyllabusDocument1 pageEc6504 Microprocessor and Microcontroller - SyllabusJagadeesh MohanNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- WozairDocument4 pagesWozairRajakumar Bajji SubburamanNo ratings yet

- DCT PIR insulation technical data sheetDocument4 pagesDCT PIR insulation technical data sheetHenky MantophaniNo ratings yet

- AIA Design Development Deliverable ListDocument8 pagesAIA Design Development Deliverable Listpeterhwilliams100% (1)

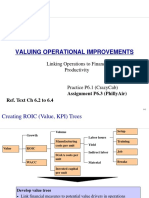

- 2 Linking Operations To Finance and ProductivityDocument14 pages2 Linking Operations To Finance and ProductivityAidan HonnoldNo ratings yet

- RepairManual NEF M100 M150 P3D32N003E Mar06Document172 pagesRepairManual NEF M100 M150 P3D32N003E Mar06manuel segovia100% (1)

- Climate Change & Disaster Risk Management: Razon, Lovelyn Rivera, Meg Anne Sta. Ines, MaricrisDocument56 pagesClimate Change & Disaster Risk Management: Razon, Lovelyn Rivera, Meg Anne Sta. Ines, MaricrisMeg Anne Legaspi RiveraNo ratings yet

- 28 2001 04 0007Document1 page28 2001 04 0007Fernando FanteNo ratings yet

- Raise The Limits: Eppendorf Research PlusDocument12 pagesRaise The Limits: Eppendorf Research PlusZahia Slama Ep AchourNo ratings yet

- Qanooneislamorcu 00 JafaDocument646 pagesQanooneislamorcu 00 JafaawNo ratings yet

- BT Word FormsDocument11 pagesBT Word FormsNguyên TrungNo ratings yet

- Casa Cook ArvindDocument65 pagesCasa Cook ArvindLEAN MauritiusNo ratings yet

- A Project Report On: "Recreation Club"Document80 pagesA Project Report On: "Recreation Club"Appz100% (2)

- Explore the Precambrian EraDocument3 pagesExplore the Precambrian EraArjay CarolinoNo ratings yet

- MA 102 Tutorial Sheet No. 2 on Limits and ContinuityDocument1 pageMA 102 Tutorial Sheet No. 2 on Limits and ContinuityKanan KumarNo ratings yet

- Sony Ericsson K610i, K610m, and V630i Service ManualDocument53 pagesSony Ericsson K610i, K610m, and V630i Service ManualJane TodoroskiNo ratings yet

- CPE PRACTICE TEST 2 READINGDocument4 pagesCPE PRACTICE TEST 2 READINGHong Anh0% (1)

- Enzymatic Browning and Its Prevention-American Chemical Society (1995)Document340 pagesEnzymatic Browning and Its Prevention-American Chemical Society (1995)danielguerinNo ratings yet

- 10 Tips To Protect Yourself From Unhealthy AirDocument2 pages10 Tips To Protect Yourself From Unhealthy AirAnonymous XuFb6TNo ratings yet

- Ruby and Pink Sapphire - IntroDocument3 pagesRuby and Pink Sapphire - Introrazanym100% (1)

- Kodak Film StructureDocument40 pagesKodak Film StructureThu Thu SheinNo ratings yet

- Auto IntroductionDocument90 pagesAuto IntroductionShivanand ArwatNo ratings yet

- MỘT SỐ CÂU HỎI TRẮC NGHIỆM ÁP DỤNG CHUYÊN ĐỀ GIỚI TỪ TRONG ĐỀ THI ĐHDocument6 pagesMỘT SỐ CÂU HỎI TRẮC NGHIỆM ÁP DỤNG CHUYÊN ĐỀ GIỚI TỪ TRONG ĐỀ THI ĐHPhương ThảoNo ratings yet

- B. WoolworthsDocument5 pagesB. WoolworthsNjabulo Shakes NtuliNo ratings yet

- Max 223C Pipeline Welding InverterDocument2 pagesMax 223C Pipeline Welding InvertermtonellyNo ratings yet

- Exercise 56 - Narration and SequenceDocument14 pagesExercise 56 - Narration and SequenceLéoKostasNo ratings yet

- Rec2009 025 PDFDocument172 pagesRec2009 025 PDFEkaStaVTVNo ratings yet

- Chapter 6 Exercises (Bonds & Interest)Document2 pagesChapter 6 Exercises (Bonds & Interest)Shaheera SuhaimiNo ratings yet

- Din en 50155 (Vde 0115-200) - 2008-03Document42 pagesDin en 50155 (Vde 0115-200) - 2008-03Collins Akhimien100% (1)

- Tabel Benkelman Beam Baru - AsisDocument21 pagesTabel Benkelman Beam Baru - AsisAsisNo ratings yet

- Bep Rev.c-New 20 MLD WTP, NathavaliDocument380 pagesBep Rev.c-New 20 MLD WTP, NathavaliAnonymous 7l8AIyq2No ratings yet