Professional Documents

Culture Documents

Fast MD5 Implementation in Hardware and Software

Uploaded by

dheeraj8r0 ratings0% found this document useful (0 votes)

123 views3 pagesThis document summarizes optimizations made to MD5 hashing algorithms implemented in both software and hardware. For the software implementation, optimizations including only computing necessary comparisons for the first block, using a circular buffer to fully utilize AVX registers for 4 simultaneous hashes, and limitations preventing 8 simultaneous hashes are discussed. For the hardware implementation on an FPGA, a 32-bit adder, circular shifter, and unrolled design computing rounds in separate modules achieved a throughput of 820 million hashes per second. Benchmark results showed software optimizations increased hashing rates by up to 34.6% over the baseline.

Original Description:

x86_64 SIMD instructions to speedup MD5 calculation.

Original Title

Fast Implementation of MD5

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document summarizes optimizations made to MD5 hashing algorithms implemented in both software and hardware. For the software implementation, optimizations including only computing necessary comparisons for the first block, using a circular buffer to fully utilize AVX registers for 4 simultaneous hashes, and limitations preventing 8 simultaneous hashes are discussed. For the hardware implementation on an FPGA, a 32-bit adder, circular shifter, and unrolled design computing rounds in separate modules achieved a throughput of 820 million hashes per second. Benchmark results showed software optimizations increased hashing rates by up to 34.6% over the baseline.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

123 views3 pagesFast MD5 Implementation in Hardware and Software

Uploaded by

dheeraj8rThis document summarizes optimizations made to MD5 hashing algorithms implemented in both software and hardware. For the software implementation, optimizations including only computing necessary comparisons for the first block, using a circular buffer to fully utilize AVX registers for 4 simultaneous hashes, and limitations preventing 8 simultaneous hashes are discussed. For the hardware implementation on an FPGA, a 32-bit adder, circular shifter, and unrolled design computing rounds in separate modules achieved a throughput of 820 million hashes per second. Benchmark results showed software optimizations increased hashing rates by up to 34.6% over the baseline.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 3

Fast Implementation of MD5:

Hardware and Software

Austin Costley and Chase Kunz

Department of Electrical and Computer Engineering

Utah State University

Logan, Utah 84321

Email: adcostley@gmail.com, chase.kunz@gmail.com

AbstractThis paper explores the MD5 hashing algorithm as it A. Optimisation I

was implemented in hardware and software. Optimisations are

suggested and benchmarked. A six character password using

We saw that many unnecessary calculations were being

upper and lowercase alpha was hashed and provided as a performed while comparing md5 hashes against the pre-image.

challenge to find. The authors found the preimage to be HeyHey Comparisons were performed for four separate blocks for each

by using a password generator and MD5 hashing function. hash. We made only computations necessary for the first block

before comparing it. If a pre-image was not matched for the

I. I NTRODUCTION

first block we moved on to the next hash, saving unneeded

Cryptographic hashing is used in many ways, most com- computations that would normally happen on the preceding

monly it is used to verify data integrity, and store passwords. blocks from occurring. We saw a twenty percent increase on

The MD5 algorithm was developed as a method for generating baseline from this optimisation.

128-bit hash values. Due to the nature of the algorithm the

hash value cannot be used to find the original candidate, or B. Optimisation II

preimage. This property makes the MD5 hash algorithm a With the implementation of AVX intrinsics our program was

prime candidate for password storage on a computer. When able to calculate four hashes simultaneously. Unfortunately the

a user creates a password on a system the password is hashed candidate space is based on twenty-six characters which is not

and stored in a password file. If an attacker is able to gain cleanly divisible by four. At the end of each iteration through

access to the password file he/she would only be able to see the character space there were two extra spaces in our set of

the password hashes. 4 candidates to be hashed in our baseline implementation. We

This paper discusses software and hardware implementations created a circular buffer ensure all hashes were on data that

of the MD5 hashing algorithm, and proposes possible optimi- would be used. From this optimisation we saw a nine percent

sations. increase over baseline.

A. Stucture of Paper C. AVX Limitation

Section II discusses our software Implementation. It in- AVX takes advantage of modern cpus. An advantage over

cludes information regarding optimisation choices, and bench- SSE allows for a computation of the form C = A + B rather

marked results. It also details software choices and attempted than only A = A + B and an extension to 256-bit registers.

optimisations. Section III outlines the hardware implementa- Using these registers, one would ideally be able to compute

tion on the Digilent Nexys 2 development board. It details the 32-bit chunks of eight hashes simultaneously. As this

design decisions, pitfalls, and results. would allow for tremendous speedup, our original goal was

to implement an eight-hash version of the software. Although

II. S OFTWARE I MPLEMENTATION we came very close to accomplishing eight-hash computation

Our basic implementation of MD5 was written in a simple we found that our calculations were limited by the carry-

C program. A function was written to output the MD5 hash bits of the 256-bit registers. As shown in Figure 3, when

corresponding to the character string given. A structure was overflow addition occurs, a carry spills from the odd-index 32-

formed around this function to provide it with every combi- bit integers to the even-index integers. The units carried into

nation of lower and upper case alpha characters and compare the even-index integers corrupt the data held in them. Modulo

them to the target MD5 pre-image. Some basic optimzations 232 addition is needed for data integrity. We implemented 232

were performed to create a baseline version of the code from addition only to find that the overhead needed to perform the

which to further optimize, namely loop unrolling and SIMD operation slowed the program down compared to adding 4

instructions via AVX extensions. Loop unrolling allowed over- 32-bit integers two times. For this reason we calculated four

head to be taken out of the many iterations in MD5 where hashes simultaneously. However, our code is setup to easily

loops would usually be used. AVX details can be seens in implement an eight hashes simultaneously with the availability

Section II-C. of AVX2 extensions.

TABLE I

BASELINE H ASH R ATES

Hash Rate (MH/sec) Improvement

Implementation

Baseline Over Baseline

md5 base 1.79 -

md5 1 2.16 20.26%

md5 2 1.96 9.49%

md5 2.41 34.6%

TABLE II

O PTIMISED H ASH R ATES

Fig. 1. Simulation Output

Hash Rate (MH/sec)

Implementation

Optimised (-O3)

md5 base 4.57

md5 1 4.56

md5 2 4.93

md5 5.02

III. H ARDWARE I MPLEMENTATION Fig. 2. Simulation Top Level Traces

In order to increase the MD5 hash rate we implemented the

MD5 algorithm on a Field Programable Gate Array (FPGA). A block size and the clock frequency and dividing by the cycles

Digilent Nexys 2 development board to implement our design. per block. The size of the hash block was 512-bits and the

We decided to employ a loop unrolled strategy to eliminate clock frequency was 50MHz. If the timing report would have

the overhead of iteration control. The first step of our design generated we could have used the maximum clock frequency

was to develope a 32-bit adder. This was accomplished by possible in for this value. The cycles per block was determined

designing a standard single-bit fulladder with carry-in and by dividing the total simulated time (630 ns) by the clock

carry-out bits. Eight fulladders were implemented together to period (20 ns). Using this calculation the throughput of the

create an 8-bit adder, and four of those were implemented FPGA implmentation was found to be about 820 MH/s (Mega

together to create a 32-bit adder. Designing this module was Hashes / Second).

critical to the MD5 algorithm and provided a great verilog Figure 1 shows the wires relating to the desired hash and the

review. The next module we created was a 32-bit circular resluting hash. The wire names Atar, Btar, Ctar, and Dtar are

shifter. In order to optimise the shifter we used a bit mapping the 32-bit portions of the target hash, and the Afin, Bfin, Cfin,

technique where the bits were re-assigned based on the shift and Dfin are the hash results of the MD5 hashing algorithm.

value. This approach performs the shift faster than a standard Figure 2 shows the top level ouput of the MD5 algorithm. The

shifting operator. top level verilog file initiated a 50Mhz clock, and configured

The basic design of our hardware implementation was to two outputs, port, and start. The start register was set high

create a module for each round. Each iteration would call the when the MD5 module was instantiated. This happened at 5

appropriate round, and have as the input the 32-bit message ns. The port register was set high when the MD5 algorithm had

piece, shift value, 32-bit sin result (T-value), and the current generated the target hash. The cursor shows that this occured

32-bit A, B, C, and D values. The sin values and shift values at 635 ns.

were pre-calculated and hard-coded into the module call. This

IV. C ONCLUSION

was chosen to elminate the need for look up tables and

iteration counters. A tradeoff to this design decision is that Our greatest future software optimizations would be to use

each iteration requires a new wire for each of the 32-bit AVX2 intrinsics, specifically the 32-bit integer add and shift

outputs. Resulting in 256 output wires for round control. instructions. This would allow us to increase from four to

When the design was completed it was also discovered that eight simultaneous hashes. Another optimization that would

this type of loop unrolling created a clock independance that greatly improve our design would be the implementation of

present problems for the throughput calculations. Since the threading to take full advantage of modern cpus multiple core

design could work independently of the onboard clock, the architecture. The next step for the progress in our hardware

ISE Design Suite software did not generate a timing report that

would contain the timing constraints. An alternative approach

was attempted by writing the shift value to a wire on each Fig. 3. AVX 32-bit integer addition overflow

clock cycle, and then using that wire as the input to the round.

Ultimately, this design did not generate the timing report on

implmentation, but it did increase the simulated hash rate.

The throughput calculation was generated by multiplying the

development would be to implement pipelining and further

refine the our implementation to generate timing reports and

timing constraints. This project was a great opportunity to

understand the use of hashing algorithms in computer security,

and to explore a possible attack platform.

You might also like

- Mini-Project Ele654Document10 pagesMini-Project Ele654MazlanNo ratings yet

- The Art of R ProgrammingDocument193 pagesThe Art of R ProgrammingMihai Tentis100% (2)

- Builder's Greywater Guide Branched DrainDocument4 pagesBuilder's Greywater Guide Branched DrainGreen Action Sustainable Technology GroupNo ratings yet

- Dry Hands MinecraftDocument1 pageDry Hands MinecraftBrandon RotzankNo ratings yet

- Advanced Network Security: Chap 4: Hash FunctionsDocument21 pagesAdvanced Network Security: Chap 4: Hash FunctionsSaja KareemNo ratings yet

- Cryptographic Hash Algorithms Performance Finding Using .Net SimulationDocument5 pagesCryptographic Hash Algorithms Performance Finding Using .Net SimulationiirNo ratings yet

- ASIC Design SHA256 ImplementationDocument5 pagesASIC Design SHA256 ImplementationFrancisco BadaróNo ratings yet

- rfc2104Document11 pagesrfc2104la.g.ua.g.ir.li.eNo ratings yet

- Cryptography and Network SecurityDocument22 pagesCryptography and Network SecuritysanjuNo ratings yet

- Information Security Unit-2 - 9 HMACDocument4 pagesInformation Security Unit-2 - 9 HMACLokesh Sai Kumar DasariNo ratings yet

- Hash Function: Message Digest or Simply Hash ValuesDocument20 pagesHash Function: Message Digest or Simply Hash Values18R11A05H4 NEELAYAVALASA MEGHNA PATNAIKNo ratings yet

- An Efficient Implementation of Hash Function Processor For IpsecDocument4 pagesAn Efficient Implementation of Hash Function Processor For IpsecTefo AlajlanNo ratings yet

- Lab2 Crypto MD5 CollisionDocument7 pagesLab2 Crypto MD5 CollisionkokoNo ratings yet

- 12.Hash and MAC AlgorithmsDocument39 pages12.Hash and MAC Algorithmsemmanuelauko4No ratings yet

- Cost-Efficient SHA Hardware AcceleratorsDocument10 pagesCost-Efficient SHA Hardware AcceleratorskattasrinivasNo ratings yet

- 9.1.2.5 Lab - Hashing Things OutDocument4 pages9.1.2.5 Lab - Hashing Things OutPeraNo ratings yet

- MDIw MTQX OADocument4 pagesMDIw MTQX OASagar ChandrakarNo ratings yet

- 20-SHA 512-14-03-2024Document9 pages20-SHA 512-14-03-2024utkarsh.tyagi2021No ratings yet

- WWW Movable Type Co Uk Scripts Sha256 HTMLDocument2 pagesWWW Movable Type Co Uk Scripts Sha256 HTMLBenny LangstonNo ratings yet

- The MD5 Encryption Technique PresentationDocument35 pagesThe MD5 Encryption Technique PresentationSwapnil Bhatnagar0% (1)

- MAC Based On The Hash FunctionDocument13 pagesMAC Based On The Hash FunctionGunasekaran PNo ratings yet

- 14-06-2021-1623667716-6-Ijece-2. Ijece - Analysis of Md5 Implementation and Brute Force Attack On It On FpgaDocument8 pages14-06-2021-1623667716-6-Ijece-2. Ijece - Analysis of Md5 Implementation and Brute Force Attack On It On Fpgaiaset123No ratings yet

- Cryptography ConceptsDocument12 pagesCryptography ConceptsAlexandru IonNo ratings yet

- Analysis of Various Hash FunctionDocument4 pagesAnalysis of Various Hash FunctionInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Arjun 20103029 Iss Assignment 3Document7 pagesArjun 20103029 Iss Assignment 3ANSHUMAN KUMAR KANNAUJIYANo ratings yet

- Week 6 HashingDocument10 pagesWeek 6 Hashingcarious cariousNo ratings yet

- BHA-160: Constructional Design of Hash Function Based On NP-hard ProblemDocument6 pagesBHA-160: Constructional Design of Hash Function Based On NP-hard ProblemZack KourgluNo ratings yet

- 030903-Automatic Checksum GeneratorDocument8 pages030903-Automatic Checksum GeneratorspyeagleNo ratings yet

- The Error Correcting Codes (ECC) Page: Welcome!Document9 pagesThe Error Correcting Codes (ECC) Page: Welcome!ARJUNARCHANANo ratings yet

- Hash Algorithms Explained and Demonstrated Using Linux CommandsDocument3 pagesHash Algorithms Explained and Demonstrated Using Linux CommandsADNANE EL MOURABITINo ratings yet

- CRYPTOGRAPHY HASH FUNCTIONS EXPLAINEDDocument5 pagesCRYPTOGRAPHY HASH FUNCTIONS EXPLAINEDArchana PanwarNo ratings yet

- An Efficient Fault Detection Scheme For The Secure Hash Algorithm SHA-512Document5 pagesAn Efficient Fault Detection Scheme For The Secure Hash Algorithm SHA-512Vijay KannamallaNo ratings yet

- MD5 Algorithm: A 128-Bit Hash FunctionDocument17 pagesMD5 Algorithm: A 128-Bit Hash FunctionAnshumanNo ratings yet

- Hardware Design For SHA-1 Based On FPGADocument3 pagesHardware Design For SHA-1 Based On FPGAtech25sacNo ratings yet

- Hash and MAC Algorithms: Hasibur RahmanDocument14 pagesHash and MAC Algorithms: Hasibur RahmanFarida SiddiqiNo ratings yet

- Chess search algorithms parallelized using two PCsDocument14 pagesChess search algorithms parallelized using two PCscoolguypj1953No ratings yet

- The Whirlpool Secure Hash Function: William StallingsDocument15 pagesThe Whirlpool Secure Hash Function: William StallingsEman AlkurdiNo ratings yet

- A Vlsi Implementation of Secure Hash AlgorithmDocument7 pagesA Vlsi Implementation of Secure Hash AlgorithmjandeepjNo ratings yet

- Research Paper On Md5 AlgorithmDocument5 pagesResearch Paper On Md5 Algorithmh07d16wn100% (1)

- Anshuman Iss Assign-03Document10 pagesAnshuman Iss Assign-03ANSHUMAN KUMAR KANNAUJIYANo ratings yet

- SHA-1 Hashing Algorithm ExplainedDocument17 pagesSHA-1 Hashing Algorithm ExplainedManu PouloseNo ratings yet

- Analysis of The PE Rich Header and Malware LinkingDocument17 pagesAnalysis of The PE Rich Header and Malware LinkingRennyNo ratings yet

- An Empirical Study of Collision Rates in SimHash Using MD5Document4 pagesAn Empirical Study of Collision Rates in SimHash Using MD5Nairouz AlzinNo ratings yet

- Modified Md5 Algorithm For Low End Iot Edge Devices: Viraj Khatri Ms. Vanita AgarwalDocument6 pagesModified Md5 Algorithm For Low End Iot Edge Devices: Viraj Khatri Ms. Vanita AgarwalNairouz AlzinNo ratings yet

- Cryptography and Network Security Module 28- Hash AlgorithmsDocument13 pagesCryptography and Network Security Module 28- Hash AlgorithmsabyNo ratings yet

- Cryptography Hash Functions: STD Code Full Name Class MarksDocument21 pagesCryptography Hash Functions: STD Code Full Name Class MarksBrikhov XNo ratings yet

- Crack passwords in a day using LM, NT, MD5 hashesDocument15 pagesCrack passwords in a day using LM, NT, MD5 hashesA Divya PreethaNo ratings yet

- HASH3.1Document74 pagesHASH3.1Vishal Kumar 1902712No ratings yet

- Unit 2 CryptographyDocument60 pagesUnit 2 CryptographyAkash ChouhanNo ratings yet

- Towards The Synthesis of Context-Free GrammarDocument8 pagesTowards The Synthesis of Context-Free Grammarscribd-centralNo ratings yet

- Lab 8Document14 pagesLab 8Avinash AvuthuNo ratings yet

- Implementing A Histogram Equalization AlgorithmDocument11 pagesImplementing A Histogram Equalization AlgorithmmuucoolNo ratings yet

- BIS RaysRecogDocument16 pagesBIS RaysRecogSaranyaRoyNo ratings yet

- Performance of Symmetric Ciphers and One-Way Hash Functions: 1 RationaleDocument7 pagesPerformance of Symmetric Ciphers and One-Way Hash Functions: 1 RationaleThanh PhamNo ratings yet

- Prepared By:: Vijay Thapa Shashank Lamshal Amit Magdum Uday Satone Under Guidance of Prof - Moshin MullaDocument14 pagesPrepared By:: Vijay Thapa Shashank Lamshal Amit Magdum Uday Satone Under Guidance of Prof - Moshin MullaTHAPA VIJAYNo ratings yet

- ARM Processor History and ArchitectureDocument15 pagesARM Processor History and ArchitectureEr Shreyas ShahNo ratings yet

- Heyhyid: Emulation of Cache CoherenceDocument5 pagesHeyhyid: Emulation of Cache CoherenceAdamo GhirardelliNo ratings yet

- S1, 2019 - V:1 (Monday, 25.02.2019, 16:00) Use For Class CommunicationsDocument5 pagesS1, 2019 - V:1 (Monday, 25.02.2019, 16:00) Use For Class CommunicationsMister007jhNo ratings yet

- Cryptography and Network Security by William Stallings Chapter 12 - Hash Algorithms and HMACDocument27 pagesCryptography and Network Security by William Stallings Chapter 12 - Hash Algorithms and HMACDuttaUdayaVenkataChegondiNo ratings yet

- 398 f11 hw3Document4 pages398 f11 hw3Jake BrownNo ratings yet

- ColisionDocument7 pagesColisionJuan GuimarãesNo ratings yet

- Hashing LabDocument3 pagesHashing LabBroe MelloNo ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- Optimization and statistical methods for high frequency tradingDocument10 pagesOptimization and statistical methods for high frequency tradingdheeraj8rNo ratings yet

- Kalman Filter Smooths Price TrendsDocument29 pagesKalman Filter Smooths Price Trendsdheeraj8rNo ratings yet

- Cimple: Instruction and Memory Level Parallelism: A DSL For Uncovering ILP and MLPDocument16 pagesCimple: Instruction and Memory Level Parallelism: A DSL For Uncovering ILP and MLPdheeraj8rNo ratings yet

- Quantitative Economics With Python PDFDocument1,890 pagesQuantitative Economics With Python PDFdheeraj8rNo ratings yet

- P O I S: Roprietary Versus PEN Nstruction ETSDocument11 pagesP O I S: Roprietary Versus PEN Nstruction ETSdheeraj8rNo ratings yet

- GCCBuiltins ESECFSE19 PreprintDocument12 pagesGCCBuiltins ESECFSE19 Preprintdheeraj8rNo ratings yet

- Could A Neuroscientist Understand A Microprocessor?: Eric Jonas Konrad KordingDocument15 pagesCould A Neuroscientist Understand A Microprocessor?: Eric Jonas Konrad Kordingdheeraj8rNo ratings yet

- 10 3905jod 2018 26 2 019 PD PDFDocument20 pages10 3905jod 2018 26 2 019 PD PDFdheeraj8rNo ratings yet

- Fast, Multicore-Scalable Low-Fragmentation Memory AllocationDocument16 pagesFast, Multicore-Scalable Low-Fragmentation Memory Allocationdheeraj8rNo ratings yet

- 1611 00467v1 PDFDocument15 pages1611 00467v1 PDFdheeraj8rNo ratings yet

- Techniques For Scientific C++ PDFDocument59 pagesTechniques For Scientific C++ PDFdheeraj8rNo ratings yet

- Table of ContentDocument6 pagesTable of Contentlinhletter123No ratings yet

- Let's Be Rational: J Ac06 Vog07Document12 pagesLet's Be Rational: J Ac06 Vog07dheeraj8rNo ratings yet

- Calibrating The Mean-Reversion Parameter in The Hull-White Model Using Neural Networks: Methods and ProtocolsDocument15 pagesCalibrating The Mean-Reversion Parameter in The Hull-White Model Using Neural Networks: Methods and Protocolsdheeraj8rNo ratings yet

- Limit Order Books ExplainedDocument38 pagesLimit Order Books Explaineddheeraj8rNo ratings yet

- Price Impact Models & Optimal Execution: Ren e CarmonaDocument25 pagesPrice Impact Models & Optimal Execution: Ren e Carmonadheeraj8rNo ratings yet

- Introduction To Operating SystemsDocument18 pagesIntroduction To Operating Systemsdheeraj8rNo ratings yet

- Category Theory For Programmers PDFDocument492 pagesCategory Theory For Programmers PDFdheeraj8rNo ratings yet

- Unix System Programming in Objective CamlDocument143 pagesUnix System Programming in Objective CamlSeñor SmilesNo ratings yet

- Alphas ExamplesDocument22 pagesAlphas Examplescclaudel09No ratings yet

- Performance v. Turnover: A Story by 4,000 AlphasDocument17 pagesPerformance v. Turnover: A Story by 4,000 Alphasdheeraj8rNo ratings yet

- ProgrammingGroundUp 1 0 BooksizeDocument326 pagesProgrammingGroundUp 1 0 BooksizemanusoftarNo ratings yet

- Why Functional Programming MattersDocument23 pagesWhy Functional Programming MattersMamaramNo ratings yet

- Good Enough Practices For Scientific ComputingDocument21 pagesGood Enough Practices For Scientific ComputingDavidNo ratings yet

- Regulating Drugs, Cosmetics and Medical Devices in IndiaDocument62 pagesRegulating Drugs, Cosmetics and Medical Devices in Indiadheeraj8rNo ratings yet

- Challenges of MM On NUMADocument26 pagesChallenges of MM On NUMAdheeraj8rNo ratings yet

- Understanding Evolutionary Potential in Virtual CPU Instruction Set ArchitecturesDocument14 pagesUnderstanding Evolutionary Potential in Virtual CPU Instruction Set Architecturesdheeraj8rNo ratings yet

- On Becoming A QuantDocument10 pagesOn Becoming A Quantdheeraj8rNo ratings yet

- Ahmad Humayun SohailDocument6 pagesAhmad Humayun SohailHumayun SohailNo ratings yet

- A1.2.3 Method Statement 4a Redacted Version2Document98 pagesA1.2.3 Method Statement 4a Redacted Version2ChanelNo ratings yet

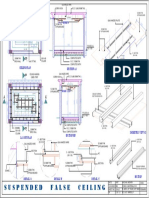

- Gypsum Ceiling PDFDocument1 pageGypsum Ceiling PDFAanchal Mishra100% (1)

- Gate Mock Test1Document17 pagesGate Mock Test1Gopinathan SudheerNo ratings yet

- College Report of Optical Burst SwitchingDocument21 pagesCollege Report of Optical Burst Switchingimcoolsha999No ratings yet

- bbk-lt2614-lt3214 Service Manual PDFDocument42 pagesbbk-lt2614-lt3214 Service Manual PDFrj arcinasNo ratings yet

- Brief Summary of The Original COCOMO ModelDocument5 pagesBrief Summary of The Original COCOMO ModelTirthajit SinhaNo ratings yet

- The Top 200 International Design Firms - ENR - Engineering News Record - McGraw-Hill ConstructionDocument4 pagesThe Top 200 International Design Firms - ENR - Engineering News Record - McGraw-Hill ConstructiontarekhocineNo ratings yet

- PD 957 AND BP 220 HOUSING DESIGN STANDARDSDocument5 pagesPD 957 AND BP 220 HOUSING DESIGN STANDARDSGeraldine F. CalubNo ratings yet

- Method Statement For Cable & TerminationDocument6 pagesMethod Statement For Cable & TerminationRajuNo ratings yet

- Eurox Cross Flow ScrubberDocument8 pagesEurox Cross Flow ScrubberRobin LayogNo ratings yet

- Holux M-1000C Bluetooth GPS Logger Manual GuideDocument22 pagesHolux M-1000C Bluetooth GPS Logger Manual Guidenabiloo2003No ratings yet

- Siemens 1LE1 PDFDocument308 pagesSiemens 1LE1 PDFharold100% (1)

- FlowCon General InstructionDocument4 pagesFlowCon General InstructionGabriel Arriagada UsachNo ratings yet

- Scrap NFL PanipatDocument9 pagesScrap NFL PanipatJitenderSinghNo ratings yet

- MS 01 182Document5 pagesMS 01 182kicsnerNo ratings yet

- B737-B787 QRH Differences: 787 NNC Includes Emergency DescentDocument13 pagesB737-B787 QRH Differences: 787 NNC Includes Emergency DescentUfuk AydinNo ratings yet

- Selection ToolsDocument13 pagesSelection ToolsDominador Gaduyon DadalNo ratings yet

- Oracle Database Question Bank 1Document5 pagesOracle Database Question Bank 1subbaraomca2010No ratings yet

- Artikel Jurnal - Fundamental Differences of Transition To Industry 4.0 From Previous Industrial RevolutionsDocument9 pagesArtikel Jurnal - Fundamental Differences of Transition To Industry 4.0 From Previous Industrial RevolutionsJohny DoelNo ratings yet

- Product Portfolio ManagementDocument10 pagesProduct Portfolio ManagementSandeep Singh RajawatNo ratings yet

- Unit4questions 100415042439 Phpapp01Document4 pagesUnit4questions 100415042439 Phpapp01Mohamad HishamNo ratings yet

- Load-Modulated Arrays Emerging MIMO TechnologyDocument83 pagesLoad-Modulated Arrays Emerging MIMO TechnologysmkraliNo ratings yet

- JEDI Slides Intro1 Chapter 02 Introduction To JavaDocument17 pagesJEDI Slides Intro1 Chapter 02 Introduction To JavaredbutterflyNo ratings yet

- Detector of FM SignalDocument4 pagesDetector of FM SignalR. JaNNaH100% (1)

- KernelDocument326 pagesKernelSkyezine Via Kit FoxNo ratings yet

- Nord Motors Manual BookDocument70 pagesNord Motors Manual Bookadh3ckNo ratings yet

- Aluminium GMAW GuideDocument32 pagesAluminium GMAW GuideDaniel Salinas100% (2)