Professional Documents

Culture Documents

1AVR Juego de Instrucciones Resumido

Uploaded by

Luis Alfonso Martinez FdezOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1AVR Juego de Instrucciones Resumido

Uploaded by

Luis Alfonso Martinez FdezCopyright:

Available Formats

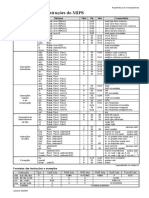

AVR Instruction Set Printed on 16/03/2010

Transfer Arithmetic / Logic Jump / Call / Branch Bit / Others

Register Arithmetic Jump Bit Set

MOV Rt, Rs Rt Rs ADD Rt, Rs Rt Rt + Rs RJMP k12 PC PC + k12 BSET s SREG(b) 1

MOVW Rt2, Rs2 Rt+1:Rt Rs+1:Rs ADC Rt, Rs Rt Rt + Rs + C IJMP PC Z BCLR s SREG(b) 0

ADIW Rd, k6 Rd Rd + k6 EIJMP PC RAMPZ:Z SBI a, b IO(a)(b) 1

Inmediate SUB Rt, Rs Rt Rt - Rs JMP k22 PC k22 CBI a, b IO(a)(b) 0

LDI Rh, k8 Rh k8 SBC Rt, Rs Rt Rt - Rs - C BST Rt, b T Rt(b)

SBIW Rd, k6 Rd+1:Rd Rd+1:Rd - k6 Call/Return BLD Rt, b Rt(b) T

SER Rh Rh 0xFF SUBI Rh, k8 Rh Rh - k8 RCALL k12 PCPC+k12; STACKPC

SBCI Rh, k8 Rh Rh - k8 - C ICALL PC Z; STACK PC SEC C=1

Direct INC Rt Rt Rt +1 EICALL PCRAMPZ:Z; STACKPC CLC C=0

LDS Rt, k16 Rt DM(k16) DEC Rt Rt Rt -1 CALL k22 PC k22; STACK PC SEN N=1

STS k16, Rs DM(k16) Rt CP Rt, Rs Rt - Rs RET PC STACK CLN N=0

CPC Rt, Rs Rt - Rs - C RETI PC STACK; I 1 SEZ Z=1

Indirect CPI Rh, k8 Rh - k8 CLZ Z=0

LD Rt, Rp Rt DM(Rp) Branch SES S=1 (S = V eor N)

LD Rt, -Rp Rp--; Rt DM(Rp) Logic CPSE Rt, Rs Skip next instr if Rt=Rs CLS S=0 (S = V eor N)

LD Rt, Rp+ Rt DM(Rp); Rp++ AND Rt, Rs Rt Rt Rs SEV V=1

LDD Rt, Ry+k6 Rt DM(Ry+k6) ANDI Rh, k8 Rh Rh k8 SBRC Rs, b Skip next instr if Rs(b)=0 CLV V=0

ST Rp, Rs DM(Rp) Rs OR Rt, Rs Rt Rt v Rs SBRS Rs, b Skip next instr if Rs(b)=1 SET T=1

ST -Rp, Rs Rp--; DM(Rp) Rs ORI Rh, k8 Rh Rh v k8 CLT T=0

ST Rp+, Rs DM(Rp) Rs; Rp++ EOR Rt, Rs Rt Rt eor Rs SBIC A, b Skip next instr if IO(A)(b)=0 SEH H=1

ST Ry+k6, Rs DM(Ry+k6) Rs COM Rt Rt not Rt SBIS A, b Skip next instr if IO(A)(b)=1 CLH H=0

NEG Rt Rt -Rt SEI I=1

Stack BRBC s, k7 Branch if SREG(b)=0 CLI I=0

PUSH Rs STACK Rs ROR Rt Rotate Right BRBS s, k7 Branch if SREG(b)=1

POP Rt Rs STACK ROL Rt Rotate Left SWAP Rt Rt(7:4) Rt(3:0)

LSR Rt Logic Shift Right BRSH k7 Branch if same or higer (unsig)

I/O LSL Rt Logic Shift Left BRLO k7 Branch if lower (unsig) MCU Control

IN Rt, A Rt IO(A) ASR Rt Arithmetic Shift Right BRGE k7 Branch if grater or equal (sig) NOP No operacin

OUT A, Rs IO(A) Rs BRLT k7 Branch if less than (sig) BREAK Break

SBR Rh, k8 Rh Rh v k8 BREQ k7 Branch if equal SLEEP Sleep

Program Memory CBR Rh, k8 Rh Rh not k8 BRNE k7 Branch if not equal WDR Watchdog Reset

LPM R0 PM(Z) TST Rt Rt = 0? (Rt Rt Rt) BRCS k7 Branch if carry set

LPM Rt, Z Rt PM(Z) CLR Rt Rt 0 (Rt Rt eor Rt) BRCC k7 Branch if carry clear

LPM Rt, Z+ Rt PM(Z); Z++ BRMI k7 Branch if minus

ELPM R0 PM(RAMPZ:Z) Multiply BRPL k7 Branch if plus

ELPM Rt, Z Rt PM(RAMPZ:Z) MUL Rt, Rs R1:R0 Rt * Rs BRHS k7 Branch if half-carry set

ELPM Rt, Z+ Rt PM(RAMPZ:Z); Z++ MULS Rh, Ri R1:R0 Rh * Ri (signed) BRHC k7 Branch if half-carry clear

SPM PM(Z) R0 MULSU Rm, Rn R1:R0 Rm * Rn (sig/unsig) BRTS k7 Branch if T set

BRTC k7 Branch if T clear

FMUL Rm, Rn R1:R0 (Rt * Rs) << 1 BRVS k7 Branch if overflow set

FMULS Rm, Rn R1:R0 (Rh * Ri) << 1 BRVC k7 Branch if overflow clear

FMULSU Rm, Rn (signed) (Rm * Rn) << 1

R1:R0 BRIE k7 Branch if interrupt mask set

(sig/uns) BRID k7 Branch if interrupt mask clear

Register Constant RAMPZ Segment Register

Rs, Rt Ordinary Source and Target register R0..R31 k6 6-Bit-Constant 0..63

Rs2, Rt2 Ordinary Source and Target even register R0, R2, R4...R30 k7 7-Bit-Constant -64..+63 DM(..) Data memory

Rh, Ri Source and Target register between R16..R31 k8 8-Bit-Constant 0..255 PM(..) Program memory

Rm, Rn Source and Target register between R16..R23 k12 12-Bit-Constante -2048..+2047

Rd Twin register R24(R25), R26(R27), R28(R29), R30(R31) k16 16-Bit-Address 0..65535 Instructions in ITALICS are pseudointructions

Rp Pointer register X=R26(R27), Y=R28(R29), Z=R30(R31) k22 22-Bit-Address 0..4M

Ry Pointer register with displacement Y=R28(R29), Z=R30(R31)

Bit Port

s State Register bit 0..7 A Ordinary Port address 0..63

b Bit position 0..7 a Lower page port address 0..31

The AVR instruction set is more orthogonal than most eight-bit microcontrollers, in particular the PIC microcontrollers with which AVR competes today. Arithmetic operations work on registers R0-R31 but not directly

on RAM and take one clock cycle, except for multiplication and word-wide addition (ADIW and SBIW) which take two cycles. The mostly-regular instruction set makes programming it using C (or even Pascal)

compilers pretty straightforward.

The data address space consists of the register file, I/O registers, and SRAM. The AVRs have 32 single-byte registers and are classified as 8-bit RISC devices. RAM and I/O space can be accessed only by copying to

or from registers. Indirect access (including optional postincrement, predecrement or constant displacement) is possible through registers X, Y, and Z. All accesses to RAM takes two clock cycles. Moving between

registers and I/O is one cycle. Moving eight or sixteen bit data between registers or constant to register is also one cycle. Reading program memory (LPM) takes three cycles.

There are two types of conditional branches: skips and jumps to address. Skips (SBxx) test an arbitrary bit in a register or I/O and skip the next instruction if the test was true. Conditional branches (BRxx) can test an

ALU flag and jump to specified address.

You might also like

- Instruction Set Summary for ATmega328/P MicrocontrollerDocument4 pagesInstruction Set Summary for ATmega328/P MicrocontrollerLeonardo AlvesNo ratings yet

- LC320Instructions 144663026Document16 pagesLC320Instructions 144663026Đức KhánhNo ratings yet

- COMPARE Signed and Unsigned Comparison InstructionsDocument3 pagesCOMPARE Signed and Unsigned Comparison InstructionsEmre CakmakyurduNo ratings yet

- Hoja Examen AVRDocument3 pagesHoja Examen AVRIceyNo ratings yet

- Chapter 4 Arithmetic and Logic ARMDocument31 pagesChapter 4 Arithmetic and Logic ARMzakariaNo ratings yet

- MIPS Instruction Set OverviewDocument1 pageMIPS Instruction Set OverviewAisha MeenaNo ratings yet

- Commands in AVR-assembler LanguageDocument1 pageCommands in AVR-assembler LanguageFrutzNo ratings yet

- Experiment No.: 3: PC With Atmel StudioDocument11 pagesExperiment No.: 3: PC With Atmel StudioDhrumil ManiyarNo ratings yet

- Instruction SetDocument1 pageInstruction Setmakerlog200No ratings yet

- MicroControllers HandbookDocument13 pagesMicroControllers Handbookjhon doeNo ratings yet

- combinepdfDocument14 pagescombinepdfGaurav KhandelwalNo ratings yet

- Instructions and Operands for the 8051 MicrocontrollerDocument7 pagesInstructions and Operands for the 8051 MicrocontrollerPhilomina EkkaNo ratings yet

- Tabela de Des ResiduaisDocument1 pageTabela de Des ResiduaisBrunoGalileuNo ratings yet

- AVR Instructions 1Document133 pagesAVR Instructions 1Mlondo Khanyisani EmmanuelNo ratings yet

- ARM® and Thumb®-2 Instruction Set Quick Reference CardDocument6 pagesARM® and Thumb®-2 Instruction Set Quick Reference CardpavankrishnatNo ratings yet

- Atmega32 Instruction Set SummaryDocument3 pagesAtmega32 Instruction Set SummaryNumo BamiNo ratings yet

- Chapter SevenDocument29 pagesChapter Sevenremi1989No ratings yet

- 12, Tut-4Document4 pages12, Tut-4Jatin SharmaNo ratings yet

- Set Instrucciones PDFDocument3 pagesSet Instrucciones PDFdatazo infoNo ratings yet

- AtmelDocument4 pagesAtmelBaba YagaNo ratings yet

- AVR Instruction Set SummaryDocument4 pagesAVR Instruction Set SummarySinan PravadaliogluNo ratings yet

- How Computers Work Assembly Tools Calling Conventions: Processor State Instruction Memory Fetch/Execute LoopDocument16 pagesHow Computers Work Assembly Tools Calling Conventions: Processor State Instruction Memory Fetch/Execute LoopZammadNo ratings yet

- Atmel 0856 Avr Instruction Set ManualDocument9 pagesAtmel 0856 Avr Instruction Set ManualGabriel Alejandro Francisco Gallardo TineoNo ratings yet

- Skup Instrukcija ATxmegaDocument4 pagesSkup Instrukcija ATxmegaskvlukaNo ratings yet

- Y Y RF M R D F Q R D F Q R D RR Ar G R D F Q R D F Q R D RR Ar G D R F M F QRF QR RR Ar G D V R VM QQ B R Q Rar R RR R RRDocument4 pagesY Y RF M R D F Q R D F Q R D RR Ar G R D F Q R D F Q R D RR Ar G D R F M F QRF QR RR Ar G D V R VM QQ B R Q Rar R RR R RRmn4webNo ratings yet

- MIPS32 Instruction Set Quick Reference: L B - F O J A B (N: O D S)Document2 pagesMIPS32 Instruction Set Quick Reference: L B - F O J A B (N: O D S)JayNo ratings yet

- Statika Excel BagusDocument11 pagesStatika Excel BagusWindiNo ratings yet

- ATmega328P - Instruction Set SummaryDocument4 pagesATmega328P - Instruction Set SummaryE&GNo ratings yet

- Code AsemblyDocument87 pagesCode AsemblyHieu Vo QuocNo ratings yet

- Instruction Set Summary: Mnemonics Operands Description Operation Flags #ClocksDocument3 pagesInstruction Set Summary: Mnemonics Operands Description Operation Flags #ClocksWalter Tintaya QuispeNo ratings yet

- Topic 6 Shift & Rotate Instructions (ISMAIL - FKEUTM 2018)Document26 pagesTopic 6 Shift & Rotate Instructions (ISMAIL - FKEUTM 2018)Aya AmirNo ratings yet

- ph208 Up Slides 1bDocument6 pagesph208 Up Slides 1bHarshita TripathiNo ratings yet

- Kumpulan Instruksi Atmega 8535Document2 pagesKumpulan Instruksi Atmega 8535sword of excaliburNo ratings yet

- Reference SheetDocument3 pagesReference Sheetandro baletiNo ratings yet

- ATmega16 ATmega32Document9 pagesATmega16 ATmega32binitdubeyNo ratings yet

- Lecture6-Bit AddressabilityDocument27 pagesLecture6-Bit AddressabilityJawad shah SayedNo ratings yet

- ATtiny13, ATtiny2313, Instruction SetDocument19 pagesATtiny13, ATtiny2313, Instruction SetMihai PaunNo ratings yet

- SurveysDocument1 pageSurveysFrancis Jem ReyesNo ratings yet

- Assembly Mi PsDocument2 pagesAssembly Mi Psgabriel sousaNo ratings yet

- Instr Set PDFDocument150 pagesInstr Set PDFvannybowoooNo ratings yet

- Michael H. Perrott (C) 2002: Open Circuit Time Constant Calculations 6.301 - Spring 2002Document2 pagesMichael H. Perrott (C) 2002: Open Circuit Time Constant Calculations 6.301 - Spring 2002Andrea FasatoNo ratings yet

- Labsheet 4 Dec30043Document15 pagesLabsheet 4 Dec30043Azmienz HierzanzNo ratings yet

- INSTRUCCIONES DE CARGA Y ALMACENAMIENTODocument3 pagesINSTRUCCIONES DE CARGA Y ALMACENAMIENTOTonantzin GuerreroNo ratings yet

- Outline: A Simple MicroprocessorDocument14 pagesOutline: A Simple MicroprocessorGide BaniekNo ratings yet

- Memory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Document2 pagesMemory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Emre CakmakyurduNo ratings yet

- Memory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Document2 pagesMemory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Emre CakmakyurduNo ratings yet

- Z80 ProgrammingDocument30 pagesZ80 ProgrammingDusan TrisicNo ratings yet

- Diesel engine efficiency and power formulasDocument2 pagesDiesel engine efficiency and power formulasPabloAmbatoNo ratings yet

- WOZPAK Sweet-16 Article 1Document13 pagesWOZPAK Sweet-16 Article 1Moe B. Us100% (1)

- Sum Evenodd of ArrayDocument1 pageSum Evenodd of ArrayTr Ần NghĩaNo ratings yet

- Chapter2 Part 2 Machine Instructions and ProgramsDocument38 pagesChapter2 Part 2 Machine Instructions and ProgramsayushNo ratings yet

- MIPS CARD TITLEDocument1 pageMIPS CARD TITLEHamza AsimNo ratings yet

- Problem Solutions To Problems Marked With A in Logic Computer Design Fundamentals, Ed. 2Document2 pagesProblem Solutions To Problems Marked With A in Logic Computer Design Fundamentals, Ed. 2Jitendra SinghNo ratings yet

- Case No., Edge Restraints Boundary Values Special CasesDocument4 pagesCase No., Edge Restraints Boundary Values Special Casesmn4webNo ratings yet

- Armv 7Document6 pagesArmv 7MeowNo ratings yet

- ATtiny24/44/84 Instruction Set SummaryDocument2 pagesATtiny24/44/84 Instruction Set SummaryRajsekhar NagNo ratings yet

- ThumbRefV2 BetaDocument1 pageThumbRefV2 BetagregNo ratings yet

- Cortex M4 Instruction Set OverviewDocument2 pagesCortex M4 Instruction Set OverviewQuique MoralesNo ratings yet

- Solution Manual for an Introduction to Equilibrium ThermodynamicsFrom EverandSolution Manual for an Introduction to Equilibrium ThermodynamicsNo ratings yet

- Minimum Salaries White Collar Workers 2022Document2 pagesMinimum Salaries White Collar Workers 2022Luis Alfonso Martinez FdezNo ratings yet

- Ananev 2019 J. Phys. Conf. Ser. 1202 012002 PDFDocument9 pagesAnanev 2019 J. Phys. Conf. Ser. 1202 012002 PDFLuis Alfonso Martinez FdezNo ratings yet

- Ludwig Van Beethoven 1 PDFDocument10 pagesLudwig Van Beethoven 1 PDFluciaNo ratings yet

- DSP08 DSP UP ArchitecturesDocument32 pagesDSP08 DSP UP ArchitecturesLuis Alfonso Martinez FdezNo ratings yet

- Advanced Electronic Circuits - TietzeDocument518 pagesAdvanced Electronic Circuits - TietzeJordy Bryan Mayta SalhuaNo ratings yet

- Self-Oscillating CMOS Class D Amplifier Optimized For Low OutputDocument64 pagesSelf-Oscillating CMOS Class D Amplifier Optimized For Low OutputLuis Alfonso Martinez FdezNo ratings yet

- AmsonlineDocument10 pagesAmsonlineLuis Alfonso Martinez FdezNo ratings yet

- Oscilloscope's Signal IntegrityDocument18 pagesOscilloscope's Signal IntegrityJose MiguelNo ratings yet

- Introduction To The Devanagari ScriptDocument24 pagesIntroduction To The Devanagari ScriptasoboyNo ratings yet

- Ludwig Van Beethoven 1 PDFDocument10 pagesLudwig Van Beethoven 1 PDFluciaNo ratings yet

- Refrigerant Pipes CalculationDocument2 pagesRefrigerant Pipes Calculationamo3330100% (2)

- Encryption 2018Document37 pagesEncryption 2018Luis Alfonso Martinez FdezNo ratings yet

- Manual de Transmisión de CalorDocument36 pagesManual de Transmisión de CalorLuis Alfonso Martinez FdezNo ratings yet

- Encryption 2018Document37 pagesEncryption 2018Luis Alfonso Martinez FdezNo ratings yet

- Ug470 7series Config PDFDocument180 pagesUg470 7series Config PDFLuis Alfonso Martinez FdezNo ratings yet

- A Switched-Winding Transformer With Low Quiescent Loss To Meet The Level VI Efficiency Standard at High Power DensityDocument7 pagesA Switched-Winding Transformer With Low Quiescent Loss To Meet The Level VI Efficiency Standard at High Power DensityLuis Alfonso Martinez FdezNo ratings yet

- Efficiency Enhancement of A Wimax Switching Mode Gan Power Amplifier Through Layout Optimization of Distributed Harmonic Matching NetworksDocument4 pagesEfficiency Enhancement of A Wimax Switching Mode Gan Power Amplifier Through Layout Optimization of Distributed Harmonic Matching NetworksLuis Alfonso Martinez FdezNo ratings yet

- Smo 64Document5 pagesSmo 64GabrielRichardHeizerMillerNo ratings yet

- FPGAs Fundamentals Advanced Features and Applications in Industrial Electronics 2017 PDFDocument251 pagesFPGAs Fundamentals Advanced Features and Applications in Industrial Electronics 2017 PDFLuis Alfonso Martinez FdezNo ratings yet

- A Switched-Winding Transformer With Low Quiescent Loss To Meet The Level VI Efficiency Standard at High Power DensityDocument7 pagesA Switched-Winding Transformer With Low Quiescent Loss To Meet The Level VI Efficiency Standard at High Power DensityLuis Alfonso Martinez FdezNo ratings yet

- The Radio Handbook 15E - 1959Document810 pagesThe Radio Handbook 15E - 1959suzycreamcheeze100% (1)

- Frequency Tracking Burst-Mode PDM-controlled Class-D Zero Voltage Soft-Switching Resonant Converter For Inductive Power Transfer ApplicationsDocument8 pagesFrequency Tracking Burst-Mode PDM-controlled Class-D Zero Voltage Soft-Switching Resonant Converter For Inductive Power Transfer ApplicationsLuis Alfonso Martinez FdezNo ratings yet

- AVR Assembler User GuideDocument26 pagesAVR Assembler User Guidewm53100% (1)

- API and ASME steel pipes specificationsDocument2 pagesAPI and ASME steel pipes specificationsRiad.belNo ratings yet

- MIG Welding Tips and TechniquesDocument3 pagesMIG Welding Tips and TechniquesQA QCNo ratings yet

- Postflood Restartprocedure HOFFMAN LAMSONDocument1 pagePostflood Restartprocedure HOFFMAN LAMSONLuis Fernando BravoNo ratings yet

- MITSUBISHI E700 - Instruction - ManualDocument131 pagesMITSUBISHI E700 - Instruction - ManualdanielNo ratings yet

- MRL Installation Manual AdditionalDocument17 pagesMRL Installation Manual AdditionalJean Luis SaviñónNo ratings yet

- Presettable synchronous BCD decade counter data sheetDocument11 pagesPresettable synchronous BCD decade counter data sheetIrvson SilveiraNo ratings yet

- Fundamentals of Computers: Reema TharejaDocument39 pagesFundamentals of Computers: Reema TharejaYash SharmaNo ratings yet

- UAV Pre Flight Checklist v2.0 - The Drone TrainerDocument2 pagesUAV Pre Flight Checklist v2.0 - The Drone TrainerAldo SetiawanNo ratings yet

- Merlin Gerin Medium VoltageDocument10 pagesMerlin Gerin Medium VoltagekjfenNo ratings yet

- ECE 313 Quiz #1 SolutionsDocument2 pagesECE 313 Quiz #1 SolutionsIdris Jeffrey MangueraNo ratings yet

- Field ManualDocument22 pagesField ManualDamienNo ratings yet

- 6 Operate Main and Auxiliary Machinery and Associated Control SystemsDocument5 pages6 Operate Main and Auxiliary Machinery and Associated Control SystemsridhoNo ratings yet

- 400 Series Skid Steer Engine OverviewDocument19 pages400 Series Skid Steer Engine OverviewJuan Betancur OsorioNo ratings yet

- Etc Lmg-Ssc12a64Document10 pagesEtc Lmg-Ssc12a64Dubis EszterNo ratings yet

- Unisource Series 2612 HoseDocument1 pageUnisource Series 2612 HosejoeNo ratings yet

- GME TAR Book Comp WiseDocument117 pagesGME TAR Book Comp WiseOm Prakash RajNo ratings yet

- 2002 Cavalier Transmission DropDocument14 pages2002 Cavalier Transmission DropAlex HirzelNo ratings yet

- 2017 BMW R Ninet Scrambler 71662Document163 pages2017 BMW R Ninet Scrambler 71662Anas KhanNo ratings yet

- OPTIKA B-159 Technical Datasheet enDocument2 pagesOPTIKA B-159 Technical Datasheet enPELITA DWI ASANo ratings yet

- Steca PV Off Grid Catalogue 2014-2015 enDocument39 pagesSteca PV Off Grid Catalogue 2014-2015 entunznathNo ratings yet

- 9 Power TrainDocument146 pages9 Power TraineduamaNo ratings yet

- Bipolar Forceps 3-3 - 8in CrvreuseDocument4 pagesBipolar Forceps 3-3 - 8in CrvreuseSalma El MamouniNo ratings yet

- Technical Hager PDFDocument32 pagesTechnical Hager PDFjohnvar04No ratings yet

- Alabang MCSPDocument229 pagesAlabang MCSP[AP-STUDENT] Ina Rose LaquiNo ratings yet

- Service Manual: TAC-42CF TAC-42CHFDocument17 pagesService Manual: TAC-42CF TAC-42CHFMuhammad FirdausNo ratings yet

- Physical Transmission MediaDocument47 pagesPhysical Transmission MediaabdulazizNo ratings yet

- Operator Protective Guards level 2Document7 pagesOperator Protective Guards level 2Irfan SaeedNo ratings yet

- Wireless Design For Power Theft Monitoring: Parul Ranjan, Namita Mehra, Prof. T.A. More, Shripad BokandDocument4 pagesWireless Design For Power Theft Monitoring: Parul Ranjan, Namita Mehra, Prof. T.A. More, Shripad BokandAyshwar Venkatesh100% (1)

- Johnson - Evinrude 1990-2001 Servis ManualDocument552 pagesJohnson - Evinrude 1990-2001 Servis Manualadolfoc26191% (44)

- WEG Hydrogenerators Gh20 14824113 Manual EnglishDocument51 pagesWEG Hydrogenerators Gh20 14824113 Manual EnglishGuilherme RosaNo ratings yet