Professional Documents

Culture Documents

J113 Calogic

Uploaded by

rdbassesOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

J113 Calogic

Uploaded by

rdbassesCopyright:

Available Formats

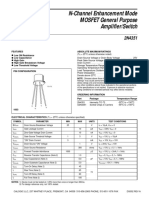

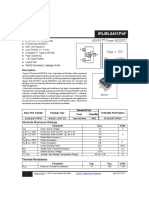

N-Channel JFET Switch

CORPORATION

J111 - J113 / SST111 – SST113

FEATURES APPLICATIONS

• Low Cost • Analog Switches

• Automated Insertion Package • Choppers

• Low Insertion Loss • Commutators

• No Offset or Error Voltage Generated By Closed Switch

-

Purely Resistive ABSOLUTE MAXIMUM RATINGS

(TA = 25oC unless otherwise specified)

-

High Isolation Resistance From Driver

• Fast Switching Gate-Drain or Gate-Source Voltage . . . . . . . . . . . . . . . . -35V

• Short Sample and Hold Aperture Time Gate Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50mA

Storage Temperature Range . . . . . . . . . . . . . -55oC to +150oC

Operating Temperature Range . . . . . . . . . . . -55oC to +135oC

PIN CONFIGURATION Lead Temperature (Soldering, 10sec) . . . . . . . . . . . . . +300oC

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 360mW

SOT-23 Derate above 25oC . . . . . . . . . . . . . . . . . . . . . . 3.3mW/ oC

G NOTE: Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to the device. These are

stress ratings only and functional operation of the device at these or

TO-92 any other conditions above those indicated in the operational sections

of the specifications is not implied. Exposure to absolute maximum

D

rating conditions for extended periods may affect device reliability.

S ORDERING INFORMATION

Part Package Temperature Range

J111-113 Plastic SOT-23 -55ooC to +135ooC

G

PRODUCT MARKING (SOT-23) SST111-113 Plastic SOT-23 -55 C to +135 C

D S

SST111 111 For Sorted Chips in Carriers see 2N4391 series.

5001 SST112 112

SST113 113

ELECTRICAL CHARACTERISTICS (TA = 25oC unless otherwise specified)

111 112 113

SYMBOL PARAMETER UNITS TEST CONDITIONS

MIN TYP MAX MIN TYP MAX MIN TYP MAX

IGSSR Gate Reverse Current (Note 1) -1 -1 -1 nA VDS = 0V, VGS = -15V

VGS(off) Gate Source Cutoff Voltage -3 -10 -1 -5 -0.5 -3 VDS = 5V, ID = 1µA

V

BVGSS Gate Source Breakdown Voltage -35 -35 -35 VDS = 0V, IG = -1µA

IDSS Drain Saturation Current (Note 2) 20 5 2 mA VDS = 15V, VGS = 0V

ID(off) Drain Cutoff Current (Note 1) 1 1 1 nA VDS = 5V, VGS = -10V

rDS(on) Drain Source ON Resistance 30 50 100 Ω VDS = 0.1V, VGS = 0V

Cdg(off) Drain Gate OFF Capacitance 5 5 5 VDS = 0,

VGS = -10V

Csg(off) Source Gate OFF Capacitance 5 5 5 pF (Note 3) f = 1MHz

Cdg(on) Drain Gate Plus Source Gate ON VDS = VGS = 0

28 28 28

+ Csg(on) Capacitance (Note 3)

td(on) Turn On Delay Time 7 7 7 Switching Time Test

tr Rise Time 6 6 6 Conditions (Note 3)

J111 J112 J113

td(off) Turn Off Delay Time 20 20 20 ns

VDD 10V 10V 10V

VGS(off) -12V -7V -5V

tf Fall Time 15 15 15 RL 0.8kΩ 1.6kΩ 3.2kΩ

o

NOTES: 1. Approximately doubles for every 10 C increase in TA.

2. Pulse test duration 300µs; duty cycle ≤3%.

3. For design reference only, not 100% tested.

CALOGIC CORPORATION, 237 Whitney Place, Fremont, California 94539, Telephone: 510-656-2900, FAX: 510-651-1076

You might also like

- Datasheet MOSFETnDocument1 pageDatasheet MOSFETnSebastian GalvisNo ratings yet

- EMOSFET Nchannel 2N4351Document1 pageEMOSFET Nchannel 2N4351Pradina Kiky WasibagnoNo ratings yet

- N-Channel JFET Low Noise Amplifier: CorporationDocument1 pageN-Channel JFET Low Noise Amplifier: CorporationmahaisenNo ratings yet

- Dual N-Channel JFET Switch: This Datasheet Has Been Downloaded From at ThisDocument2 pagesDual N-Channel JFET Switch: This Datasheet Has Been Downloaded From at ThisDanish ShahNo ratings yet

- NTE469 Silicon N-Channel JFET Transistor Spec SheetDocument2 pagesNTE469 Silicon N-Channel JFET Transistor Spec SheetrdbassesNo ratings yet

- IRLR2905Z IRLU2905Z: Automotive MosfetDocument11 pagesIRLR2905Z IRLU2905Z: Automotive MosfetnaughtybigboyNo ratings yet

- Ut3n06g Ab3 R Ut3n06g Ae3 R Ut3n06l Tm3 T Ut3n06g Tm3 T Ut3n06l Tn3 R Ut3n06g Tn3 RDocument4 pagesUt3n06g Ab3 R Ut3n06g Ae3 R Ut3n06l Tm3 T Ut3n06g Tm3 T Ut3n06l Tn3 R Ut3n06g Tn3 RAlberto CruzNo ratings yet

- Unisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetJhonson Shut DownNo ratings yet

- 2N5434Document3 pages2N5434Syed OmairNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedMax RenanNo ratings yet

- MTP50P03HDL Power MOSFET 50 Amps, 30 Volts, Logic LevelDocument8 pagesMTP50P03HDL Power MOSFET 50 Amps, 30 Volts, Logic LevelMohamed ReyadNo ratings yet

- STP11NK50ZDocument13 pagesSTP11NK50ZWilliam OliveiraNo ratings yet

- Ut 9435 Hl. Ic. TV Led Polytron 14Document4 pagesUt 9435 Hl. Ic. TV Led Polytron 14nuwari fadliNo ratings yet

- IRF1405Document9 pagesIRF1405Francisco MadridNo ratings yet

- Unisonic Technologies Co., LTD: 1.2A, 600V N-CHANNEL Power MosfetDocument7 pagesUnisonic Technologies Co., LTD: 1.2A, 600V N-CHANNEL Power MosfetRogerio E. SantoNo ratings yet

- Datasheet 2N5459 PDFDocument1 pageDatasheet 2N5459 PDFKEVIN ADRIAN SEGURA MORCILLONo ratings yet

- IRLR3110ZDocument11 pagesIRLR3110ZОлег ШироносовNo ratings yet

- IRFP054N_PowerMOSFETDocument8 pagesIRFP054N_PowerMOSFETcostelcnNo ratings yet

- Unisonic Technologies Co., LTD: 4.2A, 20V P-CHANNEL Power MosfetDocument4 pagesUnisonic Technologies Co., LTD: 4.2A, 20V P-CHANNEL Power MosfetMelissa Melissa100% (1)

- IRF9Z24NDocument8 pagesIRF9Z24NnoahkrpgNo ratings yet

- MTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Document7 pagesMTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Hectór DavidNo ratings yet

- Rfp30N06Le, Rf1S30N06Lesm: 30A, 60V, Esd Rated, 0.047 Ohm, Logic Level N-Channel Power Mosfets FeaturesDocument8 pagesRfp30N06Le, Rf1S30N06Lesm: 30A, 60V, Esd Rated, 0.047 Ohm, Logic Level N-Channel Power Mosfets Featuresfahmi1987No ratings yet

- IRF6215 DatasheetzDocument9 pagesIRF6215 DatasheetzBoniface AsuvaNo ratings yet

- N-Channel MOSFET with 650V Breakdown and 6.5A Continuous Drain CurrentDocument7 pagesN-Channel MOSFET with 650V Breakdown and 6.5A Continuous Drain Currentjoswil21No ratings yet

- IRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesDocument6 pagesIRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesJaime Enrique ValbuenaNo ratings yet

- Stb35Nf10 Stp35Nf10: N-Channel 100V - 0.030 - 40A - D Pak/To-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument14 pagesStb35Nf10 Stp35Nf10: N-Channel 100V - 0.030 - 40A - D Pak/To-220 Low Gate Charge Stripfet™ Ii Power MosfetRichardNo ratings yet

- IRFZ44N 60V 55A 16.5mo Vth4.0 PDFDocument9 pagesIRFZ44N 60V 55A 16.5mo Vth4.0 PDFVolodiyaNo ratings yet

- Irf2807 International DatasheetDocument8 pagesIrf2807 International DatasheetAdam SchwemleinNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedHorizonte Servicios CarmelitoNo ratings yet

- Irf2807 International DatasheetDocument8 pagesIrf2807 International DatasheetAdam SchwemleinNo ratings yet

- FQB55N10: N-Channel QFET MosfetDocument8 pagesFQB55N10: N-Channel QFET MosfetcurzNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedwilltorNo ratings yet

- N-Channel JFET: J210 - J212 / SSTJ210 - SSTJ212Document2 pagesN-Channel JFET: J210 - J212 / SSTJ210 - SSTJ212Luis Carlos OrtegaNo ratings yet

- Irf 3205Document12 pagesIrf 3205Bristhian LezanoNo ratings yet

- Irfiz 34 NDocument8 pagesIrfiz 34 NBase de DatosNo ratings yet

- Stp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetDocument12 pagesStp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetJavier55No ratings yet

- DatasheetDocument8 pagesDatasheetAndrianarimananaNo ratings yet

- DatasheetDocument12 pagesDatasheetErwin Rolando EscobarNo ratings yet

- Irfr3505Pbf Irfu3505Pbf: FeaturesDocument11 pagesIrfr3505Pbf Irfu3505Pbf: FeaturesAzizullah AlizayNo ratings yet

- J105 / J106 / J107 N-Channel Switch: DescriptionDocument6 pagesJ105 / J106 / J107 N-Channel Switch: Descriptionfarlocco23No ratings yet

- IRFR3910 DatasheetzDocument11 pagesIRFR3910 DatasheetzwilltorNo ratings yet

- IRF9520Document7 pagesIRF9520Emilio QuijanoNo ratings yet

- 6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999Document8 pages6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999rex999No ratings yet

- Irlr3705Zpbf Irlu3705Zpbf: Automotive MosfetDocument11 pagesIrlr3705Zpbf Irlu3705Zpbf: Automotive MosfetMOHAN M ANo ratings yet

- Irfz48npbf PDFDocument8 pagesIrfz48npbf PDFAntony BurgersNo ratings yet

- Unisonic Technologies Co., LTD: 10 Amps, 600/650 Volts N-Channel Power MosfetDocument9 pagesUnisonic Technologies Co., LTD: 10 Amps, 600/650 Volts N-Channel Power MosfetEmmanuel ZambranoNo ratings yet

- Infineon IRFR540Z DataSheet v01 01 EN-3166491Document13 pagesInfineon IRFR540Z DataSheet v01 01 EN-3166491ANo ratings yet

- Unisonic Technologies Co., LTD: 9.4A, 100V P-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 9.4A, 100V P-CHANNEL Power Mosfetboubker2bessaiNo ratings yet

- IRFRU9024NDocument10 pagesIRFRU9024NRuslanNo ratings yet

- Irf 530 NPBFDocument9 pagesIrf 530 NPBFGabiBaciuNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedLiver Haro OrellanesNo ratings yet

- Datasheet PDFDocument8 pagesDatasheet PDFSaad LehlouNo ratings yet

- IRFZ 34N - International RectifierDocument8 pagesIRFZ 34N - International RectifierStevenNo ratings yet

- Irf3710 Datasheet PDFDocument8 pagesIrf3710 Datasheet PDFMiguel Gutierréz CasillasNo ratings yet

- Infineon IRLML6401 DataSheet v01 01 enDocument10 pagesInfineon IRLML6401 DataSheet v01 01 enMohammad kazem DehghaniNo ratings yet

- Hoja de Datos 10n65kDocument6 pagesHoja de Datos 10n65kleamxi777No ratings yet

- F1010NDocument8 pagesF1010Nangel sulvaranNo ratings yet

- CRST045N10N, CRSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedDocument10 pagesCRST045N10N, CRSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedLuis FigueroaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- 12VAC, 500ma Circuit For 12V SLA Battery ChargerDocument5 pages12VAC, 500ma Circuit For 12V SLA Battery ChargerrdbassesNo ratings yet

- Roland KC-300 PreampDocument1 pageRoland KC-300 PreamprdbassesNo ratings yet

- Wharfadale SVP-X Users ManualDocument12 pagesWharfadale SVP-X Users ManualrdbassesNo ratings yet

- SVP-15P NewDocument13 pagesSVP-15P NewAchille100% (1)

- J113 Linear SystemsDocument2 pagesJ113 Linear SystemsrdbassesNo ratings yet

- Viper22A-E Viper22Adip-E, Viper22As-E: Low Power Off-Line Smps Primary SwitcherDocument21 pagesViper22A-E Viper22Adip-E, Viper22As-E: Low Power Off-Line Smps Primary SwitcherAkash KumarNo ratings yet

- Viper 22A-E Circuit 2 PDFDocument17 pagesViper 22A-E Circuit 2 PDFrdbassesNo ratings yet

- Wharfedale SVP 12PMDocument13 pagesWharfedale SVP 12PMrdbasses100% (1)

- Viper 22A-E Circuit 1Document17 pagesViper 22A-E Circuit 1rdbassesNo ratings yet

- El817 1471182106Document14 pagesEl817 1471182106RăzvanNo ratings yet

- J113-Micro Electronics PDFDocument1 pageJ113-Micro Electronics PDFrdbassesNo ratings yet

- D5954Document6 pagesD5954rdbassesNo ratings yet

- How To Read FET DatasheetDocument1 pageHow To Read FET DatasheetNevethNo ratings yet

- J113 PhillipsDocument6 pagesJ113 PhillipsrdbassesNo ratings yet

- Topics On CIrcuit Protection For Power SuppliesDocument11 pagesTopics On CIrcuit Protection For Power SuppliesrdbassesNo ratings yet

- J113 PhillipsDocument6 pagesJ113 PhillipsrdbassesNo ratings yet

- Roland Cube 60Document1 pageRoland Cube 60rdbasses0% (1)

- NNSD 698 SDocument40 pagesNNSD 698 SAnonymous 2GVabYh40W100% (1)

- Wharfdale Pro Brochure 2013Document72 pagesWharfdale Pro Brochure 2013rdbassesNo ratings yet

- 44.fine Tuning Air Conditioning and Refrigeration System - Team Tolly PDFDocument129 pages44.fine Tuning Air Conditioning and Refrigeration System - Team Tolly PDFdexterNo ratings yet

- 5-CH BTL DRIVER FOR DVD PLAYER WITH DISC BIDIRECTIONAL DRIVER AND TWO VARIABLE REGULATORSDocument8 pages5-CH BTL DRIVER FOR DVD PLAYER WITH DISC BIDIRECTIONAL DRIVER AND TWO VARIABLE REGULATORSjose4445No ratings yet

- LA78040B Vertical Deflection Output ICDocument3 pagesLA78040B Vertical Deflection Output ICdragon-red0816No ratings yet

- BIG-IP F5 AFM Operations GuideDocument115 pagesBIG-IP F5 AFM Operations GuidePadam DhamiNo ratings yet

- A Blockchain-Based Self-Tallying Voting Protocol With Maximum Voter PrivacyDocument13 pagesA Blockchain-Based Self-Tallying Voting Protocol With Maximum Voter PrivacyTango CharlieNo ratings yet

- Upload 4 Documents for FreeDocument71 pagesUpload 4 Documents for FreesgdcNo ratings yet

- Automatic Plant Watering System Using Arduino Done EditDocument87 pagesAutomatic Plant Watering System Using Arduino Done EditZylene Janela67% (3)

- Mini Cooper S: User GuideDocument24 pagesMini Cooper S: User GuideGazza TNo ratings yet

- Manual For PD48LM46SP - 1Document148 pagesManual For PD48LM46SP - 1s3ms0No ratings yet

- Baxter - Heraeus Megafuge 1,2 - User ManualDocument13 pagesBaxter - Heraeus Megafuge 1,2 - User ManualMarcos ZanelliNo ratings yet

- Infinity Serviss: Batch Coding MachinesDocument2 pagesInfinity Serviss: Batch Coding MachinesSatyaki SNo ratings yet

- Evolution of Latches and Flip-Flops-1Document24 pagesEvolution of Latches and Flip-Flops-1Ravi ThejaNo ratings yet

- ETL Developer ProfileDocument2 pagesETL Developer ProfileKrishNo ratings yet

- C ProgrammingDocument8 pagesC ProgrammingLigo PastiNo ratings yet

- AACC Cyber Security IA Degree & CertificatesDocument4 pagesAACC Cyber Security IA Degree & CertificatescarrielearyNo ratings yet

- 013740E Echo-Screen III Brochure en USDocument4 pages013740E Echo-Screen III Brochure en USSuhaimi RostiNo ratings yet

- Documentation Haptic TechnologyDocument27 pagesDocumentation Haptic TechnologyLavan saikumar20% (5)

- Home Generator Systems: Wattage WorksheetDocument6 pagesHome Generator Systems: Wattage WorksheetDeborah Rivera NaugleNo ratings yet

- Assignment-1 (Santoshini Satapathy)Document16 pagesAssignment-1 (Santoshini Satapathy)S lalita KumariNo ratings yet

- Circuit breaker testing with micro-logic trip unitDocument16 pagesCircuit breaker testing with micro-logic trip unitgeo_biNo ratings yet

- Effectiveness of Workers Participation in ManagementDocument59 pagesEffectiveness of Workers Participation in ManagementᏒ.Gᴀɴᴇsн ٭ʏт᭄No ratings yet

- PMD - Front Sprint2021-20 ScenariosDocument42 pagesPMD - Front Sprint2021-20 ScenariosHuy Quang PhạmNo ratings yet

- Introduction to Maintenance ManagementDocument13 pagesIntroduction to Maintenance Managementn.tNo ratings yet

- Strategic Mine Planning With COMET SoftwareDocument4 pagesStrategic Mine Planning With COMET SoftwareALfian Bangngabua'No ratings yet

- Bluetooth Dual Mode: Configuration Guide Wednesday, 25 November 2020Document28 pagesBluetooth Dual Mode: Configuration Guide Wednesday, 25 November 2020rNo ratings yet

- Aluminum and Sustainable Building Design: Eddie Bugg PE, LEED APDocument40 pagesAluminum and Sustainable Building Design: Eddie Bugg PE, LEED APVinayak GharayNo ratings yet

- 1mrk509063-Uen en Operatoras Manual Compact Current Relay and Protection Assemblies RXHL 401 and Rahl 401Document22 pages1mrk509063-Uen en Operatoras Manual Compact Current Relay and Protection Assemblies RXHL 401 and Rahl 401Reji KurianNo ratings yet

- Requirements GatheringDocument2 pagesRequirements GatheringNivikesh ramNo ratings yet

- KING LONG Operation Manual XMQ6900JDocument132 pagesKING LONG Operation Manual XMQ6900JWence Clement AgustinNo ratings yet

- Metal Detectors Performance Uxo For98Document17 pagesMetal Detectors Performance Uxo For98A. VillaNo ratings yet

- Trim Chart API 600Document2 pagesTrim Chart API 600Ercan YilmazNo ratings yet

- Diagnostic Trouble Codes: TroubleshootingDocument9 pagesDiagnostic Trouble Codes: TroubleshootingEva AprianaNo ratings yet

- Computer Science PracticalDocument41 pagesComputer Science Practicalsikander.a.khanixd26No ratings yet