Professional Documents

Culture Documents

Autorizacion de Retiro Correo Argentino 190520150606

Uploaded by

Lucas EtchezuriCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Autorizacion de Retiro Correo Argentino 190520150606

Uploaded by

Lucas EtchezuriCopyright:

Available Formats

THC63LVD104C_Rev.2.

1_E

THC63LVD104C

112MHz 30Bits COLOR LVDS Receiver

General Description Features

The THC63LVD104C receiver is designed to support • Wide dot clock range: 8-112MHz suited for NTSC,

pixel data transmission between Host and Flat Panel VGA, SVGA, XGA, and SXGA

Display from NTSC up to SXGA resolutions. The • PLL requires no external components

THC63LVD104C converts the LVDS data streams back • 50% output clock duty cycle

into 35bits of CMOS/TTL data with the choice of the

• TTL clock edge programmable

rising edge or falling edge clock for the convenience

with a variety of LCD panel controllers.At a transmit • Power down mode

clock frequency of 112MHz, 30bits of RGB data and • Low power single 3.3V CMOS design

5bits of timing and control data (HSYNC, • 64pin TQFP

VSYNC,DE,CNTL1,CNTL2) are transmitted at an

• Backward compatible with THC63LVDF64x

effective rate of 784Mbps per LVDS channel.Using a

(18bits) / F84x(24bits)

112MHz clock, the data throughput is 490Mbytes per

second. • Pin compatible with THC63LVD104A

• Fail-safe for Open LVDS Input

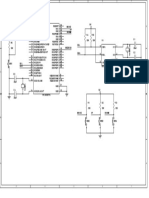

Block Diagram

LVDS INPUT CMOS/TTL OUTPUT

RA+/- 7 RA6-RA0

SERIAL TO PARALLEL

RB+/- 7 RB6-RB0

RC+/- 7 RC6-RC0

RD+/- 7 RD6-RD0

RE+/- 7 RE6-RE0

RCLK+/- PLL CLKOUT

(8 to 112MHz)

CMOS/TTL INPUT

TEST

PD

OE

R/F

Copyright©2010 THine Electronics, Inc. 1/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Pin Out

GND

VCC

VCC

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RB0

RB1

RB2

RB3

RB4

RB5

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

RA- 49 32 RB6

RA+ 50 31 CLKOUT

RB- 51 30 GND

RB+ 52 29 RC0

LVCC 53 28 RC1

RC- 54 27 RC2

RC+ 55 26 RC3

RCLK- 56 25 RC4

RCLK+ 57 24 RC5

LGND 58 23 VCC

RD- 59 22 RC6

RD+ 60 21 RD0

RE- 61 20 RD1

RE+ 62 19 RD2

PGND 63 18 RD3

PVCC 64 17 RD4

10

12

13

14

15

16

11

1

2

3

4

5

6

7

8

9

TEST

GND

GND

VCC

RD6

RD5

RE6

RE5

RE4

RE3

RE2

RE1

RE0

R/F

OE

PD

Copyright©2010 THine Electronics, Inc. 2/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Pin Description

Pin Name Pin # Type Description

RA+, RA- 50, 49 LVDS IN

RB+, RB- 52, 51 LVDS IN

RC+, RC- 55, 54 LVDS IN LVDS Data In.

RD+, RD- 60, 59 LVDS IN

RE+,RE- 62, 61 LVDS IN

RCLK+, RCLK- 57, 56 LVDS IN LVDS Clock In.

RA6 ~ RA0 40,41,42,43,45,46,47 OUT

RB6 ~ RB0 32,33,34,35,36,38,39 OUT

RC6 ~ RC0 22,24,25,26,27,28,29 OUT CMOS/TTL Data Outputs.

RD6 ~ RD0 14,15,17,18,19,20,21 OUT

RE6 ~ RE0 6,7,8,10,11,12,13 OUT

TEST 2 IN Test pin, must be “L” for normal operation.

H: Normal operation,

PD 3 IN

L: Power down (all outputs are “L”)

H: Output enable (Normal operation).

OE 4 IN

L: Output disable(all outputs are Hi-Z)

Output Clock Triggering Edge Select.

R/F 5 IN

H: Rising edge, L: Falling edge

VCC 9,23,37,48 Power Power Supply Pins for TTL outputs and digital circuitry.

CLKOUT 31 OUT Clock out.

GND 1,16,30,44 Ground Ground Pins for TTL outputs and digital circuitry.

LVCC 53 Power Power Supply Pin for LVDS inputs.

LGND 58 Ground Ground Pin for LVDS inputs.

PVCC 64 Power Power Supply Pin for PLL circuitry.

PGND 63 Ground Ground Pin for PLL circuitry.

Data Outputs

PD R/F OE CLKOUT

(Rxn)

0 0 0 Hi-Z Hi-Z

0 0 1 All 0 Fixed Low

0 1 0 Hi-Z Hi-Z

0 1 1 All 0 Fixed Low

1 0 0 Hi-Z Hi-Z

1 0 1 Data Out The falling edge closer to the center of the data eye.

1 1 0 Hi-Z Hi-Z

1 1 1 Data Out The rising edge closer to the center of the data eye.

** Rxn

x = A,B,C,D,E

n = 0,1,2,3,4,5,6

Copyright©2010 THine Electronics, Inc. 3/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Absolute Maximum Ratings 1

Supply Voltage (VCC=VCC=LVCC=PVCC) -0.3V ~ +4.0V

CMOS/TTL Input Voltage -0.3V ~ (VCC + 0.3V)

CMOS/TTL Output Voltage -0.3V ~ (VCC + 0.3V)

LVDS Receiver Input Voltage -0.3V ~ (VCC + 0.3V)

Output Current -30mA ~ 30mA

Junction Temperature +125 °C

Storage Temperature Range -55 °C ~ +150 °C

Reflow Peak Temperature / Time +260 °C / 10sec.

Maximum Power Dissipation @+25 °C 2.1W

Electrical Characteristics

CMOS/TTL DC Specifications

VCC =LVCC=PVCC= 3.0V ~ 3.6V, Ta = -20 °C ~ +85 °C

Symbol Parameter Conditions Min. Typ. Max. Units

VIH High Level Input Voltage 2.0 VCC V

VIL Low Level Input Voltage GND 0.8 V

IOH= -4mA (data)

VOH High Level Output Voltage 2.4 V

IOH= -8mA (clock)

IOL= 4mA (data)

VOL Low Level Output Voltage 0.4 V

IOL= 8mA (clock)

IINC Input Current 0V ≤ V IN ≤ V CC ± 10 μA

LVDS Receiver DC Specifications

VCC =LVCC=PVCC= 3.0V ~ 3.6V, Ta = -20 °C ~ +85 °C

Symbol Parameter Conditions Min. Typ. Max. Units

VTH Differential Input High Threshold VIC= 1.2V 100 mV

VTL Differential Input Low Threshold VIC= 1.2V -100 mV

VIN= 2.4V / 0V

IINL Input Current 30 μA

VCC= 3.6V

1. “Absolute Maximum Ratings” are those values beyond which the safety of the device can not be guaranteed. They

are not meant to imply that the device should be operated at these limits. The tables of “Electrical Characteristics”

specify conditions for device operation.

Copyright©2010 THine Electronics, Inc. 4/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Supply Current

VCC =LVCC=PVCC= 3.0V ~ 3.6V, Ta = -20 °C ~ +85 °C

Symbol Parameter Conditions Typ. Max. Units

fCLKOUT = 75MHz CL=8pF,Vcc=3.6V, 205 mA

Receiver Supply

fCLKOUT = 90MHz Ta= -20 °C ~ 85 °C 236 mA

IRCCW Current

CL=8pF,Vcc=3.6V,

(LVDS Full Toggle) fCLKOUT = 112MHz 280 mA

Ta= -20 °C ~70 °C *

Receiver Power Down

IRCCS PD = L 25 μA

Supply Current

*The trade-off between the output load and the ambient temperature exists so that the junction temperature does not

exceed 125 °C .

LVDS Full Toggle Pattern

CLKOUT

Rx0

Rx1

Rx2

Rx3

Rx4

Rx5

Rx6

x=A,B,C,D,E

Copyright©2010 THine Electronics, Inc. 5/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Output load limitation

The output load is limited so that the junction temperature does not exceed 125 °C .

25.0

20.0

Output Load[pF]

15.0

10.0

5.0 Ta=70℃

Ta=85℃

0.0

8 28 48 68 88 108

Frequency[MHz]

Copyright©2010 THine Electronics, Inc. 6/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Switching Characteristics

VCC =LVCC=PVCC= 3.0V ~ 3.6V, Ta = -20 °C ~+85 °C

Symbol Parameter Min. Typ. Max. Units

tRCP CLKOUT Period 8.92 T 125.0 ns

tRCH CLKOUT High Time T ns

---

2

tRCL CLKOUT Low Time T ns

---

2

tRS TTL Data Setup to CLKOUT 4 ns

--- t RCP – 1

7

tRH TTL Data Hold from CLKOUT 3 ns

--- t RCP – 1

7

tTLH TTL Low to High Transition Time 1.0 3.0 ns

tTHL TTL High to Low Transition Time 1.0 3.0 ns

CLKOUT=50MHz -1000 0 1000 ps

Receiver Skew CLKOUT=75MHz -550 0 550 ps

tSK

Margin CLKOUT=90MHz -400 0 400 ps

CLKOUT=112MHz -250 0 250 ps

tRIP1 Input Data Position0 - tSK 0 + tSK ns

t RCIP t RCIP t RCIP

tRIP0 Input Data Position1 -------------- – t SK -------------

- -------------- + t SK ns

7 7 7

t RCIP t RCIP t RCIP

tRIP6 Input Data Position2 2 -------------

- – t SK 2 -------------

- 2 -------------

- + t SK ns

7 7 7

t RCIP t RCIP t RCIP

tRIP5 Input Data Position3 3 -------------

- – t SK 3 -------------

- 3 -------------

- + t SK ns

7 7 7

t RCIP t RCIP t RCIP

tRIP4 Input Data Position4 4 -------------

- – t SK 4 -------------

- 4 -------------

- + t SK ns

7 7 7

t RCIP t RCIP t RCIP

tRIP3 Input Data Position5 5 -------------

- – t SK 5 -------------

- - + t SK

5 ------------- ns

7 7 7

t RCIP t RCIP t RCIP

tRIP2 Input Data Position6 6 -------------

- – t SK 6 -------------

- - + t SK

6 ------------- ns

7 7 7

tRPLL Phase Lock Loop Set 10.0 ms

RCLK +/- to

tRCD CLKOUT=75MHz 46.5 52.5 ns

CLKOUT Delay

tRCIP CLKIN Period 8.92 125.0 ns

Copyright©2010 THine Electronics, Inc. 7/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

AC Timing Diagrams

TTL Outputs

TTL Output 80% 80%

CL=8pF

20% 20%

TTL Output Load

tTLH tTHL

tRCP tRCH tRCL

R/F = L

CLKOUT VCC/2 VCC/2 VCC/2

R/F = H

tRS tRH

Rxn VCC/2 VCC/2

x = A,B,C,D,E

n = 0,1,2,3,4,5,6

Copyright©2010 THine Electronics, Inc. 8/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E

AC Timing Diagrams

Phase Lock Loop Set Time

3.0V

VCC

RCLK+/-

2.0V

PD

tRPLL

2.0V

CLKOUT

RCLK +/- to CLKOUT Delay Note:

1)Vdiff = (RCLK+) - (RCLK-)

RCLK+ Vdiff=0V

Ry+/-

y = A,B,C,D,E Current Data

tRCD

CLKOUT

VCC/2

R/F = L

Rxn Current Data

x = A,B,C,D,E

n = 0,1,2,3,4,5,6

Copyright©2010 THine Electronics, Inc. 9/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E

AC Timing Diagrams

LVDS Inputs

tRCIP

Vdiff = 0V Vdiff = 0V

RCLK+

(Differential)

RA+/- RA3’ RA2’ RA1’ RA0’ RA6 RA5 RA4 RA3 RA2 RA1 RA0 RA6’’

RB+/- RB3’ RB2’ RB1’ RB0’ RB6 RB5 RB4 RB3 RB2 RB1 RB0 RB6’’

RC+/- RC3’ RC2’ RC1’ RC0’ RC6 RC5 RC4 RC3 RC2 RC1 RC0 RC6’’

RD+/- RD3’ RD2’ RD1’ RD0’ RD6 RD5 RD4 RD3 RD2 RD1 RD0 RD6’’

RE+/- RE3’ RE2’ RE1’ RE0’ RE6 RE5 RE4 RE3 RE2 RE1 RE0 RE6’’

Previous Cycle Current Cycle Next Cycle

tRIP1

tRIP0

tRIP6

tRIP5

tRIP4

tRIP3

tRIP2

Copyright©2010 THine Electronics, Inc. 10/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E THine

Note

1)Power On Sequence

Power on LVDS-Tx after THC63LVD104C.

2)Cable Connection and Disconnection

Don't connect and disconnect the LVDS cable, when the power is supplied to the system.

3)GND Connection

Connect the each GND of the PCB which LVDS-Tx and THC63LVD104C on it. It is better for EMI reduction to place

GND cable as close to LVDS cable as possible.

4)Multi Drop Connection

Multi drop connection is not recommended.

TCLK+

LVDS-Tx THC63LVD104C

TCLK-

THC63LVD104C

5)Asynchronous use

Asynchronous use such as following systems are not recommended.

CLKOUT TCLK+ CLKOUT

DATA LVDS-Tx TCLK- THC63LVD104C DATA

IC IC

CLKOUT TCLK+

LVDS-Tx THC63LVD104C DATA

DATA TCLK-

TCLK+ CLKOUT

TCLK- THC63LVD104C DATA

IC IC

TCLK+

THC63LVD104C DATA

TCLK-

Copyright©2010 THine Electronics, Inc. 11/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E

Package

12.00 BSC.

1.2 Max

10.00 BSC.

1.00+/-0.05

0.05~0.15

12.00 BSC.

10.00 BSC.

THC63LVD104C

0.09~0.20

0.50 BSC. 0.20+/-0.03 0.08 M

3.5+/-3.5 degree

S SEATING PLANE

0.10 S

GAGE PLANE

0.25mm

0.60+/-0.15

1.00 REF.

Unit : mm

Copyright©2010 THine Electronics, Inc. 12/13 THine Electronics, Inc.

THC63LVD104C_Rev.2.1_E

Notices and Requests

1. The product specifications described in this material are subject to change without prior notice.

2. The circuit diagrams described in this material are examples of the application which may not

always apply to the customer's design. We are not responsible for possible errors and omissions

in this material. Please note if errors or omissions should be found in this material, we may not

be able to correct them immediately.

3. This material contains our copy right, know-how or other proprietary. Copying or disclosing to

third parties the contents of this material without our prior permission is prohibited.

4. Note that if infringement of any third party's industrial ownership should occur by using this

product, we will be exempted from the responsibility unless it directly relates to the production

process or functions of the product.

5. This product is presumed to be used for general electric equipment, not for the applications

which require very high reliability (including medical equipment directly concerning people's

life, aerospace equipment, or nuclear control equipment). Also, when using this product for the

equipment concerned with the control and safety of the transportation means, the traffic signal

equipment, or various Types of safety equipment, please do it after applying appropriate

measures to the product.

6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur

with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you

are encouraged to have sufficiently redundant or error preventive design applied to the use of the

product so as not to have our product cause any social or public damage.

7. Please note that this product is not designed to be radiation-proof.

8. Customers are asked, if required, to judge by themselves if this product falls under the category

of strategic goods under the Foreign Exchange and Foreign Trade Control Law.

THine Electronics, Inc.

E-mail: sales@thine.co.jp

Copyright©2010 THine Electronics, Inc. 13/13 THine Electronics, Inc.

You might also like

- THC63LVDM83ADocument9 pagesTHC63LVDM83AHj SoonNo ratings yet

- Thc63lvdf84b Rev.5.11 eDocument15 pagesThc63lvdf84b Rev.5.11 eSsr ShaNo ratings yet

- LVDS 18 Bit COLOR HOST-LCD PANEL INTERFACEDocument9 pagesLVDS 18 Bit COLOR HOST-LCD PANEL INTERFACEAndres Emilio Veloso RamirezNo ratings yet

- X-10 Data-Stream MonitorDocument4 pagesX-10 Data-Stream MonitorGustavo PiaiNo ratings yet

- Pic 16 C 54 CDocument5 pagesPic 16 C 54 Ccuaco_ibm5328No ratings yet

- Timers, Interrupts and LCD ControlDocument11 pagesTimers, Interrupts and LCD ControlTrần Ngọc Thiên DiNo ratings yet

- GE Fanuc CMMDocument6 pagesGE Fanuc CMMmarcosNo ratings yet

- GPSUser ManualDocument15 pagesGPSUser ManualaravindbprasadNo ratings yet

- Appointment Probation Confirmation IDocument33 pagesAppointment Probation Confirmation Igopika vijayanNo ratings yet

- Datasheet PIC16f870Document9 pagesDatasheet PIC16f870Esteban AdrianNo ratings yet

- 256Mb DDR SDRAM Specification SheetDocument40 pages256Mb DDR SDRAM Specification Sheetdata binkusNo ratings yet

- 16F87X Datasheet - Version ResumidaDocument69 pages16F87X Datasheet - Version ResumidamowliwhiteNo ratings yet

- PIC16C773Document202 pagesPIC16C773Luis Oliveira SilvaNo ratings yet

- Datasheet Pic 16 F 871Document172 pagesDatasheet Pic 16 F 871Sound AplicacionNo ratings yet

- Experiment 4: Connecting Input DevicesDocument15 pagesExperiment 4: Connecting Input DevicesTariq MograbiNo ratings yet

- Da DKCNDocument3 pagesDa DKCNTrọng LêNo ratings yet

- 16F877 Data SheetDocument201 pages16F877 Data Sheetjohn11221No ratings yet

- RJ45 To RJ11 2013-1225Document7 pagesRJ45 To RJ11 2013-1225Compu CreditoNo ratings yet

- A-Data ADS6616A4A 1M x 16 Bit x 4 Banks Synchronous DRAMDocument9 pagesA-Data ADS6616A4A 1M x 16 Bit x 4 Banks Synchronous DRAMJim LiebNo ratings yet

- SDNL 1Document1 pageSDNL 1Trọng LêNo ratings yet

- Operation Temperature Condition - 40 85 : Features General DescriptionDocument29 pagesOperation Temperature Condition - 40 85 : Features General DescriptionJuan GutierrezNo ratings yet

- Component Parts ListDocument4 pagesComponent Parts ListVasilis RiderNo ratings yet

- CD74HC4060, CD74HCT4060: High Speed CMOS Logic 14-Stage Binary Counter With OscillatorDocument10 pagesCD74HC4060, CD74HCT4060: High Speed CMOS Logic 14-Stage Binary Counter With OscillatorMuhammad azeemNo ratings yet

- Component Parts ListDocument4 pagesComponent Parts ListskyNo ratings yet

- Linsn Technology: Receiver RV901H SpecificationDocument6 pagesLinsn Technology: Receiver RV901H SpecificationRoberto PasicNo ratings yet

- 41200cmanual MacrochipDocument36 pages41200cmanual MacrochipDarilho Batista Ignacio100% (1)

- PD16732A, 16732B: Mos Integrated CircuitDocument24 pagesPD16732A, 16732B: Mos Integrated CircuitAnika HernandezNo ratings yet

- PIC16F882/883/884/886/887: 28/40/44-Pin Flash-Based, 8-Bit CMOS MicrocontrollersDocument78 pagesPIC16F882/883/884/886/887: 28/40/44-Pin Flash-Based, 8-Bit CMOS Microcontrollersfranklin monteroNo ratings yet

- 64Mb Synchronous DRAM Specification: A3V64S40GTPDocument40 pages64Mb Synchronous DRAM Specification: A3V64S40GTPJeferson AndradeNo ratings yet

- Datasheet - HK Pic16f73 271716 PDFDocument168 pagesDatasheet - HK Pic16f73 271716 PDFAbdul QadirNo ratings yet

- HEF4060BDocument14 pagesHEF4060BVăn Đạt VũNo ratings yet

- RJ45 To RJ11 CablingDocument7 pagesRJ45 To RJ11 CablingAyah Arya100% (1)

- KX-NS300 RJ45 Cabling ConfigurationDocument5 pagesKX-NS300 RJ45 Cabling ConfigurationsmnguyenNo ratings yet

- AK4346Document31 pagesAK4346naeem_aaNo ratings yet

- 3921 Fig 02Document1 page3921 Fig 02Matheus Régis Dias100% (2)

- 74HC HCT4060Document19 pages74HC HCT4060JorgeNo ratings yet

- BAI 1 - Led Don - 7 DoanDocument7 pagesBAI 1 - Led Don - 7 DoanTrần Ngọc Thiên DiNo ratings yet

- DatasheetDocument16 pagesDatasheetStuxnetNo ratings yet

- Hy57v641620hg (16M)Document12 pagesHy57v641620hg (16M)vetchboyNo ratings yet

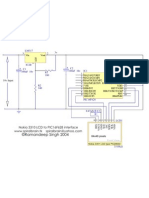

- ProteusDocument12 pagesProteusGuesh Gebrekidan100% (1)

- ©ramandeep Singh 2004: Nokia 3310 LCD To PIC16F628 InterfaceDocument1 page©ramandeep Singh 2004: Nokia 3310 LCD To PIC16F628 InterfaceAnonymous GxeR0L100% (2)

- HY57V561620Document13 pagesHY57V561620Saleem BegNo ratings yet

- 2 (1) M Words X 8 (16) Bits X 4 Banks (64-MBIT) Synchronous Dynamic RamDocument68 pages2 (1) M Words X 8 (16) Bits X 4 Banks (64-MBIT) Synchronous Dynamic RamФат Хыу НгуенNo ratings yet

- MCP453Document102 pagesMCP453priyanka choudhryNo ratings yet

- Interfacing Keypad With PIC 16F877A MicrocontrollerDocument6 pagesInterfacing Keypad With PIC 16F877A MicrocontrollerEysha qureshi100% (1)

- Links v4 circuit components guideDocument2 pagesLinks v4 circuit components guidejbwiltsNo ratings yet

- Description Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICDocument4 pagesDescription Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICSamerNo ratings yet

- Half Bridge Driver With IR2153 IGBT PDFDocument4 pagesHalf Bridge Driver With IR2153 IGBT PDFShibu Kumar SNo ratings yet

- Multiple RS-232 Drivers & Receivers: Product Description FeaturesDocument9 pagesMultiple RS-232 Drivers & Receivers: Product Description Features40818248No ratings yet

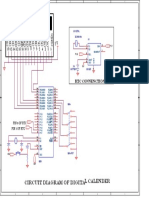

- Digital CalenderDocument1 pageDigital CalenderGarvitt BhatnagarNo ratings yet

- Basic 16f877Document1 pageBasic 16f877api-27535945100% (1)

- MN 66279 RSCDocument97 pagesMN 66279 RSCCarlos AguiarNo ratings yet

- Sdram: M12L2561616A (2S)Document45 pagesSdram: M12L2561616A (2S)api-432313169No ratings yet

- PlaitsDocument3 pagesPlaitsrubixkubeNo ratings yet

- Reb 3571LPX PDFDocument25 pagesReb 3571LPX PDFMuhammad NajibNo ratings yet

- Practical Electronics 1978 01 DrumsDocument6 pagesPractical Electronics 1978 01 DrumsDATrevinoNo ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Chapter 01Document18 pagesChapter 01Parth BhawarNo ratings yet

- Pandora's Box Arcade Stick User ManualDocument21 pagesPandora's Box Arcade Stick User ManualJonardNadelaNo ratings yet

- S01C5021 PDFDocument243 pagesS01C5021 PDFBroken WindowNo ratings yet

- In2114 DatasheetDocument2 pagesIn2114 DatasheetSuep RizalNo ratings yet

- LB91B 47lh50ydDocument66 pagesLB91B 47lh50ydMaiaraFirminoNo ratings yet

- Optiplex 980 Tech GuideDocument51 pagesOptiplex 980 Tech GuidePhosika Sithisane100% (1)

- Project Evaluation and Geotagging SpecsDocument1 pageProject Evaluation and Geotagging SpecsGeovanni DumpasanNo ratings yet

- KTL220S-Xx Service ManualDocument37 pagesKTL220S-Xx Service ManualCamilo Ernesto Rodriguez RodriguezNo ratings yet

- Veilux DVR 960H SeriesDocument71 pagesVeilux DVR 960H SeriesArsenal LontonNo ratings yet

- En c1316 Sarix Ti Ip ps041311Document4 pagesEn c1316 Sarix Ti Ip ps041311Antonio ChipanaNo ratings yet

- Lenovo Ideapad U310 Ultrabook Lenovo Ideapad U410 Ultrabook Lenovo Ideapad U310-8188/8189/8190 Lenovo Ideapad U410 - 1308/1309/1310Document3 pagesLenovo Ideapad U310 Ultrabook Lenovo Ideapad U410 Ultrabook Lenovo Ideapad U310-8188/8189/8190 Lenovo Ideapad U410 - 1308/1309/1310RusydinaNo ratings yet

- Schneider Electronics Service Manual GuideDocument60 pagesSchneider Electronics Service Manual GuideAouadi AbdellazizNo ratings yet

- Viewsonic n3751w-1m vs11405-1m PDFDocument116 pagesViewsonic n3751w-1m vs11405-1m PDFluispe82No ratings yet

- Acer Travelmate 4050Document90 pagesAcer Travelmate 4050joho1945No ratings yet

- STDP93xx 92xx 73xx DatasheetDocument137 pagesSTDP93xx 92xx 73xx Datasheetgrosbill26100% (1)

- M100e 12 Dfu Aen PDFDocument14 pagesM100e 12 Dfu Aen PDFggeorgelNo ratings yet

- E-Ball TechnologyDocument38 pagesE-Ball Technologyjissmathew100% (2)

- Atv Box LCDDocument7 pagesAtv Box LCDashokhaiiiiNo ratings yet

- GM5621, GM5626, GM2621: Dual Input LCD Controller For Entry Level ApplicationsDocument8 pagesGM5621, GM5626, GM2621: Dual Input LCD Controller For Entry Level Applicationsparana12345No ratings yet

- ProDisplay P223Document4 pagesProDisplay P223peterzNo ratings yet

- User Manual: VDH-NKDocument41 pagesUser Manual: VDH-NKMohamed Ibrahim AhamedRasmiNo ratings yet

- KD-208 User ManualDocument17 pagesKD-208 User ManualmazacotesNo ratings yet

- Crestron - Dmc-4k-Co-Hd-Hdcp2Document3 pagesCrestron - Dmc-4k-Co-Hd-Hdcp2Tuấn VũNo ratings yet

- TH-L42E3S: LCD TVDocument84 pagesTH-L42E3S: LCD TVrachmatNo ratings yet

- LCD TV: Service ManualDocument36 pagesLCD TV: Service Manualalvhann_1No ratings yet

- Operator'S Manual: Multi-Purpose LCD DisplayDocument44 pagesOperator'S Manual: Multi-Purpose LCD DisplayMike Omega Global Marine ServicesNo ratings yet

- Led LCD TV: Service ManualDocument48 pagesLed LCD TV: Service Manualku1989No ratings yet

- Ihm Mi4 - Technik - K - GDocument43 pagesIhm Mi4 - Technik - K - GAngelo MuñozNo ratings yet

- SM - LG 43uh603v - Ud65s PDFDocument76 pagesSM - LG 43uh603v - Ud65s PDFJerzy LisowskiNo ratings yet

- Acer C20 20100929 V1 0Document58 pagesAcer C20 20100929 V1 0Sorin BucNo ratings yet