Professional Documents

Culture Documents

Amkor IMAPS TSV Presentation Oct27 2011

Uploaded by

peter_alsiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Amkor IMAPS TSV Presentation Oct27 2011

Uploaded by

peter_alsiCopyright:

Available Formats

Challenges & Opportunities for 3DIC TSV Based Products

Ron Huemoeller SVP, Adv. 3D Platform Develop October 27, 2011

Stacked CSP Migration to TSV

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

R.Huemoeller Oct-11

FCBGA Migration to TSV

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

R.Huemoeller Oct-11

TSV Industry Product Development

Vertical Stacking

Many top tier customers engaged with several years of development completed Today CSP focused on 28nm CMOS scaling to 20/22nm Both wafer finishing and pre-finished wafer process flows being used

Interposer Side by Side Stacking

Many top tier customers engaged with several years of development completed All large package body focused Both wafer finishing and pre-finished wafer process flows being used Logic on Interposer Multiple logic die on single thinned interposer Logic + Memory on Interposer Single logic die + multiple memory stacks on single thinned interposer Other passive components in some cases

2011 Amkor Technology, Inc. Amkor Info. for Controlled Release at AZ IMAPS 4 R.Huemoeller Oct-11

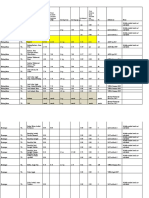

TSV Production Intercepts Amkor View

Si InterpT + DDRT + Logic

GPU, CPU Interposer Required

Apps ProcessorT + DDR

Smart Phone / Tablet

Interposer Required

MEMsT

Mobile Devices

Memory (DDRT)

Server, Wide I/O

Si InterposerT + Logic

ASIC, FPGA

Interp. Reqd

Logic Backside Metal

Power Amp.

Production Since 2010

2011

Die with SV indicated by = T

2011 Amkor Technology, Inc.

2012

2013

2014

2015

All Products planning on 22/20nm in future platforms for TSV

Amkor Info. for Controlled Release at AZ IMAPS 5 R.Huemoeller Oct-11

3DIC TSV Product Opportunities

Logic 1 Traditional SOC Analog Cache Logic 2

Logic 2

Analog

Logic 1

Cache

Logic 1

Monolithic SOC

Logic 1 Logic 2

Logic New !! Logic Logic

Logic

Logic

Multi-Die Interposer SOC

Focus process node development on specific application functionalities Reduces complexity and mask layer count of process node Reduces advanced process node Time to Market Improves wafer yield Reduces wafer start cost Improves performance, power, and area of each application functionality

Amkor Info. for Controlled Release at AZ IMAPS 6 R.Huemoeller Oct-11

2011 Amkor Technology, Inc.

Primary Drivers for Interposers

New Markets Lower Power Memory Bus Speed Stress Reduction in Top Die

R.Huemoeller Oct-11

Si InterpT + DDRT + Logic

Wide Parallel Busses Wide Parallel Busses Gate to Gate Routing between Die Departition

Si InterpT + Logic

Deconstruc t Smaller Die

Fab Yield

Si InterpT + Logic + SERDES

Departition (e-DRAM)

Integrate Heterogeneous Die

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

Silicon Interposer Logistic Challenge

Wafer Finish Can be at either Foundry or OSAT

Business Concerns : Ownership of TSV related failures Cost Agreed to metric for known good Wafer Technical Concerns : BOM Compatibility Same bump metallurgies Same passivation materials Thin wafer handling / shipping

2011 Amkor Technology, Inc. Amkor Info. for Controlled Release at AZ IMAPS 8 R.Huemoeller Oct-11

TSV Product Challenges

Technology Integration

Thermal

Micro Copper Pillar Bumping

Micro Joining

Silico n

Interposer Substrate

Underfill Thin Wafer Handling

TSV Reveal Interposer Thinning

Subassembly & Package Warpage

9 R.Huemoeller Oct-11

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

Wafer Finishing of TSV Devices

TSV Reveal, Isolation and Passivation

Key : No damage to silicon, liner or tip Critical : No copper residue on surface

Grind Expose TSV

Ni Au on Copper Via

Silicon Etch Recess

2011 Amkor Technology, Inc.

Amkor Business Proprietary Amkor Info. for Controlled Release at AZ IMAPS

10

R.Huemoeller Oct-11

Wafer Finishing of TSV Devices, cont.

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

11

R.Huemoeller Oct-11

Top Wafer Finishing Challenge

Thin Wafer Handling

200/300mm Thin Wafer Handling De-bonding De-bonding both 200mm and 300mm wafers with large

C4 bumps on back side of wafer very challenging

Wafer breakage, bump deformation, foreign material all

present challenges

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

12

R.Huemoeller Oct-11

Top TSV Assembly Challenges

Die-Die / Die-Substrate Joining

Micro bump uniformity ; Method of Join ; Materials

Die-Die X-Y Spacing

Fillet sizes and pad metallurgy Process assy sequence ; Micro-join method & Matls

Assembly Process Flexibility is REQUIRED

Thermal & Power Management

Use of Lids, Stiffeners & Passives Underfill/Resin bleed, adhesive compatibility Process assy sequence ; Micro-join method & Matls

Warpage Control

Interposer warpage ; Substrate warpage Top die warpage top die area density/distribution

Die to Die Die to Substrate Die to Wafer

Intermediate e-Test Points

Process assembly sequence

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

13

R.Huemoeller Oct-11

Many Assembly Flows in Use Today

Vertical Stacking Side-Side Stacking

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

14

R.Huemoeller Oct-11

TSV CSP Vertical Assembly

Thermo-Compression Bond + Non Conductive Paste (NCP)

Thin die handling capability to 50m Material dispense critical

Chip

Chip

Pitch 40m today ; 30m 2011 Pillar to Ni-Au Pad as standard Ni 2011 Amkor Technology, Inc.

Cu Pillar with SnAg Bumps 40 40m today

15 R.Huemoeller Oct-11

Amkor Info. for Controlled Release at AZ IMAPS

TSV Silicon Interposer Assembly

Assembly Experience on Interposer

Substrates range from 35mm up to 55mm Interposer thickness as thin as 60um, but typically at100um

GPU DRAM DRAM

Chip

Chip

Pitch 40m today ; 30m 2012

2011 Amkor Technology, Inc.

80m Tall Plated SnAg Bumps Pitch 150m today ; 130m 2012

16 R.Huemoeller Oct-11

Amkor Info. for Controlled Release at AZ IMAPS

TSV Silicon Interposer Reliability

Initial Underfill

MRT, L4

HAST 48 Hours

HAST 264 Hours

Courtesy of Xilinx, TSMC, Amkor

Passed MRT + HAST: 110C, 85% RH, 264 Hours

2011 Amkor Technology, Inc. Amkor Info. for Controlled Release at AZ IMAPS 17 R.Huemoeller Oct-11

TSV Reliability Data General

ASIC (die to die = face to face)

Multiple Die on Interposer ; 100m thick, 10m TSV at 210m pitch Logic at 40m pitch bump with 25m dia. ; over 200k micro-bumps Passed Level 4 MRT ; TC Condition B 1000 cycles ; HTS 1000 hrs

Handset 45nm Baseband (die to die = face to back)

Memory ~ 100m thick Logic ~ 50m thick with 10m TSV at 40um pitch ; either peripheral or area array bump pitch to substrate Passed MRT L3 260C (3x reflow) ; T/C-B 1000 cycles ; HTS 1000 hrs

2011 Amkor Technology, Inc.

Amkor Info. for Controlled Release at AZ IMAPS

18

R.Huemoeller Oct-11

Thank You!

You might also like

- Wafer Level CSP Overview Fillion 2011Document36 pagesWafer Level CSP Overview Fillion 2011Sandra FillionNo ratings yet

- Amkor - Min YooDocument31 pagesAmkor - Min YookbrinaldiNo ratings yet

- Stats eWLB OverviewFlyer PDFDocument4 pagesStats eWLB OverviewFlyer PDFChris TanNo ratings yet

- PDF LokDocument43 pagesPDF LokSaroSureshNo ratings yet

- ELWB Read FirstDocument24 pagesELWB Read FirstChris TanNo ratings yet

- Department of Electrical and Systems Engineering: MOSFET Amplifier Mini ProjectDocument7 pagesDepartment of Electrical and Systems Engineering: MOSFET Amplifier Mini ProjectsadfaNo ratings yet

- SIA 2023 Factbook - 1Document27 pagesSIA 2023 Factbook - 1cfsturmanNo ratings yet

- Osat Sector TaiwanDocument33 pagesOsat Sector Taiwantalleyrand8No ratings yet

- Laser Assisted Transfer of Solder Material From A Solid - State Solder Layer For Mask-Less Formation of Micro Solder Depots On Cu-Pillars and ENIG Pad StructuresDocument8 pagesLaser Assisted Transfer of Solder Material From A Solid - State Solder Layer For Mask-Less Formation of Micro Solder Depots On Cu-Pillars and ENIG Pad StructuresYaodong WangNo ratings yet

- Introduction to SOP TechnologiesDocument46 pagesIntroduction to SOP TechnologiesAhmad UsmanNo ratings yet

- Veggie ListDocument1 pageVeggie ListZach KieferNo ratings yet

- Low Potassium Diet Guide for Kidney PatientsDocument12 pagesLow Potassium Diet Guide for Kidney PatientsHeleneSmithNo ratings yet

- Product Selector GuideDocument36 pagesProduct Selector Guidekarthik4096No ratings yet

- Nutrition ConceptDocument1 pageNutrition ConceptJubilee Jirah ReyesNo ratings yet

- Calculate Total and Soluble Oxalate Levels in Common FoodsDocument269 pagesCalculate Total and Soluble Oxalate Levels in Common FoodsValentin QuinterosNo ratings yet

- Advanced Technologies For Next Generation Integrated CircuitsDocument321 pagesAdvanced Technologies For Next Generation Integrated CircuitsIEC2020034No ratings yet

- Lab Experiment 8Document8 pagesLab Experiment 8Meredith Jensen0% (1)

- SIA Beyond Borders Report FINAL May 6 1Document52 pagesSIA Beyond Borders Report FINAL May 6 1Joey NguyenNo ratings yet

- Nutrition AND Diet Theraphy: Submitted To: Mrs. Lorienel B. EspanolaDocument12 pagesNutrition AND Diet Theraphy: Submitted To: Mrs. Lorienel B. EspanolaBarcelona StarlleteNo ratings yet

- Triangular Patch Antenna 1Document3 pagesTriangular Patch Antenna 1Isha JainNo ratings yet

- Besser Radar Webinar - 2010Document48 pagesBesser Radar Webinar - 2010hafsakhan21No ratings yet

- How to Measure Manager PerformanceDocument25 pagesHow to Measure Manager PerformanceMary Joy CorpuzNo ratings yet

- Biopestcides: Types and Applications: IJAPBC - Vol. 1 (4), Oct-Dec, 2012Document8 pagesBiopestcides: Types and Applications: IJAPBC - Vol. 1 (4), Oct-Dec, 2012Balaji RajendranNo ratings yet

- Challenges of Power Electronic PackagingDocument8 pagesChallenges of Power Electronic Packaging李云龙No ratings yet

- MOSFET Scaling: Dr. Rajan Pandey Associate Professor, SENSEDocument6 pagesMOSFET Scaling: Dr. Rajan Pandey Associate Professor, SENSEVibha M VNo ratings yet

- Comparison of ASIC TechnologyDocument16 pagesComparison of ASIC Technologyasifpatel1234100% (1)

- Yole Equipment Materials For 3DIC Wafer Level Packaging Sample October 2012Document21 pagesYole Equipment Materials For 3DIC Wafer Level Packaging Sample October 2012wirebonderNo ratings yet

- Analog and Digital MEMS Microphone Design Considerations6Document7 pagesAnalog and Digital MEMS Microphone Design Considerations6aragon1974No ratings yet

- 3D IC TechnologyDocument33 pages3D IC TechnologyNikhilAKothariNo ratings yet

- Controlled ImpedanceDocument44 pagesControlled ImpedanceMallappa Patil100% (1)

- Alkaline HydrolysisDocument28 pagesAlkaline Hydrolysissiamak77No ratings yet

- Through Hole Via in PadDocument1 pageThrough Hole Via in PadLina GanNo ratings yet

- ECE448 Lecture15 ASIC DesignDocument17 pagesECE448 Lecture15 ASIC DesignSunil PandeyNo ratings yet

- Power ElectronicsDocument37 pagesPower ElectronicsMohammad Tabrez AlamNo ratings yet

- Semiconductors Top Markets Report PDFDocument63 pagesSemiconductors Top Markets Report PDFMichaela PlatzerNo ratings yet

- SIP Substrates Drive Continued MiniaturizationDocument4 pagesSIP Substrates Drive Continued Miniaturizations1hahriarNo ratings yet

- Proper PCB Layout Techniques Maximize Power Module PerformanceDocument4 pagesProper PCB Layout Techniques Maximize Power Module PerformancesumalaglNo ratings yet

- Design Practices and Strategies For Efficient Signal Integrity ClosureDocument13 pagesDesign Practices and Strategies For Efficient Signal Integrity ClosureSuresh GnanasambanthamNo ratings yet

- What Is Wire BondingDocument27 pagesWhat Is Wire BondingjackNo ratings yet

- Samsung Globalfoundries 14nm Collaboration FinalDocument10 pagesSamsung Globalfoundries 14nm Collaboration FinalTheodoros MaragakisNo ratings yet

- 3D IcDocument37 pages3D IcdevaNo ratings yet

- Semiconductors Next WaveDocument59 pagesSemiconductors Next WaveGary Ryan DonovanNo ratings yet

- Prismark Workshop 092021Document100 pagesPrismark Workshop 092021Gibson leeNo ratings yet

- Performance Comparison of 2D and 3D Torus Network-on-Chip ArchitecturesDocument4 pagesPerformance Comparison of 2D and 3D Torus Network-on-Chip ArchitecturesJournal of ComputingNo ratings yet

- Introduction To National Instruments Wireless Test PlatformDocument47 pagesIntroduction To National Instruments Wireless Test Platformsepe999No ratings yet

- RFCMOSDocument8 pagesRFCMOSSudheer RajaNo ratings yet

- High Speed Serial IntelDocument6 pagesHigh Speed Serial IntelNitu VlsiNo ratings yet

- Global Semiconductor Micro Components Market: Technology, Future Trends, Market Opportunities 2019Document6 pagesGlobal Semiconductor Micro Components Market: Technology, Future Trends, Market Opportunities 2019vinay kumarNo ratings yet

- 8rf Esd GuideDocument148 pages8rf Esd GuidesalmanNo ratings yet

- EMC Design Considerations - ArticleDocument4 pagesEMC Design Considerations - Articlethangaraj_icNo ratings yet

- Assembly of Flexible Circuits With Lead - Free Solder AlloyDocument16 pagesAssembly of Flexible Circuits With Lead - Free Solder AlloyBorad AlpeshNo ratings yet

- Stmicroelectronics Deep Sub-Micron Processes: 0.18Μ, 0.12Μ, 90Nm CmosDocument36 pagesStmicroelectronics Deep Sub-Micron Processes: 0.18Μ, 0.12Μ, 90Nm CmosAbhiNo ratings yet

- Semiconductor RoadmapDocument34 pagesSemiconductor RoadmapGary Ryan DonovanNo ratings yet

- 3CCRX Broadcom JSSCC 16Document14 pages3CCRX Broadcom JSSCC 16Ravi TejaNo ratings yet

- EMC Guidelines PCBDocument13 pagesEMC Guidelines PCBCristian BarrosNo ratings yet

- 15 JFellner MOS-AKDocument18 pages15 JFellner MOS-AKMalagala CharanNo ratings yet

- Amkor Panczak Copper Wirebondingan OSATViewDocument22 pagesAmkor Panczak Copper Wirebondingan OSATViewbalapmuruganNo ratings yet

- Advantages of LCP PackagesDocument6 pagesAdvantages of LCP PackagesTzouralas TheodorosNo ratings yet

- TMN & Nms5ux 002 e GMDocument43 pagesTMN & Nms5ux 002 e GMMuhammad Al FarabiNo ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Project Planning HandbookDocument21 pagesProject Planning HandbookPhilip JonesNo ratings yet

- Anie Altamirano Learning For Life HandoutDocument4 pagesAnie Altamirano Learning For Life HandoutAnnapurna VNo ratings yet

- DMS 48 NormesDocument11 pagesDMS 48 NormesSonia WittmannNo ratings yet

- Example 02 - Moment Capacity of A Concrete Beam - Reinforced Concrete Design ReviewDocument5 pagesExample 02 - Moment Capacity of A Concrete Beam - Reinforced Concrete Design ReviewJohn Michael GeneralNo ratings yet

- 07-02-2023 MS QLNDocument3 pages07-02-2023 MS QLNSummaaaaNo ratings yet

- Active-Passive VoiceDocument18 pagesActive-Passive VoiceDivya JainNo ratings yet

- LTE Interview QuestionsDocument10 pagesLTE Interview QuestionsMahesh Pratap100% (1)

- Gmail LogoDocument12 pagesGmail Logovinodram993480No ratings yet

- A Study To Assess The Effectiveness of PDocument9 pagesA Study To Assess The Effectiveness of PKamal JindalNo ratings yet

- Adiabatic Production of Acetic AnhydrideDocument7 pagesAdiabatic Production of Acetic AnhydrideSunilParjapatiNo ratings yet

- Galvanized and Black Malleable Iron Pipe Fittings SpecificationsDocument24 pagesGalvanized and Black Malleable Iron Pipe Fittings SpecificationsdeniNo ratings yet

- Query Operation 2021Document35 pagesQuery Operation 2021Abdo AbaborNo ratings yet

- Lead Funnels On Funnel Swipe File - TrelloDocument5 pagesLead Funnels On Funnel Swipe File - TrelloKatherie BriersNo ratings yet

- Mineral Processing Course: ThickeningDocument50 pagesMineral Processing Course: ThickeningAdham Elbrawy100% (1)

- Application-Form MRP-INFORMCC 2021 VFFDocument5 pagesApplication-Form MRP-INFORMCC 2021 VFFBouramaNo ratings yet

- Vehicle Tracker Offer SheetDocument1 pageVehicle Tracker Offer SheetBihun PandaNo ratings yet

- Computer Vision: Chapter 5. SegmentationDocument16 pagesComputer Vision: Chapter 5. SegmentationThịi ÁnhhNo ratings yet

- PC 5400 PC 5500Document53 pagesPC 5400 PC 5500ArturHeiseNo ratings yet

- Keynote Proficient End-Of-Course Test BDocument7 pagesKeynote Proficient End-Of-Course Test Bana maria csalinasNo ratings yet

- Texas Final LeadsDocument36 pagesTexas Final Leadsabdullahmohammed4460No ratings yet

- Risk and Risk ManagementDocument8 pagesRisk and Risk ManagementMARY JUSTINE PAQUIBOTNo ratings yet

- Influence of Social Studies Education On Ethnic and Religious Tolerance Among National Certificate of Education Students in Kaduna State.Document104 pagesInfluence of Social Studies Education On Ethnic and Religious Tolerance Among National Certificate of Education Students in Kaduna State.Tsauri Sule SalehNo ratings yet

- 8.9 Basic Maths For Well PlanningDocument9 pages8.9 Basic Maths For Well PlanningKhanh Pham MinhNo ratings yet

- Techniques-Of-Attitude-Scale-Construction FullDocument344 pagesTechniques-Of-Attitude-Scale-Construction FullLuthfi fharuq Al Fairuz67% (3)

- The Advantages and Disadvantages If Block ChainDocument7 pagesThe Advantages and Disadvantages If Block ChainKarthik ShettyNo ratings yet

- 182 - GE8076, GE6075 Professional Ethics in Engineering - 2 MarksDocument17 pages182 - GE8076, GE6075 Professional Ethics in Engineering - 2 Markssharon sylvia .sNo ratings yet

- CBL Training ReportDocument12 pagesCBL Training ReportSwapnil Modak100% (1)

- Writing Emails Part 1 Informal British English Teacher Ver2Document7 pagesWriting Emails Part 1 Informal British English Teacher Ver2Madalina MandiucNo ratings yet

- Carbon SteelDocument1 pageCarbon SteeldexterNo ratings yet

- The Chair As Health Hazard Part II J of PDFDocument11 pagesThe Chair As Health Hazard Part II J of PDFPablo BuniakNo ratings yet