Professional Documents

Culture Documents

Micro Architecture Lab - Execise 1: Amir Saka 060136322 Oded Friedmann 043144799

Uploaded by

Oded FriedmannOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

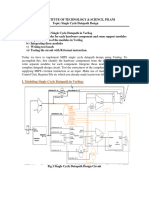

Micro Architecture Lab - Execise 1: Amir Saka 060136322 Oded Friedmann 043144799

Uploaded by

Oded FriedmannCopyright:

Available Formats

Amir Saka 060136322 Oded Friedmann 043144799

Micro Architecture Lab Execise 1

Part A 1. ok 2. This is a tool that simulates the behavior of a computing device. We use it for the following reasons: a. It allows us to test and examine device's ability in the design stage, before actual implementation on HW. b. Different designs can be tested before actual implementation on HW, and allow us to choose the best design c. Gives us the option to test larger variety of scenarios and configurations until we get an optimal result d. level of abstraction can be throttled to design task 3. Types of architectural simulators: a. Functional simulators There are trace driven simulators Vs. Exec driven simulators. b. Performance simulators Instructions schedulers Vs. Cycle Timers. Simple scalar simulator is Exec driven and Cycle Timer. 4. The simple scalar tool set includes compilers, assembler, linker and simulators. It also has the ability to get Assembly code directly. 5. The Simpler scalar simulation suite includes: Type Sim-Fast Sim-Safe Sim-Profile SimCache/Cheetah Sim-Outorder Functional/Performance Functional Functional Functional Functional Performance No of lines 420 350 900 1000> 3900 Other MIPS +4 W/ checks Lots of stats Cache stats OoO issue branch pred, mis spec, ALU, cache, TLB, 200+ KIPS

6. SPEC2000 benchmark suite: A set of benchmarks for standard CPU (and memory) performance measuring and evaluation. There are two main parts: CINT2000 set of Integer programs. CFP2000 set of Floating-point programs. 7. ok 8. ok attached file: q8.txt 9. attached files are: cache32.simout, cache64.simout We changed the size of the cache and ran it once with 32kb and once with 64kb. Miss rate in the first time (32kb) was: 0.0903 Miss rate in the second run (64kb) was: 0.0335

10. the command we used was: cut cache.simout |grep I sim_num_insn > parsing_example.txt Part B 11. Out-Of-Order (OOO) speculative execution is a term that refers to a CPU that executes instructions, not necessarily in their order of appearance bu commits them in order. This is possible by performing the actual calculations without writing the results to the memory. Speculative Execution when branch instruction is executed, the CPU is allowed to predict if the branch will be taken or not taken (there are different methods for predications) and continue execution according to the prediction. If it turns out to be wrong, it is able to restore the status before the prediction. 12. Sim-Outorder Simulator: Performance simulator, which implements OoO processor, including two memory levels and speculative execution. Simulator options (3 chosen): - -issue:inorder determine if processor issues instructions inorder. - -max:inst maximum instructions to execute. - -ptrace <file_name> x:y enable pipeline trace of execution range. 13. Architecture pipeline: Fetch Deco Exe Mem WB

Fetch reads instruction from memory, stores it in PC and advance PC by 4. Includes ALU, register and MUX. Decode reads data from registers, determines instruction type. Includes Registers and sign extension unit. Execute execute ALU commands or memory address calculation. Includes 2 MUX and ALU. MEM reads/writes from/to memory. WB writes ALU result to result register.

14. The output of the command was many blocks such as the following one: First is the cycle number: @ 3974 Then a list of the instructions that were fetched: dn = `0x120028af0: [internal ld/st]' do = `0x120028af4: [internal ld/st]' dp = `0x120028af8: [internal ld/st]' dq = `0x120028b00: stq r17,56(r16)' dr = `0x120028b04: stq r17,40(r16)' ds = `0x120028b08: stq r17,48(r16)' And then the state of the pipeline: [IF] [DA] [EX] [WB] [CT] dm cz dd ct cr* dq dc cx cs* dr df cy cv* ds dg da cw* dh db di de dj dk dl dn do dp Attached are the output.trc and q14.txt files. 15. We ran the following commands: Without config: /local/arch_lab/Simple_Scalar/simplesim-3.0/sim-outorder -max:inst 8000000 /local/arch_lab/spec2000binaries/ sixtrack.peak.ev6 With config: /local/arch_lab/Simple_Scalar/simplesim-3.0/sim-outorder -config /local/arch_lab/Simple_Scalar/simplesim-3.0/config/outorder_2.cfg /local/arch_lab/spec2000binaries/ sixtrack.peak.ev6 There was a problem with the config file that generated an error in the run. The IPC on the first run was: 1.7666 Files attached: q15_no_config.txt , q15_config.txt 16. Again we ran without config file. In the second run we added the -issue:inorder tag. The IPC in the outorder run was: 1.7666 The IPC in the inorder run was: 0.8856 As we expect, executing commands out of order is much better than in order execution. Attached are the files: q16_inorder.txt, q16_outorder.txt

17. Parameter

We changed the script to run bzip2 & eon and got the following results: bzip2 25000002 25939609 2.6890 0.7385 0.0000 0.9975 9975 0.0000 0.0008 0.3793 eon 25000003 33144231 1.9206 0.1061 0.0000 0.9371 0.9714 0.0000 0.0005 0.1551

sim_num_insn sim_total_insn sim_IPC ruu_full lsq_full bpred_comb.bpred_addr_rate bpred_comb.bpred_dir_rate il1.miss_rate dl1.miss_rate ul2.miss_rate

18. FP: mesa 3 dimension graphic program in C, which converts 2-D scalar field data to 2-D PNG (Portable Networks Graphics) image. INT: twolf C program that finds parameters needed for microchip design. Uses heuristic methods to find the best solution according to specific design rules. Outputs the location and layout of all pins. vpr C program for integrated circuit design. The program get as an input file describing the netlist and outputs files containing the best FPGA design it could find + statistics and validity checks results of this design.

You might also like

- Chapter Four 4. The Control UnitDocument9 pagesChapter Four 4. The Control UnitTamene TekileNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Getting Started With Nuvoton NUC140 32-Bit ARM Cortex-M0 Microcontroller PDFDocument7 pagesGetting Started With Nuvoton NUC140 32-Bit ARM Cortex-M0 Microcontroller PDFoktaNo ratings yet

- uCOS-II IntroDocument49 pagesuCOS-II IntroREVATHY RATHEESHNo ratings yet

- CPU Control: Hardwired vs MicroprogrammedDocument13 pagesCPU Control: Hardwired vs MicroprogrammedVaibhav SharmaNo ratings yet

- Hands On Platform Assignment 2Document4 pagesHands On Platform Assignment 2Dylan LerNo ratings yet

- HOMEWORK 3: COMPUTER SYSTEM ARCHITECTUREDocument7 pagesHOMEWORK 3: COMPUTER SYSTEM ARCHITECTUREBajrang KumarNo ratings yet

- Computer System Architecture MCA - 301Document10 pagesComputer System Architecture MCA - 301Mangesh MalvankarNo ratings yet

- Jaimin-Boot Time Optimization in Embedded Linux PDFDocument23 pagesJaimin-Boot Time Optimization in Embedded Linux PDFjaimin23100% (1)

- Sap ComputerDocument6 pagesSap ComputerAyaz AhmadNo ratings yet

- CPU Design PDFDocument53 pagesCPU Design PDFAamir AltafNo ratings yet

- CEA Lab ReportDocument8 pagesCEA Lab ReportIbrahim MehmoodNo ratings yet

- 3 RdunitcsoDocument38 pages3 RdunitcsoGourav DubeyNo ratings yet

- Co-2 - CoaDocument46 pagesCo-2 - CoaDAVU REVANTH NAGNo ratings yet

- Chapter 3Document26 pagesChapter 3عبدالآله الشريفNo ratings yet

- Project 4Document6 pagesProject 4Trai TranNo ratings yet

- EMBEDDED SYSTEM ASSIGNMENT ON PROCESSORS AND COMMUNICATIONDocument30 pagesEMBEDDED SYSTEM ASSIGNMENT ON PROCESSORS AND COMMUNICATIONajas777BNo ratings yet

- Cpusim Hand Book by ManishDocument25 pagesCpusim Hand Book by ManishDinesh YadavNo ratings yet

- Lab Sheet 6 Single Cycle Datapath FinalDocument3 pagesLab Sheet 6 Single Cycle Datapath FinalSANJEEV MALLICKNo ratings yet

- 32 Bit Risc ProcessorDocument60 pages32 Bit Risc ProcessorMuruganantham MuthusamyNo ratings yet

- Ucos II IntroDocument49 pagesUcos II IntroprincegirishNo ratings yet

- Benchmarking CPU Micro-Architecture FeaturesDocument5 pagesBenchmarking CPU Micro-Architecture FeaturesVarad DeshmukhNo ratings yet

- Programming For Problem SolvingDocument95 pagesProgramming For Problem Solvingseemakujur3377No ratings yet

- Cpusim Hand Book by ManishDocument29 pagesCpusim Hand Book by Manishjaikaranprasad527No ratings yet

- Lab4 Testing DFTDocument6 pagesLab4 Testing DFTDeepuNo ratings yet

- Continuation 4TH Unit DpacoDocument18 pagesContinuation 4TH Unit DpacoSANJAY KASI VISVANATHANNo ratings yet

- Module 3 NotesDocument10 pagesModule 3 NotesAmal MonichanNo ratings yet

- MicrocomputerDocument26 pagesMicrocomputerChandan Mishra100% (1)

- Lab 5Document5 pagesLab 5AliBaranIşıkNo ratings yet

- Cse IV Computer Organization (10cs46) SolutionDocument62 pagesCse IV Computer Organization (10cs46) Solutionnbpr0% (1)

- Exp 2Document10 pagesExp 2NAFISA ISLAM 1808006No ratings yet

- Beyond RISC - The Post-RISC Architecture Submitted To: IEEE Micro 3/96Document20 pagesBeyond RISC - The Post-RISC Architecture Submitted To: IEEE Micro 3/96Andreas DelisNo ratings yet

- Control Unit Operation: Roselle Manalang Manuel Vincent Galdo Ron CastroDocument10 pagesControl Unit Operation: Roselle Manalang Manuel Vincent Galdo Ron CastroVincent GaldoNo ratings yet

- MCU Basic Structure/Operation: MCU: The Brain That Controls The HardwareDocument18 pagesMCU Basic Structure/Operation: MCU: The Brain That Controls The HardwareTiniNo ratings yet

- Hpux Performance Troubleshooting Class CPU BottlenecksDocument57 pagesHpux Performance Troubleshooting Class CPU Bottlenecksaibot aibotNo ratings yet

- Assinmet&Case StudyDocument19 pagesAssinmet&Case Studysantosh vighneshwar hegdeNo ratings yet

- Realtime Applications With RTAI: R.KOCIK - Embedded Systems DepartmentDocument69 pagesRealtime Applications With RTAI: R.KOCIK - Embedded Systems DepartmentsatyanaryanakNo ratings yet

- DSP Lab 5 HandoutDocument14 pagesDSP Lab 5 Handoutusama anwerNo ratings yet

- 3.2 Computer Function: Reads (Fetches) InstructionsDocument20 pages3.2 Computer Function: Reads (Fetches) InstructionsElaph AhmedNo ratings yet

- Microprogrammed Control UnitDocument14 pagesMicroprogrammed Control UnitShazib Shabir100% (1)

- EMBEDDED SYSTEM-unit-1Document119 pagesEMBEDDED SYSTEM-unit-112 EE234 Santhosh kumar sNo ratings yet

- Debugging: Log Level DescriptionDocument5 pagesDebugging: Log Level DescriptionavadcsNo ratings yet

- SimpleScalar GuideDocument4 pagesSimpleScalar GuideSaurabh ChaubeyNo ratings yet

- 16-Bit RISC PROCESSORDocument16 pages16-Bit RISC PROCESSORCroitoru Adrian100% (1)

- Component 2Document2 pagesComponent 2karmaNo ratings yet

- Analyzing Kernel Crash On Red HatDocument9 pagesAnalyzing Kernel Crash On Red Hatalexms10No ratings yet

- Co Notes Module 1Document42 pagesCo Notes Module 1Vinyas M SNo ratings yet

- Experiment 3Document56 pagesExperiment 3Ayusha JagtapNo ratings yet

- Assignment: - 4Document7 pagesAssignment: - 4nikita_gupta3No ratings yet

- Serial Device Driver ProjectDocument4 pagesSerial Device Driver ProjectTiagaNo ratings yet

- lab1_specDocument6 pageslab1_spec星期三的配音是對的No ratings yet

- Department of Computer Science and EngineeringDocument32 pagesDepartment of Computer Science and Engineeringjexehif3730% (1)

- Final Project Report: For Advanced Microprocessor DesignDocument13 pagesFinal Project Report: For Advanced Microprocessor DesignAHMED AlrbeaaiNo ratings yet

- Chapter 6-Computer ArchitectureDocument34 pagesChapter 6-Computer ArchitectureVongai MubaiwaNo ratings yet

- Project Report: ON Traffic Light Control SystemDocument53 pagesProject Report: ON Traffic Light Control SystemRajinder BhullarNo ratings yet

- MCRP Viva QuestionDocument12 pagesMCRP Viva QuestionPeter ParkerNo ratings yet

- Synopsys ASIC Design Flow TutorialDocument18 pagesSynopsys ASIC Design Flow TutorialNishant Singh100% (1)

- Top Level View of Computer Function and InterconnectionDocument38 pagesTop Level View of Computer Function and Interconnectionhsi3No ratings yet

- Computer Organization and Architecture Cs2253: Part-ADocument21 pagesComputer Organization and Architecture Cs2253: Part-AjanukarthiNo ratings yet

- Red Hat Enterprise Linux 7 Networking Guide FR FRDocument233 pagesRed Hat Enterprise Linux 7 Networking Guide FR FRndarndarNo ratings yet

- FreeBSD Performance ReviewDocument2 pagesFreeBSD Performance ReviewYaelNo ratings yet

- Audalarm CcvparmsDocument983 pagesAudalarm CcvparmsAleksandr BashmakovNo ratings yet

- Rajasthan Technical University, Kota Teaching & Scheme of Examination For B.Tech. (Computer Engineering)Document4 pagesRajasthan Technical University, Kota Teaching & Scheme of Examination For B.Tech. (Computer Engineering)MUKESHNo ratings yet

- Install Safebridge Training Client GuideDocument5 pagesInstall Safebridge Training Client GuidePrashant SinghNo ratings yet

- DSP Project ProposalDocument6 pagesDSP Project ProposalMohsin IqbalNo ratings yet

- LANGuard 9 - ManualDocument164 pagesLANGuard 9 - ManualAccess CommunicationsNo ratings yet

- BaiOMC - v10.2 Data Sheet-01Document6 pagesBaiOMC - v10.2 Data Sheet-01aungnyinyitunNo ratings yet

- 5GLab DescDocument1 page5GLab DescNaved AlamNo ratings yet

- Online Car Price Prediction System Functional RequirementsDocument8 pagesOnline Car Price Prediction System Functional RequirementsABDUL HADI KHANNo ratings yet

- CS110T Lab02 PDFDocument6 pagesCS110T Lab02 PDFmNo ratings yet

- The Future of Control Room DesignDocument11 pagesThe Future of Control Room DesignS.KAMBANNo ratings yet

- Psts v111 Student Us WMKDocument198 pagesPsts v111 Student Us WMKGopi VenkatesanNo ratings yet

- Disk PartitionsDocument3 pagesDisk PartitionsFernαndα Mαriα dα SilvαNo ratings yet

- Xenius™ 4 EnergyDocument7 pagesXenius™ 4 Energymakmohit6037No ratings yet

- Guía de Actividades y Rúbrica de Evaluación - Tarea 1 - El Concepto de IntegralDocument46 pagesGuía de Actividades y Rúbrica de Evaluación - Tarea 1 - El Concepto de IntegralDany Fernando RodriguezNo ratings yet

- Chapter 2Document60 pagesChapter 2Ravi Parmar043No ratings yet

- Bradburn Et Al v. North Central Regional Library District - Document No. 41Document25 pagesBradburn Et Al v. North Central Regional Library District - Document No. 41Justia.comNo ratings yet

- NPC Order - Cathay PacificDocument4 pagesNPC Order - Cathay PacificRapplerNo ratings yet

- SAP Strategy Management Deliver On Corporate Strategy With Enterprise-Wide Alignment PDFDocument30 pagesSAP Strategy Management Deliver On Corporate Strategy With Enterprise-Wide Alignment PDFsteghibelliniNo ratings yet

- Smart Waste Management SystemDocument42 pagesSmart Waste Management SystemUsama NawazNo ratings yet

- Cspro Capi Getting StartedDocument16 pagesCspro Capi Getting StartedSADOUN SeNo ratings yet

- How To Make A KVCDDocument4 pagesHow To Make A KVCDJagmohan JagguNo ratings yet

- Sc1000 Manual Fiber Laser CuterDocument53 pagesSc1000 Manual Fiber Laser CuterLuis Jose Hernandez BriceñoNo ratings yet

- Qaffl StudioDocument4 pagesQaffl StudiodradetoxNo ratings yet

- CSE 4027 - Mobile Application DevelopmentDocument164 pagesCSE 4027 - Mobile Application Developmentnaman1709No ratings yet

- Configure SSL MasterthebossDocument12 pagesConfigure SSL MasterthebossRobert PhoNo ratings yet

- Blackboard Learn 9.1 Installation Guide PDFDocument133 pagesBlackboard Learn 9.1 Installation Guide PDFhasjudasNo ratings yet

- BPMN Poster A4 Ver 1.0.10 PDFDocument1 pageBPMN Poster A4 Ver 1.0.10 PDFSatrio N. W. NotoamidjojoNo ratings yet

- Unit 7 (C++) - StructuresDocument44 pagesUnit 7 (C++) - StructuresabdiNo ratings yet