Professional Documents

Culture Documents

6.1 Basic Interface

Uploaded by

Ammar IshaquiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

6.1 Basic Interface

Uploaded by

Ammar IshaquiCopyright:

Available Formats

Interface

8088 I/F with basic IO, RAM and 8255

Topics

Timing diagram

Address Bus, R/W, Data Memory Map I/O

Address Decoding

CPU is addressable lager than devices.

Chip Supports

TTL : De-multiplexer, Latch, Buffer

Timing Diagram : Read Cycle

Timing Diagram : Write Cycle

BUS Buffering and Latching

Basic Architecture

Dr.Jim Plusquellic, University of Maryland, Baltimore County http://www.csee.umbc.edu/~plusquel/310/

Bus Architecture

Address:

If I/O, a value between 0000H and FFFFH is issued. If memory, it depends on the architecture:

20 24 25 32 36

-bits -bits -bits -bits -bits

(8086/8088) (80286/80386SX) (80386SL/SLC/EX) (80386DX/80486/Pentium) (Pentium Pro/II/III)

Bus Architecture

Data:

8 -bits (8088) 16 -bits (8086/80286/80386SX/SL/SLC/EX) 32 -bits (80386DX/80486/Pentium) 64 -bits (Pentium/Pro/II/III)

Control:

Most systems have at least 4 control bus connections (active low). MRDC (Memory ReaD Control), MWRC , IORC (I/O Read Control), IOWC

Bus Standards

ISA (Industry Standard Architecture): 8 MHz

8-bit (8086/8088) 16-bit (80286-Pentium)

EISA : 8 MHz

32-bit (older 386 and 486 machines).

PCI (Peripheral Component Interconnect):

33 MHz 32-bit or 64-bit (Pentiums)

VESA (Video Electronic Standards Association):

32-bit or 64-bit (Pentiums), Runs at processor speed. Only disk and video. Competes with the PCI but is not popular.

Bus Standards

USB (Universal Serial Bus):

12 Mbps / 480 Mbps, Serial connection to microprocessor. For keyboards, the mouse, modems and sound cards. To reduce system cost through fewer wires.

IEEE 1394

400 Mbps, primary target is audio/visual consumer electronic devices

AGP (Advanced Graphics Port): 66MHz

64-bits for 533MB/sec, Fast parallel connection, video cards. To accommodate the new DVD (Digital Versatile Disk) players.

Memory : Blank Layout

Memory : Blank Layout

Memory : Blank Layout

Basic I/O Architecture

Interrupt Vector : DOS PC

IO Space

Basic I/O Interface : Input

Basic I/O Interface : Output

I/O Port Decoding

MEMORY

Memory Types

Two basic types:

ROM: Read-only memory RAM: Read-Write memory

Four commonly used memories:

ROM Flash (EEPROM) Static RAM (SRAM) Dynamic RAM (DRAM)

Memory Chips

The data pins are typically bi-directional in read-write memories.

The number of data pins is related to the size of the memory location. For example, an 8-bit wide (byte-wide) memory device has 8 data pins.

Each memory device has at least one chip select (CS) or chip enable (CE) or select (S) pin that enables the memory device.

This enables read and/or write operations. If more than one are present, then all must be 0 in order to perform a read or write.

SRAM vs. DRAM

SRAMs

SRAMs used for caches have access times as low as 10ns .

DRAMs

SRAMs are limited in size (up to about 128Kb). DRAMs are available in much larger sizes, e.g., 64M X 1. DRAMs MUST be refreshed every 2 to 4 ms Since they store their value on an integrated capacitor that loses charge over time.

Memory Address Decoding

Memory Address Decoding

The processor can usually address a memory space that is much larger than the memory space covered by an individual memory chip. In order to splice a memory device into the address space of the processor, decoding is necessary. For example, the 8088 issues 20-bit addresses for a total of 1MB of memory address space.

Ex. Memory Address Decoding

The BIOS on a 2716 EPROM has only 2KB of memory and 11 address pins. A decoder can be used to decode the additional 9 address pins and allow the EPROM to be placed in any 2KB section of the 1MB address space.

Ex. Memory Address Decoding

To determine the address range that a device is mapped into:

Ex. Memory Address Decoding

This 2KB memory segment maps into the reset location of the 8086/8088 (FFFF0H). NAND gate decoders are not often used. Rather the 3-to-8 Line Decoder (74LS138) is more common.

3-to-8 Line Decoder

G2A, G2B, and G1 must be active. Each output of the decoder can be attached to an 2764 EPROM ( 8K X 8 ).

EPROM 2764 x 8

More on Address Decoding

Yet a third possibility is a PLD (Programmable Logic Device).

PLDs come in three varieties: PLA (Programmable Logic Array) PAL (Programmable Array Logic) GAL (Gated Array Logic)

A PAL example (16L8) is commonly used to decode the memory address, particularly for 32-bit addresses generated by the 80386DX and above.

PLD as address decoder

AMD 16L8 PAL decoder. It has 10 fixed inputs (Pins 1-9, 11), two fixed outputs (Pins 12 and 19) and 6 pins that can be either (Pins 13-18).

8088 Memory Interface

The memory systems "sees" the 8088 as a device with:

20 address connections (A19 to A0). 8 data bus connections (AD7 to AD0). 3 control signals, IO/M, RD, and WR.

Interfacing the 8088 with:

32K of EPROM (at addresses F8000H-FFFFFH). 512K of SRAM (at addresses 00000H-7FFFFH).

8088 Memory Interface: EPROM

8088 Memory Interface: EPROM

The EPROM will also require the generation of a wait state.

The EPROM has an access time of 450ns . The 74LS138 requires 12ns to decode.

The 8088 runs at 5MHz and only allows 460ns for memory to access data. A wait state adds 200ns of additional time

8088 Memory Interface: RAM

8088 Memory Interface: RAM

The 62256s on the previous slide are actually SRAMs. Access times are on order of 10ns . Flash memory can also be interfaced to the 8088. However, the write time ( 400ms !) is too slow to be used as RAM.

8088 I/F with Programmable Peripheral Interface 8255

Part I

PPI : 82C55

The 82C55 is a popular interfacing component, that can interface any TTL-compatible I/O device to the microprocessor. It is used to interface to the keyboard and a parallel printer port in PCs (usually as part of an integrated chipset). Requires insertion of wait states if used with a microprocessor using higher that an 8 MHz clock. PPI has 24 pins for I/O that are programmable in groups of 12 pins and has three distinct modes of operation. In the PC, an 82C55 or its equivalent is decoded at I/O ports 60H-63H.

8255 Block Diagram

Pin layout of 8255

Interfacing 8255 PPI

Thats all

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- WinCC V5 Manual Part 1 - 2Document468 pagesWinCC V5 Manual Part 1 - 2www.otomasyonegitimi.comNo ratings yet

- WinCC Int Course FinalDocument1 pageWinCC Int Course FinalAmmar IshaquiNo ratings yet

- Scad A 1Document76 pagesScad A 1ravindarsinghNo ratings yet

- Sub-Station Automation Usin ScadaDocument4 pagesSub-Station Automation Usin Scadamksnsvpr123No ratings yet

- Win CCDocument52 pagesWin CCAmmar IshaquiNo ratings yet

- Profibus CommunicationDocument7 pagesProfibus CommunicationBhayata100% (2)

- Implementation of Control Unit Using SCADA System For Filling Systemv46-13Document5 pagesImplementation of Control Unit Using SCADA System For Filling Systemv46-13Krishna ReddyNo ratings yet

- WinCC Fuel Mangement SoftwareDocument1 pageWinCC Fuel Mangement SoftwareAmmar IshaquiNo ratings yet

- WinCC DataMonitor V6.2Document7 pagesWinCC DataMonitor V6.2Ammar IshaquiNo ratings yet

- Users Manual WinCC Flexible en-USDocument454 pagesUsers Manual WinCC Flexible en-USMavi GüneyEylülNo ratings yet

- 0 1 2 3 4 5 6 Simatic Hmi: ManualDocument120 pages0 1 2 3 4 5 6 Simatic Hmi: Manualyukaokto2No ratings yet

- 0 1 2 3 4 5 6 Simatic Hmi: ManualDocument120 pages0 1 2 3 4 5 6 Simatic Hmi: Manualyukaokto2No ratings yet

- PLC or DCS PDFDocument12 pagesPLC or DCS PDFsafvanshaikhNo ratings yet

- Reguleau GBDocument2 pagesReguleau GBAmmar IshaquiNo ratings yet

- "Practical Projects of PLC-based Process Control System From The View Points of Environmental Countermeasure" Series 1: Now, Why PLC-based Process Control System?Document8 pages"Practical Projects of PLC-based Process Control System From The View Points of Environmental Countermeasure" Series 1: Now, Why PLC-based Process Control System?trc_bsnlNo ratings yet

- NIST Guide To Supervisory and Data Acquisition-SCADA and Industrial Control Systems Security (2007)Document164 pagesNIST Guide To Supervisory and Data Acquisition-SCADA and Industrial Control Systems Security (2007)thomaswangkoroNo ratings yet

- KB Wincc v6 eDocument12 pagesKB Wincc v6 eMancamiaicuruNo ratings yet

- PLC L05Document21 pagesPLC L05mihai37No ratings yet

- KB Wincc v6 eDocument12 pagesKB Wincc v6 eMancamiaicuruNo ratings yet

- KB Wincc 62 News enDocument14 pagesKB Wincc 62 News enAmmar IshaquiNo ratings yet

- Hmi Wincc v7 0 Information System en-USDocument10 pagesHmi Wincc v7 0 Information System en-USAmmar IshaquiNo ratings yet

- KB Wincc 62 News enDocument14 pagesKB Wincc 62 News enAmmar IshaquiNo ratings yet

- Doconweb PDF Sinumerik Sinamics 04 2010 e S7300re2Document190 pagesDoconweb PDF Sinumerik Sinamics 04 2010 e S7300re2Cảnh ManuNo ratings yet

- Howto Wincc v6 IngearopcDocument21 pagesHowto Wincc v6 IngearopcAmmar IshaquiNo ratings yet

- Hmi Wincc v6 2 Prodis Download Information Systems enDocument4 pagesHmi Wincc v6 2 Prodis Download Information Systems enAmmar IshaquiNo ratings yet

- Manual de WinCCDocument420 pagesManual de WinCCdanielrs_1980No ratings yet

- Hmi Wincc v7 0 Information System en-USDocument10 pagesHmi Wincc v7 0 Information System en-USAmmar IshaquiNo ratings yet

- HMIi Wincc v6 2 Getting Started enDocument120 pagesHMIi Wincc v6 2 Getting Started enHery100% (1)

- Continuous IndustriesDocument3 pagesContinuous IndustriesjithmavelyNo ratings yet

- WinCC Configuration Manual Vol 1Document320 pagesWinCC Configuration Manual Vol 1andtibNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Memories in Computers-Part 1: Dr. William R. Huber, P.EDocument55 pagesMemories in Computers-Part 1: Dr. William R. Huber, P.EdexterNo ratings yet

- Understanding digital literacy and technology fundamentalsDocument54 pagesUnderstanding digital literacy and technology fundamentalsGabriel Anton de LeonNo ratings yet

- Cache OrganizationDocument27 pagesCache OrganizationAbhishek karwalNo ratings yet

- 8085 and 8086 Memory Interface - FormatDocument45 pages8085 and 8086 Memory Interface - FormatAnime LegacyNo ratings yet

- List of Computer Abbreviations and Acronyms PDF: Abbreviation Stands ForDocument8 pagesList of Computer Abbreviations and Acronyms PDF: Abbreviation Stands Forhappyproof100% (1)

- UHFReader18 Demo Software User's Guidev2.1Document18 pagesUHFReader18 Demo Software User's Guidev2.1Jack WyhNo ratings yet

- LAB3.2.2-Memory Page Replacement - IndividualDocument7 pagesLAB3.2.2-Memory Page Replacement - Individualkhanhtlh.22itbNo ratings yet

- Heaps About HeapsDocument66 pagesHeaps About HeapsFilipe Xavier MinormonifNo ratings yet

- Zynq 7020Document4 pagesZynq 7020NGUYỄN HOÀNG LINHNo ratings yet

- C2000™ CPU Memory Built-In Self-Test: Application ReportDocument25 pagesC2000™ CPU Memory Built-In Self-Test: Application ReportLingaraju ChNo ratings yet

- Information AgeDocument11 pagesInformation AgevalicuinfoNo ratings yet

- Pg150 Ultrascale Memory IpDocument528 pagesPg150 Ultrascale Memory IpMohammed Nawaz ShaikNo ratings yet

- CS - Assignment 5 (RAM)Document2 pagesCS - Assignment 5 (RAM)Yajaira Lilledeshan De LeonNo ratings yet

- Cache (Computing)Document12 pagesCache (Computing)chahoubNo ratings yet

- BSIT 1st Semester Paper 2Document5 pagesBSIT 1st Semester Paper 2Asif SyedNo ratings yet

- Ds1922E Ibutton High-Temperature Logger With 8Kb Datalog MemoryDocument44 pagesDs1922E Ibutton High-Temperature Logger With 8Kb Datalog MemorylizarazojavierNo ratings yet

- RTS Book Notes for Real-Time SystemsDocument81 pagesRTS Book Notes for Real-Time SystemsKusuma P ChandrashekharNo ratings yet

- Institute of Information Technology University of DhakaDocument31 pagesInstitute of Information Technology University of Dhakaali marufNo ratings yet

- OS Concepts Chapter 1 MCQsDocument15 pagesOS Concepts Chapter 1 MCQsAyMan Omer100% (2)

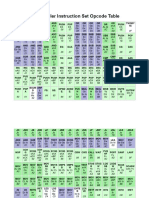

- Intel x86 Assembler Instruction Set Opcode TableDocument9 pagesIntel x86 Assembler Instruction Set Opcode TableMariaKristinaMarasiganLevisteNo ratings yet

- ISA System ArchitectureDocument521 pagesISA System Architecturecdrbc100% (1)

- Ch03-Virtual Memory Memory ManagementDocument74 pagesCh03-Virtual Memory Memory Managementlheyha1986No ratings yet

- Memory Management Unit 5Document58 pagesMemory Management Unit 5Nishant NalawadeNo ratings yet

- KVR32S22S8/16: Memory Module Specifi CationsDocument2 pagesKVR32S22S8/16: Memory Module Specifi CationsJefry Gutiérrez CelisNo ratings yet

- CS604 - Operating SystemsDocument11 pagesCS604 - Operating SystemsAsadNo ratings yet

- DRAM Circuit and Architecture Basics: Terminology Access Protocol ArchitectureDocument32 pagesDRAM Circuit and Architecture Basics: Terminology Access Protocol ArchitecturepnrgoudNo ratings yet

- Mask MotorolaDocument54 pagesMask Motorolazoki100% (2)

- COA question bank on computer organization and architectureDocument10 pagesCOA question bank on computer organization and architectureVenkat RamNo ratings yet

- Question Bank MPDocument5 pagesQuestion Bank MPER_GIRRAJNo ratings yet